@ -триггер (его варианты)

Иллюстрации

Показать всеРеферат

1. D-ТРИГГЕР, содержащий четыре транзистора и четыре резистора , тактовый вход D -триггера соединен с эмиттером первого транзистора , база которого соединена с шиной питания через первый резистор, а коллектор соединен с базой второго транзистора, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с тактовым входом Э -триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающийс я тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него введен пятый транзистор, коллектор и эмиттер которого соединены соответственно с базой третьего тр;анзистора и коллектором четвертого транзистора, а база соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с D -входом D-триггера, эмиттер и база четвертого транзистора соединены соответственно .с общей шиной и с коллектором третьего транзистора, а коллектор - с выходом Э -триггера. 2.О -триггер, содержащий четыре транзистора и четыре резистора,Dвход D -триггера соединен с первым эмиттером первого транзистора, база которого соединена с шиной питания через первый резистор, коллектор с .базой второго транзистора, коллекс тор которого соединен с шиной пита ния через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с вторьм эмиттером первого транзистора и тактовым входом D -триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающийся тем, что, с целью уменьшения потребляемой мощ00 ности и увеличения быстродействия,ое бд в него введен пятый транзистор,коллектор и эмиттер которого соединены соответственно с базой третьего транзистора и коллектором четвертого транзистора, база пятого транзистора соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с общей шиной, эмиттер и база четвертого транзистора соединены соответственно с общей шиной и с коллектором второго транзистора, а коллектор с выходом -триггера.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„> 188861 (5l)4 Н 03 К 3/286

ОПИСАНИЕ ИЗОБРЕТЕНИ

Н ABTOPCKOIVIV СВИДЕТЕЛЬСТВУ

ЗСЕ:ОЮЗА 1

Й4,.;

ТЕЛЛЬ„.

МИаОХаа

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3747252/24-21 (22) 19.04.84 (46) 30.10.85. Бюл. N 40 (72) А.П.Панфилов, А.Н.Молев, Ю.И.Савотин и И.И.Шагурин (53) 621.375 (088.8) (56) Апексеенко А.Г., Шагурин И.И.

Микросхемотехника. М.: Радио и связь, 1982,. с. 138.

Березенко А.И., Корягин Л.Н., Назарьян А.P. Микропроцессорные комплекты повышенного быстродействия. М.: Радио и связь, 198 1, с.69, рис.39. (54) (57) 1. Э-ТРИГГЕР, содержащий . четыре транзистора и четыре резистора, тактовый вход I) -триггера соединен с эмиттером первого транзистора, база которого соединена с шиной литания через первый резистор, а коллектор соединен с базой второго транзистора, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с тактовым входом 3 -триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, о т л и ч а ю щ и й— с я тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия, в него введен пятый транзистор, коллектор и эмиттер которого соединены соответственно с базой третьего транзистора и коллектором четвертого транзистора, а база соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с .D -входом

2 -триггера, эмиттер и база четвертого транзистора соединены соответственно.с общей шиной и с коллектором третьего транзистора, а коллектор — с выходом Э -триггера.

2. D -триггер, содержащий четыре транзистора и четыре резистора, З— вход D -триггера соединен с первым эмиттером первого транзистора, база которого соединена с шиной питания через первый резистор, коллекторс .базой второго транзистора, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора, эмиттер которого соединен с вторым эмиттером первого транзистора и тактовым входом 2 --триггера, коллектор четвертого транзистора соединен через третий резистор с шиной питания, отличающийся тем, что, с целью уменьшения потребляемой мощности и увеличения быстродействия,. в него введен пятый транзистор,коллектор и эмиттер которого соединены соответственно с базой третьего транзистора и коллектором четвертого транзистора, база пятого транзистора соединена через четвертый резистор с шиной питания, эмиттер второго транзистора соединен с общей шиной, эмиттер и база четвертого транзистора соединены соответственно с общей шиной и с коллектором второго транзистора, а коллектор— с выходом З -триггера.

1188861

Изобретение относится к импульсной технике и предназначено для использования в интегральных логических цифровых микросхемах.

Цель изобретения — уменьшение потребляемой мощности и увеличение быстродействия путем уменьшения напряжейия питания и уменьшения логического перехода.

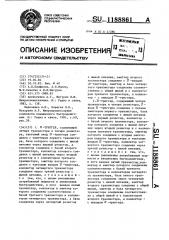

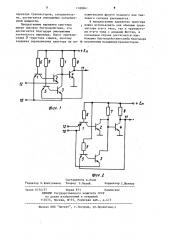

На фиг. 1 изображена принципиальная электрическая схема 2 -триггера, первый вариант; на фиг. 2 — то же, второй вариант.

Первый вариант 3 -триггера (фиг.1) содержит пять транзисторов 1-5 и четыре резистора 6-9, тактовый вход

10 триггера соединен с эмиттером первого транзистора i база которого соединена с шиной питания через первый резистор 6, коллектор первого транзистора 1 соединен с базой второго транзистора 2, коллектор которого соединен с шиной питания через второй резистор и с коллектором третьего транзистора 3, эмиттер которого соединен с тактовым входом

10 триггера, а коллектор четвертого транзистора 4 соединен через третий резистор 8 с шиной питания, коллектор и эмиттер пятого транзистора 5 ЗО соединены соответственно с базой третьего транзистора 3 и коллектором четвертого транзистора 4 и с выходом

11 триггера, а база соединена через четвертый резистор с шиной питания, З эмиттер второго транзистора 2 соединен с > -входом 12 триггера, а эмиттер и база четвертого транзистора 4 соединены соответственно с общей шиной и с коллектором третьего тран- 4р зистора 3.

Второй вариант D --триггера (фиг ° 2) содержит пять транзисторов

1-5, четыре резистора 6-9, Э -вход

12 соединен с первым эмиттером нер- 45 вого транзистора, база которого соединена с шиной питания через первый резистор 6, коллектор первого транзистора 1 соединен с базой второго транзистора 2, коллектор которого щ соединен с шиной питания через второй резистор 7 и с коллектором третьего транзистора 3, эмиттер которого соединен со вторым эмиттером первого транзистора 1 и тактовым вхо- 55 дом 10 Ý -триггера, а коллектор четвертого транзистора 4 соединен через третий резистор 8 с шиной питания, коллектор и эмиттер пятого транзистора 5 соединены соответственно с базой третьего транзистора

3 и коллектором четвертого транзистора 4, который соединен с выходом

11 Ю -триггера, база пятого транзистора 5 соединена через четвертый резистор 9 с шиной питания, эмиттер второго транзистора 2 соединен с общей шиной, которая соединена с эмиттером четвертого транзистора 4, база которого соединена с коллектором второго транзистора 2.

Первый вариант Д) -триггера (фиг.1) работает следующим образом.

Предположим,. что на тактовый вход 10 подано напряжение лог."1".

Если на входе 12 триггера .установлен потенциал лог. "О", то транзистор 1 находится в инверсном режиме и его ток коллектора втекает в базу транзистора 2 и является достаточ-. ным для насыщения транзистора 2, потенциал на коллекторе которого равен сумме остаточного напряжения на коллекторе насыщенного транзистора и уровня лог. "0". Таким образом,потенциал на базе транзистора 4 недостаточен для его отпирания, поэтому на выходе 11 триггера устанавливается потенциал лог."1". Потенциал лог.

"1" со входа 10,тактового сигнала поступает также и на эмиттер транзистора 3, поэтому независимо от потенциала на эмиттере транзистора 5,ток коллектора транзистора 3 равен нулю.

Если на вход 12 триггера подается потенциал лог."1" транзистор 2 отключается и потенциал íà его коллекторе увеличивается до уровня отпирания эмиттерного перехода транзистора 4. Транзистор 4 включается и переходит в насыщение, при этом на выходе триггера потенциал уменьшается до уровня лог."0". После этого транзистор 5 также переходит в насыщение, однако состояние транзистора

3 не меняется.

Таким образом, при удержании потенциала лог."1" на тактовом входе 10 на выход 11 триггера передается инверсия входного сигнала триггера.

Пусть на тактовый вход 10 подано напряжение, тогда транзистор 1 насыщен, и независимо от величины входного сигнала на эмчттере транзистора

2 на базе этого транзистора сохранядля удержания транзистора 2 во включенном состоянии, поэтому он выключается и потенциал на его коллекторе увеличивается до напряжения отпирания эмиттерного перехода транзистора 4. Транзистор 4 включается и переходит в насьпцение, при этом на выходе 11 триггера потенциал уменьшается до уровня лог."0". После этого транзистор 5 также переходит в насьпцение, однако состояние транзистора 3 не меняется.

Таким образом, при удержании потенциала лог."1" на тактовом входе

15 10 потенциал на выходе 11 триггера повторяет потенциал на входе 12 триггера.

° Пусть на тактовый вход 10 подано напряжение, тогда независимо от входного сигнала на втором эмиттере транзистора 1 на коллекторе этого транзистора сохраняется низкий потенци ал, недостаточный для отпирания транзистора 2, поэтому коллекторный

25 ток транзистора 2 равен нулю. Если потенциал на выходе триггера равен лог."1", то транзистор 5 работает в инверсном режиме, и в базу транзистора 3 втекает ток резистора 9, достаточный для насьпцения транзистора

3. На базе транзистора 4 устанавливается потенциал, недостаточный для отпирания транзистора 4, поэтому на выходе 11 триггера сохраняется по35 тенциал лог. 1 . Если же на выходе

11 триггера было напряжение лог."0", то транзистор 5 насьпцается, потенциал на его коллекторе снижается до ,величины, недостаточной для того, 40 чтобы транзистор 3 остался в режиме насыщения, поэтому потенциал на коллекторе транзистора 3 возрастет до уровня, достаточного для удержания транзистора 4 в насьпценном состоянии, 45 при этом на выходе триггера сохраняется потенциал лог."0", следовательно, при удержании потенциала лог.

11, lI

О на тактовом входе триггер хранит записанную информацию.

50 Таким образом, устройство, схема которого изображена на фиг. 2, также функционирует как Ю -триггер, тактируемый Уровнем лог."1".

Предлагаемые варианты триггера

55 работают при низких напряжениях источника питания вплоть до величины

U, + Ц„, где Um U o- падение напряжения на открытом диоде и эмиттерном

3 11888б1 4 ется низкий потенциал, недостаточный для отпирания транзистора 2, поэтому коллекторный ток транзистора

2 равен нулю. Если потенциал на выходе 11 триггера равен лог."1", то транзистор 5 работает в инверсном режиме, и в базу транзистора 3 втекает ток резистора 9, достаточный для насьпцения транзистора 3. На базе транзистора 4 устанавливается 10 потенциал, недостаточный для отпирания транзистора 4, поэтому на выходе 11 триггера сохраняется высокий потенциал . Если же на выходе

11 триггера было напряжение лог."0", то транзистор 5 насьпцается, потенциал на его коллекторе снижается и становится недостаточным для того, чтобы транзистор 3 остался в режиме насьпцения, поэтому потенциал на коллекторе транзистора 3 повьппается до уровня, достаточного для удержания . транзистора 4 в насыщенном состоянии, при этом на выходе триггера сохраняется потенциал лог."0", следовательно, при удержании потенциала лог."0" на тактовом входе триггер сохраняет ранее записанное. состояние.

Таким образом, устройство, схема которого изображена на фиг. 1, функционирует как 3 -триггер, тактируемый уровнем лог."1".

Второй вариант 2 -триггера (фиг.2) работает следующим образом.

Предположим, что на тактовый вход 10 подано напряжение лог."1".

Если на входе 12 триггера установлен потенциал лог."1", то транзистор 1 находится в инверсном режиме и его ток коллектора втекает в базу транзистора 2 и является достаточным для насьпцення транзистора 2, потенциал на коллекторе которого равен остаточному напряжению, которое недостаточно для насьпцения транзистора 4, поэтому на выходе 11 триггера устанавливается потенциал лог." 1".

Потенциал лог."1" со входа тактового сигнала поступает также и на эмиттер транзистора 3, поэтому независимо от потенциала на эмиттере транзистора 5 ток коллектора транзистора 3 ранен нулю.

Если на вход 12 триггера подается потенциал лог."0", транзистор 1 насыщается и на его коллекторе устанавливается потенциал, недостаточный

ll88861 р08 1

Составитель А.Янов

Редактор Н.Киштулинец Техред З.Палий, Корректор C.Øåêìàð

Заказ 6754/57 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.Ужгород, ул.Проектная,4 переходе транзисторов, следовательно, достигается уменьшение потребляемой мощности.

Предлагаемые варианты триггера имеют высокое быстродействие, что достигается благодаря уменьшению логического перепада. Порог переключения Ю -триггера снижен, поэтому задержка переключения триггера на положительном фронте входного или тактового сигнала уменьшается.

В предлагаемых вариантах триггера можно испольэовать как обычные транзисторы п-р-и типа, так и транзисторы и-р-п типа с диодами Шоттки, в последнем случае достигается наибольшее быстродействие схемы благодаря

1О исключению насышениятранзисторов.