Устройство обнаружения факсимильных фазовых импульсов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ОБНАРУЖЕНИЯ ФАКСИМИЛЬНЫХ ФАЗОВЫХ ИМПУЛЬСОВ, содержащее накопитель, формирователь импульсов сброса и первый триггер, установочньй вход которого соединен с шиной сигнала начальной установки, а выход формирователя импульсов сброса подключен к установочному входу накопителя , отличающееся тем, что, с целью повышения достоверности обнаружения фазовых импульсов, в него введены второй триггер, первый и второй элементы И и коммутатор импульсов , первый и второй выходы которого подключены соответственно к счетному, входу первого триггера и к входу формирователя импульсов сброса, первый и второй управляюпще входы коммутатора импульсов соединены соответственно с первым и вторым выходами первого триггера, первый информационный вход которого является входом фазовых импульсов, а второй информационный вход соединен с выходом второго элемента И первый вход которого соединен с первым выходом первого триггера, при этом выходы накопителя 5S соединены с соответствующими входами первого элемента И, выход которого (Л подключен к второму входу второго элемента Инк счетному входу второго триггера, выход которого подключен к информационному входу первого триггера, а объединенные установочный и информационный входы второго триггера соединены с первым выходом накопителя. 00 00 со о оо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (! 9) (I! ) (()4 H 04 N 1/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY. СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3740110/24-09 (22) 08. 05. 84 (46) 30. 10.85. Бюл. N - 40 (72) Ю. Г. Ильин (53) 621 ° 397 (088. 8) (56) Патент Японии N - 53-1089, кл. Н 04 N 1/36, 1973 °

Аппараты факсимильные Ф5СБ-M-1-71 и Ф5СБ-М3-71. Техническое описание.

Минск, 1979. (54) (57) УСТРОЙСТВО ОБНАРУ((ЕНИЯ ФАКСИМИЛЬНЫХ ФАЗОВЫХ ИМПУЛЬСОВ, содержащее накопитель, формирователь импульсов сброса и первый триггер, установочный вход которого соединен с шиной сигнала начальной установки, а выход формирователя импульсов сброса подключен к установочному входу накопителя, отличающееся тем, что, с целью повышения достоверности обнаружения фазовых импульсов, в него введены второй триггер, первый и второй элементы И и коммутатор импульсов, первый и второй выходы которого подключены соответственно к счетному. входу первого триггера и к входу формирователя импульсов сброса, первый и второй управляющие входы коммутатора импульсов соединены соответственно с первым и вторым выходами первого триггера, первый информационный вход которого является входом фазовых импульсов, а второй информационный вход соединен с выходом второго элемента И, первый вход которого соединен с первым выходом первого триггера, при этом выходы накопителя соединены с соответствующими входами первого элемента И, выход которого подключен к второму входу второго элемента И и к счетному входу второго триггера, выход которого подключен к информационному входу первого триггера, а объединенные установочный и информационный входы второго триггера соединены с первым выходом накопителя.

1188903

Изобретение относится к технике телевидения и может быть использовано в системах факсимильной передачи изображений.

Цель изобретения — повышение достоверности обнаружения фазовых импульсов .

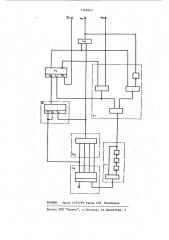

На чертеже изображена структурная электрическая схема устройства обнаружения факсимильных фазовых импульсов.

Устройство обнаружения Факсимильных фазовых импульсов содержит формирователь 1 импульсов сброса, накопитель 2, первый 3 и второй 4 триггеры, первый 5 и второй б элементы И, коммутатор 7 импульсов, входную 8, вьгходную 9 и установочную 10 шины.

Устройство работает следующим образом.

После снятия сигнала начальной установки с установочной шины 10 на выходной шине 9 присутствует логический "0". Это связано с подачей на вход второго элемента И 6 логического "0" с первого триггера 3.

Эта блокировка существует до срабатывания первого триггера 3. До этого времени с первого и второго выходов первого триггера 3 на управляющие входы коммутатора 7 поступают соответственно логический "Îн и логическая "1", разрешая прохождение через коммутатор 7 на формирователь 1 положительных импульсов с входной шины 8. Короткие положительные импульсы с формирователя 1 подаются на накопитель 2, устанавливая его в нулевое состояние, и начиная после окончания входного импульса отсчеты заново. Необходимая для отсчетов исходная частота (Е) подается на счетный вход накопителя 2.

Отсчеты интервалов времени с накопителя 2 поступают на первый элемент И 5, на выходе которог о формируется положительный импульс, у которого заднгпг

5 фронт несет информацию о предполагаемой фазе, и после положительного решения (срабатывания первого триггера 3) выдается в виде сфазированной последовательности опорных импульсов на выходную шину 9.

Пусть на входную шину 8 подается первый фазовый импульс. От его переднего Фронта начинает работать накопитель 2, выдавая необходимые интервалы времени. Пусть между двумя Фазовыми импульсами появляется помеха в виде короткого положительного импульса. От его переднего фронта счет сбрасывается и начинается снова. К моменту появления действительного фазового импульса на вьгходе первого элемента И 5 опорный импульс не будет сформирован. При появлении помехи другого рода, когда часть фазового импульса уничтожена, на выходе первого элемента И 5 появляется опорный импульс, который подается на счетный вход

30 второго триггера 4, íà S- u D-входы которого подается сигнал с одного из выходов накопителя 2. В соответствии с логикой работы второго триггера 4 на его выходе имеется положительньпг импульс. Этот импульс подается на информационный вход первого триггера 3, на счетный вход которого подается опорный проверяемый импульс. с входной шины 8 через

40 коммутатор 7. Так как фазовый фронт приходящего на входную шину 8 Фазового импульса искажен (как отмечалось выше), то срабатывание первого триггера .3 не происходит.

1188903

ВНИИПИ Заказ 6751/59 Тираж 658 Подписное

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4