Формирователь частотно-манипулированных сигналов

Иллюстрации

Показать всеРеферат

ФОРМИРОВАТЕЛЬ ЧАСТОТНОМАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащий синтезатор сетки частот, первый , второй и третий выходы которого соединены соответственно с сигнальными входами первого, второго и третьего фазовращателей , коммутатор, первый, второй и третий сигнальные входы которого соединены с выходами соответственно первого, второго и третьего фазовращателей, и блок питания , отличающийся гем, что, с целью уменьщения краевых искажений выходных сигналов , введены последовательно соединенные первый блок интегрирования, вход которого соединен с выходом первого фазовращателя, и первый блок выборки и хранения, последовательно соединенные второй блок интегрирования , вход которого соединен ,с выходом второго фазовращателя, и второй блок выборки и хранения, последовательно соединенные третий блокинтегрирования, вход которого соединен с выходом третьего фазовращателя, и третий блок выборки и хранения, четвертый, пятый и шестой блоки выборки и хранения, дополнительный коммутатор, первый, второй и третий сигнальные входы которого соединены соответственно с выходами первого, второго и третьего фазовращателей, первый, второй и третий триггеры, неинвертирующие выходы которых соединены соответственно с первым , вторым и третьим управляющими входами дополнительного коммутатора, последовательно соединенные фазовый детектор, первый вход которого соединен с выходом коммутатора, и переключатель, первый выход которого соединен с входом установки в «1 первого триггера, первым в.ходом установки в «О второго триггера и вторым входом установки в «О третьего триггера, второй выход соединен с вторь м входом установки в «О первого триггера, входом установки в «1 второго триггера и первым входом установки в «О третьего триггера , а третий выход переключателя соединен с входом установки в «О первого триггера , вторым входом установки в «О второго триггера и входом установки в «1 тре$3 тьего триггера, четвертый блок интегриро (Л вания, последовательно соединенные усилитель и широкополосный фильтр, а между выходом блока питания и входом питающего напряжения синтезатора сетки частот введен блок установки в «О, выход которого соединен с входом сброса первого, второго и третьего триггеров, с входами сброса первого, второго, третьего и четвертого блоков интегрирования и с входами сброса первого, второго, третьего, четвертого, со пятого и шестого блоков выборки и хранео ния, при этом первый, второй и третий фа4 зовращатели выполнены управляемыми, и их Од первые управляющие входы соединены соотto ветственно с выходами первого, второго и третьего блоков выборки и хранения, а вторые управляющие входы - соответственно с выходами четвертого, пятого и шестого блоков выборки и хранения, вход четвертого блока интегрирования и вход усилителя соединены с выходом дополнительного коммутатора и с вторым входом фазового детектора, сигнальные входы четвертого, пятого и щестого блоков выборки и хранения соединены с выходом четвертого блока интегрирования, управляющие входы первого и четвертого блоков выборки и хранение

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК уц4 Н 03 С 3/00...1 I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

М А ВТОРСМОМЪ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3584722/24-09 (22) 27.04.83 (46) 07.11.85. Бюл. № 41 (71) Донецкое отделение Института «Гипро-. углеавтоматизация» (72) Н. А. Чехлатый и А. М. Пирогов (53) 621.376.52 (088:8) (56) Бухвинер В. Е. и др. Дискретные схемы в фазовых системах радиосвязи.— М.:

Связь, 1969, с. 108 — 109.

Авторское свидетельство СССР № 383198, кл. Н 03 С 3/26, 1970. (54) (57) ФОРМИРОВАТЕЛЬ ЧАСТОТНОМАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащий синтезатор сетки частот, первый, второй и третий выходы которого соединены соответственно с сигнальными входами первого, второго и третьего фазовращателей, коммутатор, первый, второй и третий сигнальные входы которого соединены с выходами соответственно первого, второго и третьего фазовращателей, и блок питания, отличающийся тем, что, с целью уменьшения краевых искажений выходных сигналов, введены последовательно соединенные первый блок интегрирования, вход которого соединен с выходом первого фазовращателя, и первый блок выборки и хранения, последовательно соединенные второй блок интегрирования, вход которого соединен с выходом второго фазовращателя, и второй блок выборки и хранения, последовательно соединенные третий блок- интегрирования, вход которого соединен с выходом третьего фазовращателя, и третий блок выборки и хранения, четвертый, пятый и шестой блоки выборки и хранения, дополнительный коммутатор, первый, второй и третий сигнальные входы которого соединены соответственно с выходами первого, второго и третьего фазовращателей, первый, второй и третий триггеры, неинвертирующие выходы которых соединены соответственно с перÄÄSUÄÄ 1190462 А вым, вторым и третьим управляющими входам и дополнительного коммутатора, последовательно соединенные фазовый детектор, первый вход которого соединен с выходом коммутатора, и переключатель, первый выход которого соединен с входом установки в «1» первого триггера, первым входом установки в «О» второго триггера и вторым входом установки в «О» третьего триггера, второй выход соединен с вторым входом установки в «О» первого триггера, входом установки в «1» второго триггера и перBb1M входом установки в «О» третьего триггера, а третий выход переключателя соединен с входом установки в «О» первого триггера, вторым входом установки в «О» второго триггера и входом установки в «!» третьего триггера, четвертый блок интегрирования, последовательно соединенные усилитель и широкополосный фильтр, а между выходом блока питания и входом питающего напряжения синтезатора сетки частот введен блок установки в «О», выход которого соединен с входом сброса первого, второго и третьего триггеров, с входами сброса первого, второго. третьего и четвертого блоков интегрирования и с входами сброса первого, второго, третьего, четвертого, пятого и шестого блоков выборки и хранения, при этом первый, второй и третий фазовращатели выполнены управляемыми, и их первые управляющие входы соединены соответственно с выходами первого, второго и третьего блоков выборки и хранения, а вторые управляющие входы — соответственно с выходами четвертого, пятого и шестого блоков выборки и хранения, вход четвертого блока интегрирования и вход усилителя соединены с выходом дополнительного коммутатора и с вторым входом фазового детектора, сигнальные входы четвертого, пятого и шестого блоков выборки и хранения соединены с выходом четвертого блока интегрирования, управляющие входы первого и четвертого блоков выборки и хранениг

1190462 первый управляющий вход коммутатора и первый сигнальный вход переключателя соединены между собой и точка их соеди нения является первым входом манипулирующих сигналов, управляющие входы второго и пятого блоков выборки и хранения, второй управляющий вход коммутатора и второй сигнальный вход переключателя соединены между собой и точка их соеди1

Изобретение относится к радиотехнике и может использоваться в качестве формирователя частотно-манипулированных сигналов без разрыва фазы в частотно-времен- 20 ных системах телемеханики.

Цель изобретения — уменьшение краевых искажений выходных сигналов.

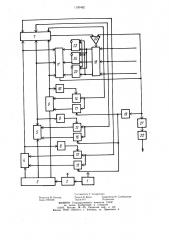

На чертеже представлена структурная электрическая схема предлагаемого фор25 мирователя частотно-манипулированных сигналов.

Предлагаемое устройство содержит блок

1 питания, блок 2 установки в нуль, синтезатор 3 сетки частот, первый 4, второй 5 и третий 6 управляемые фазоврашатели, коммутатор 7, первый Ь, второй 9 и третий 10 блоки интегрирования, дополнительный коммутатор 11, первый 12, второй 13, третий 14, четвертый 15, пятый 16, шестой 17 блоки выборки и хранения, переключатель 18, четвертый блок 19 интегрирования, фазовый 35 детектор 20, усилитель 21, широкополосный фильтр 22, первый 23, второй 24 и третий

25 триггеры.

Формирователь частотно-манипулированных сигналов работает следующим образом.

При включении блока 1 питания включается блок. 2 установки в нуль. Сигнал с выхода блока 2 установки в нуль устанавливает в исходное состояние блоки 8— !

О и 19 интегрирования, триггеры 23 — 25, 45 блоки 12 в 17 выборки и хранения и включает синтезатор 3 сетки частот. С первого, второго и третьего выходов синтезатора 3 сетки частот сигналы рабочей частоты (f— — F) (f+ F) и несущей частоты поступают соответственно на входы первого 4, второго 5

50 и третьего 6 управляемых фазовращателей и через них, соответственно, на первый, второй и третий входы коммутатора 7 и на блоки 8 — 10 интегрирования. В последних, которые могут быть выполнены в виде после- 55 довательно соединенных формирователя импульсов и интегрирующей цепи, формируются прямоугольные импульсы, длитель нения является вторым входом манипулирующих сигналов, управляющие входы третьего и шестого блоков выборки и хранения, третий управляющий вход коммутатора и третий сигнальный вход переключателя соединены между собой, и точка их соединения является третьим входом манипулирующих сигналов формирователя частотноманипулированных сигналов. ность которых равна периоду следования высокочастотных импульсов на их входах, и затем их длительность преобразуется в амплитуду. С выходов блоков 8 — 10 интегрирования сигналы поступают соответственно на входы блоков 12 — 14 выборки и хранения, которые совместно с блоками 15—

17 выборки и хранения производят выборку сигнала при наличии на их управляющем входе переднего фронта импульса на соответствующем входе манипулирующих сигналов.

Амплитуда сигнала на выходе блоков 8—

10 интегрирования и 19 в момент выборки определяет величину фазового рассогласования между высокочастотным сигналом, поступаюгцим на широкополосный фильтр 22 и выходным сигналом управляемых фазовращателей 4 — 6. В каждый момент времени два блока выборки и хранения, например, блоки 14 и 17 выборки и хранения находятся в режиме хранения, а остальные блоки выборки и хранения 13 и 16, 12 и 15— в ждущем режиме.

При поступлении манипулирующего сигнала на управляющие входы блоков 12 и 15 выборки и хранения на первый сигнальныйы и вход перекл юч ател я 18 и первый управляющий вход коммутатора 7, последний открывается и высокочастотный сигнал (f — F) поступает на первый вход фазового детектора 20, на второй вход которого поступает высокочастотный сигнал предыдущей посылки. Передним фронтом манипулирующего сигнала блоки 12 и 15 выборки и хранения производят выборку сигнала, поступающего с блоков 8 и 19 интегрирования. Сигнал с выхода блока 12 выборки и хранения поступает на первый управляющий вход управляемого фазовращателя 4, осуществляя при этом подстройку фазы высокочастотного сигнала в пределах от 0 до †3 в зависимости от уровня сигнала выборки, а сигнал с выхода блока 15 выборки и хранения поступает на второй управляющий вход управляемого фазовращателя 4, 1190462

3 осуществляя подстройку фазы в пределах от 0 до + 360 .

При равенстве фаз высокочастотных колебаний на выходе фазового детектора 20 появляется импульс, который поступает на управляющий вход переключателя 18. Импульс с соответствующего выхода последнего производит включение триггера 23 и выключения триггеров 24 и 25. Сигнал с неинвертирующего выхода триггера 23 поступает на первый управляющий вход дополнительного коммутатора 11, на выходе которого происходит смена посылки f — F. При этом блоки 12 и 15 выборки и хранения обеспечивают хранение сигналов на время формирования высокочастотной посылки

f — F. Выходной сигнал дополнительного коммутатора !1 поступает на блок 19 интегрирования и через усилитель 21 на широкополосный фильтр 22, на выходе которого выделяется синусоидальный сигнал.

В следующем такте при поступлении манипулирующего сигнала на управляющие входы блоков 13 и 16 (14 и 17) выборки и хранения, второй (третий) сигнальный вход переключателя 18 и второй (третий) управляющий вход коммутатора 7 последний открывается и высокочастотный сигнал f+

+F(f) поступает на первый вход фазового детектора 20, на второй вход которого пос тупает высокочастотный сигнал f = F. Передним фронтом манипулирующего сигнала в блоках 13 и 16 (14 и 17) выборки и хранения производится выборка сигнала, поступающего с блоков 9(10) и 19 интегри4 рования. Сигнал с выхода блока 14 (13) выборки и хранения поступает на первый управляющий вход управляемого фазовращателя 5(6), осуществляя установку фазы в

«О», а сигнал с выхода блока 17(16) выборки и хранения поступает на второй управляющий вход управляемого фазовращателя

5 и 6, осуществляя подстройку фазы высокочастотного сигнала f — F.

Таким образом осуществляется отслежи10 вание фазы высокочастотного сигнала предыдущей посылки. При равенстве фаз высокочастотных сигналов предыдущей посылки

f — F и последующей f+F(f) на выходе фазового детектора 20 формируется импульс, который поступает на управляющий вход переключателя 18. Импульс с его соответствующего выхода производит включение триггера 24 (25) и выключение триггеров

23 и 25 (24). Сигнал с неинвертирующего выхода триггера 24 поступает на соответст20 вующий gïpàâëÿþøèé вход дополнительного коммутатора 11, на выходе которого происходит смена посылки на f+F(f). При этом блоки 13 и 16 (14 и 17) выборки хранения обеспечивают хранение сигналов на

25 время формирования Высокоч стотной посылки f+ F(f) . Выходной си гнал допол ни тельного коммутатора 11 поступает через усилитель 21 на широкополосный фильтр 22 и далее синусоидальный сигнал, в котором без разрыва фазы происходит переход с одgp ной частоты на другую, поступает на выход формирователя частотно-манипулированных сигналов.

1190462

Редактор М. Бланар

Заказ 7000/56

Составитель Г. Захарченко

Техред И. Верес Корректор М. Самборская

Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», г. Ужгород, ул. Проектная, 4