Цифровая линия задержки

Иллюстрации

Показать всеРеферат

ЦИФРОВАЯ ЛИНИЯ ЗАДЕРЖКИ , содержащая первое запоминающее устройство, формирователь тактовых сигналов , первый выход которого соединен с первым входом первого формирователя адресных сигналов, адресные выходы которого соединены с адресными входами первого запоминающего устройства, отличающаяся тем, что, с целью повыщения разрещающей способности линии задержки и уменьшения потребляемой мощности, в него введены второй формирователь адресных сигналов , второе запоминающее устройство. адресные входы которого соединены с адресными выходами второго формирователя адресных сигналов, первый вход которого объединен с первым входом первого формирователя адресных сигналов, элемент задержки на один такт первый и второй входы которого соединены соответственно с первым и вторым выходами формирователя тактовых сигналов и с первым и вторым входами делителя на два, один выход которого соединен с вторым входом первого формирователя адресных сигналов и с управляющим входом первого запоминающего устройства, а другой - с вторым входом второго формирователя адресных сигналов и с управляющим входом второго запоминающего устС ройства, выход элемента задержки на один такт является выходом устройства, а его (Л третий вход подключен к объединенным выходами первого и второго запоминающих устройств, объединенные информационные входы которых являются входом цифровой линии задержки. со о ;с со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1190499 д1)4 НОЗ К5 13

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3653726/24-21 (22) 18. 10.83 (46) 07.11.85. Бюл. 41 (72) В. А. Максимов и Н. П. Корнышев (53) 621.374 (088.8) (56) Дубицкий В. И. и Поддубный Е. В.

Цифровые линии задержки видеосигнала на интегральных микросхемах «памяти». Техника, кино и телевидение, № 9, 1980, с. 34 — 36. (54) (57) ЦИФРОВАЯ ЛИНИЯ ЗАДЕРЖКИ, содержащая первое запоминающее устройство, формирователь тактовых сигналов, первый выход которого соединен с первым входом первого формирователя адресных сигналов, адресные выходы которого соединены с адресными входами первого запоминающего устройства, отличающаяся тем, что, с целью повышения разрешающей способности линии задержки и уменьшения потребляемой мощности, в него введены второй формирователь адресных сигналов, второе запоминающее устройство, адресные входы которого соединены с адресными выходами второго формирователя адресных сигналов, первый вход которого объединен с первым входом первого формирователя адресных сигналов, элемент задержки на один такт, первый и второй входы которого соединены соответственно с первым и вторым выходами формирователя тактовых сигналов и с первым и вторым входами делителя на два, один выход которого соединен с вторым входом первого формирователя адресных сигналов и с управляющим входом первого запоминающего устройства, а другой — с вторым входом второго формирователя адресных сигналов и с управляющим входом второго запоминающего устройства, выход элемента задержки на один такт является выходом устройства, а его третий вход подключен к объединенным выходами первого и второго запоминающих устройств, объединенные информационные входы которых являются входом цифровой линии задержки.

1190499

Составитель А. Титов

Редактор А. Сабо Техред И. Верес Корректор М. Максимишинец

Заказ 7002/58 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Изобретение относится к импульсной технике и может быть использовано для обработки видеосигнала, при построении аппаратуры телевизионной автоматики, в частности при построении счетчиков количества объектов, анализаторов изображений объектов.

Цель изобретения — повышение разрешающей способности линии задержки за счет повышения тактовой частоты и уменьшение потребляемой мощности.

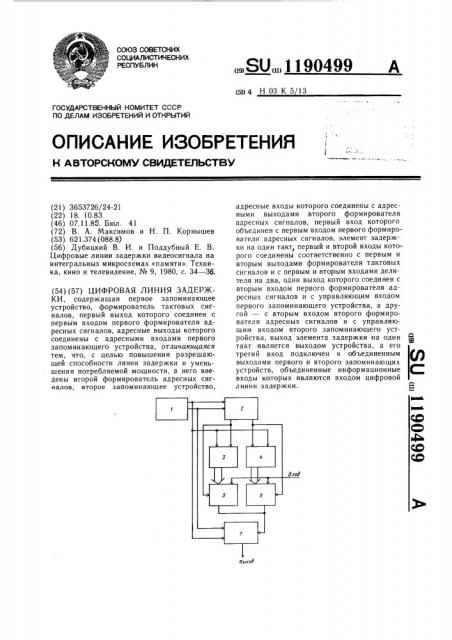

На чертеже приведена структурная схема цифровой линии задержки.

Цифровая линия задержки содержит формирователь 1 тактовых сигналов, первый выход которого соединен с первыми входами делителя 2 на два, первого 3 и второго 4 формирователя адресных сигналов, адресные выходы которых подключены соответственно к адресным входам первого

5 и второго 6 запоминающих устройств, управляюшие входы которых соединены соответственно с вторыми входами формирователей 3 и 4 сигналов и соответственно с первым и вторым выходами делителя на два.

Об.ьединенные информационные входы запоминающих устройств 5 и 6 являются входом устройства задержки, а их объединенные выходы подключены к третьему входу элемента 7 задержки на один такт, выход которого является выходом устройства, а первый и второй входы которого подключены соответственно к первому выходу формирователя 1 тактовых сигналов и к второму выходу формирователя 1 тактовых сигналов, соединенному с вторым входом делителя 2 на два.

Формирователь 1 тактовых сигналов содержит, например, генератор тактовых импульсов и источник синхронизирующих импульсов, первый и второй выходы его являются соответственно выходами синхронизирующего и тестового импульсов. Делитель 2 на два может быть выполнен в виде счетного триггера, его первый вход установочный, а второй — счетный, формирователи 3 и 4 сигналов могут быть выполнены в виде счетчиков, их первые входы-установочные, а вторые — счетные, запоминающие устройства 5 и 6 являются типовыми элементами оперативной памяти. В качестве элемента задержки 7 на один такт может быть использован, например, Д-триггер первый его вход установочный, второй— тактовый, а третий — информационный.

Устройство работает следующим образом.

Во время действия синхронизируюшего импульса, начало и конец которого синхронизированы тактовой частотой формирователя 1 тактовых сигналов, формирователи адресных сигналов 3 и 4, делитель 2 на два, элемент 7 задержки на один такт устанавливаются в исходное состояние, при котором формирователи 3 и 4 адресных сигналов устанавливаются в нулевое состояние, а делитель 2 на два в состояние, при котором, например, запоминаюшее устройство 5 будет находиться в режиме «запись», а запоминающее устройство 6 — в режиме «считывание». Элемент 7 задержки на один такт при этом вырабатывает сигнал уровня «О», независимо от информации, считываемой с первой ячейки запоминающего усройства

6. С приходом на счетный вход делителя на два первого тактового сигнала прямого хода строчной развертки, запоминающие устройства 5 и 6 изменяют режимы работы, а к содержимому формирователя 3 адресных сигналов прибавится «1»

В результате в соответствии с установленным адресом в запоминающем устройстве 5 производится считывание информации с второй ячейки памяти, а в запоминающем устройстве 6 — запись в первую ячейку памяти в соответствии с уровнем сигнала на входной шине. На выходе элемента 7 задержки на один так выдается информация, считанная с первой ячейки памяти запоминающего устройства 6 во время действия синхронизирующего импульса, которая запишется на элемент 7 задержки на один такт по первому тактовому сигналу прямого хода строчной развертки.

По началу второго тактового сигнала формирователь 4 адресных сигналов изменяет свое начальное состояние на «1», а запоминающее устройство 5 переходит в режим считывания с второй ячейки памяти.

Элемент 7 задержки на один такт при этом выдает значение информации, считанной с второй ячейки памяти запоминающего устройства 5. Далее происходит последовательное считывание с последующих ячеек памяти. С приходом следующего синхронизирующего импульса устройство возвращается в указанное состояние. Далее цикл работы повторяется.