Пороговый логический элемент (его варианты)

Иллюстрации

Показать всеРеферат

1. Пороговый логический элемент, выполненный на магнитном токовом переключателе , содержащем два микросердечника, два диода, две встречно включенные обмотки считывания, которые выполнены соответственно на первом, втором микросердечниках , начала обмоток считывания соединены с входной шиной считывания, концы первой и второй обмоток считывания соединены соответственно с анодами первого и второго диодов, катоды которых соединены соответственно с первой, второй выходными шинами считывания, п пар шин записи прямого и инверсного значений аргумента, п выходных шин записи, п пар обмоток записи прямого и инверсного значений аргумента, в каждой из которых обмотки записи прямого и инверсного значений аргумента включены встречно и выполнены на первом и втором микросердечниках, числа витков обмоток записи аргументов соответствуют весам аргументов пороговой функции, каждая пара шин записи прямого и инверсного значений аргумента соединена соответственно с началами обмоток записи прямого и инверсного значений аргумента соответствующей пары обмоток записи прямого и инверсного значений аргумента, в которой концы обмоток записи прямого и инверсного значений аргумента объединены, в n-k парах, где , обмоток записи прямого и инверсного значений аргумента концы обмоток записи прямого и инверсного значений аргумента соединены с соответствующей выходной щиной записи, отличающийся тем, что, с целью повышения надежности, в k парах шин записи прямого и инверсного значений аргумента шины записи прямого значения аргумента соединены с соответствующими выходными шинами записи, причем суммарное число витков обмоток записи прямых значений аргумента в k парах обмоток записи прямого и инверсного значений аргумента соответствует весу порога пороговой функции .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5D 4 Н 03 19 16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

Фиг. /

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3669894/24-21 (22) 29.11.83 (46) 07.11.85. Бюл. № 41 (72) Ю. И. Крылов (53) 621.374.32 (088.8) (56) Авторское свидетельство СССР № 207473, кл. Н 03 К 19/16, 1966.

Авторское свидетельство СССР № 244393, кл. Н 03 К 19/16, 1968. (54) ПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ (ЕГО ВАРИАНТЫ). (57) 1. Пороговый логический элемент, выполненный на магнитном токовом переключателе, содержащем два микросердечника, два диода, две встречно включенные обмотки считывания, которые выполнены соответственно на первом, втором микросердечниках, начала обмоток считывания соединены с входной шиной считывания, концы первой и второй обмоток считывания соединены соответственно с анодами первого и второго диодов, катоды которых соединены соответственно с первой, второй выходными шинами считывания, и пар шин записи прямого и инверсного значений аргумента, и выходных шин записи, и пар обмоток записи прямого и инверсного значений аргумента, в каждой из которых обмотки записи прямого

/=!

„„SUÄÄ 1190517 A и инверсного значений аргумента включены встречно и выполнены на первом и втором микросердечниках, числа витков обмоток записи аргументов соответствуют весам аргументов пороговой функции, каждая пара шин записи прямого и инверсного значений аргумента соединена соответственно с началами обмоток записи прямого и инверсного значений аргумента соответствующей пары обмоток записи прямого и инверсного значений аргумента, в которой концы обмоток записи прямого и инверсного значений аргумента объединены, в и-k парах, где

k(n, обмоток записи прямого и инверсного значений аргумента концы обмоток записи прямого и инверсного значений аргумента соединены с соответствующей выходной шиной записи, отличающийся тем, что, с целью повышения надежности, в k парах шин записи прямого и инверсного значений аргумента шины записи прямого значения аргумента соединены с соответствующими выходными шинами записи, причем суммарное число витков обмоток записи прямых значений аргумента в k парах обмоток записи прямого и инверсного значений аргумента соответствует весу порога пороговой функции.

1190517

2. Пороговый логический элемент, выполненный на магнитном токовом переключателе, содержащем два микросердечника, два диода, две встречно включенные обмотки считывания, которые выполнены соответственно на первом, втором микросердечниках, начала обмоток считывания соединены с входной шиной считывания, концы первой и второй обмоток считывания соединены соответственно с анодом первого и второго диодов, катоды которых соединены соответственно с первой, второй выходными шинами считывания, п выходных шин записи, п пар шин записи прямого и инверсного значений аргумента, обмотку начальной установки, выполненную на первом, втором микросердечниках, и п обмоток записи прямого значения аргумента, каждая из которых выполнена на первом, втором микросердечниках, 1

Изобретение относится к автоматике и вычислительной технике и может найти применение в реализации технических средств в этих областях.

Целью изобретения является повышение надежности путем совмещения функции пороговой обмотки с функцией обмоток записи аргуменгов, т.е. изменения соотношения числа витков обмоток записи прямого и инверсного значений аргумента при сохранении общего числа витков обмоток записи прямого и инверсного значений аргумента.

Исключение пороговой обмотки уменьшает общее число витков обмоток при заданном конструктивном размере, что позволяет увеличить число аргументов (число обмоток) или число витков в обмотках аргументов.

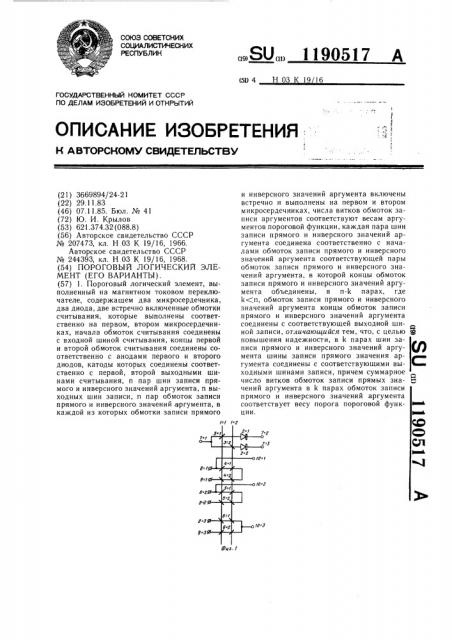

На фиг.1 приведена схема порогового логического элемента с обмотками записи прямого и инверсного значений каждого аргумента; на фиг.2 — схема порогового логического элемента с обмоткой записи только прямого значения каждого аргумента.

Логический элемент (фиг.1) содержит микросердечники 1=1 и 1=2, диоды 2=1 и 2=2, обмотки 3=1 и 3=2 считывания, обмотку 4=1 записи прямого значения первого аргумента, обмотку 4=2 записи инверсного значения первого аргумента, обмотку

5=1 записи прямого значения второго аргумента, обмотку 5=2 записи инверсного значения второго аргумента, обмотки 6=1 и 6=2 записи соответственно прямого и инверсного значений третьего аргумента, входную шину 7=1 считывания, выходные шинь1 7=2 и 7=3 считывания, шины

30 числа витков обмоток записи прямого значения аргумента соответствуют весам аргументов пороговой функции, и шин записи прямого значения аргумента соединены соответственно с началом п обмоток записи прямого значения аргумента, концы которых соединены соответственно с и шинами записи инверсных значений аргумента, концы п-k, где k(n, обмоток записи прямого значения аргумента соединены соответственно с и-k выходными шинами записи, отличающийся тем, что, с целью повышения надежности, k шин записи прямого значения аргумента соединены соответственно с k выходными шинами записи, причем суммарное число витков k обмоток записи прямого значения аргумента соответствует весу порога пороговой функции.

8=1 — 8=3 записи соответственно прямых значений первого, второго и третьего аргументов, шины 9=1 — 9=3 записи инверсных значений соответственно первого, второго и третьего аргументов, выходные шины

10=1 — 10=3 записи соответственно первого, второго и третьего аргументов.

Логический элемент (фиг.2) содержит микросердечники 11=1 и 11=2 диоды 12=1 и 12=2, обмотки 13=1 и 13=2 считывания, обмотки 14=1 — 14=3 записи прямых значений соответственно первого, второго и третьего аргументов, обмотку 15 начальной установки, входную шину 16= 1 считывания, выходные шины 16= 2 и 16= 3 считывания, шины 17=1 — 17=3 записи прямых значений соответственно первого, второго и третьего аргументов, шины 18=1 — 18=3 записи инверсных значений соответственно первого, второго и третьего аргументов, выходные шины 19=1 — 19=3 записи соответственно первого, второго и третьего аргументов.

Начала встречно включенных обмоток

3=1 и 3=2 считывания (фиг.1) выполненных соответственно на микросердечниках

1=1 и 1=2, соединены с входной шиной

7= 1 считывания, концы обмоток 3= 1 и 3=2 соединены соответственно с анодами диодов 2= 1 и 2=2, катоды которых соединены соответственно с выходными шинами

7=2 и 7=3 считывания, шины 8=1 — 8=3 записи прямых значений аргументов соединены соответственно с началами обмоток

4=1, 5=1 и 6=1 записи прямых значений аргументов, концы обмоток 4=1, 5=1 и

6=1 соединены соответственно с концами

1190517 обмоток 4=2, 5=2 и 6=2, начала которых соединены соответственно с шинами 9=1—

9=3 записи инверсных значений аргументов, обмотки 4=1, 5=1 и 6=1 включены соответственно встречно с обмотками 4=2, 5=2 и 6=2, обмотки 4=1 — 6=1 и

4=2 — 6=2 выполнены на микросердечниках 1=1 и 1=2, числа витков обмоток

4=1 — 6=1 соответственно равны числам витков обмоток 4= 2 — 6= 2 и соответствуют весам аргументов пороговой функции, начала обмоток 4=1 и 5=1 и конец обмотки

6=1 соединены соответственно с выходными шинами 10=1 — 10=3 записи, суммарное число витков обмоток 4=1 и 5= 1 соответствует весу порога пороговой функции.

Начала встречно включенных обмоток

13=1 и 13=2 считывания (фиг.2), выполненных соответственно на микросердечниках 11= 1 и 11=2, соединены с входной шиной 16=1, концы обмоток 13=1 и 13=2 соединены соответственно с анодами диодов

12=1 и 12=2, катоды которых соединены соответственно с выходными шинами 16=2 и

16=3 считывания, шины 17=1 — 17=3 прямых значений аргументов соединены соответственно с началами обмоток 14=1 — 14=3 записи прямых значений аргументов, концы которых соединены соответственно с шинами 18=1 — 18=3 инверсных значений аргументов, шины 17=1, 17=2 и 18=3 соединены соответственно с выходными шинами 19=1 — 19= 3 записи, обмотки 14=1—

14=3 и 15 выполнены на микросердечниках

11=1 и 11=2, числа витков обмоток 14=1—

14=3 соответствуют весам аргументов пороговой функции, суммарное число витков обмоток 14=1 и 14=2 соответствует весу порога пороговой функции.

В логических элементах (фиг.1 и 2) пороговая обмотка отсутствует, однако функция пороговой обмотки совмещена с функцией обмоток записи аргументов, при этом соотношение числа витков записи прямого и инверсного значений аргументов изменяется при сохранении общего числа витков записи прямого и инверсного значений аргумента.

Для совмещения пороговой обмотки с обмотками какого-либо аргумента надо часть витков пороговой обмотки просуммировать с прямым и инверсным значением витков аргументов. Числа витков обмоток с встречными витками вычитываются, с согласными (или нулевымй витками) — суммируются.

При этом чаще всего число витков пороговой обмотки, совмещаемых с аргументом, берется равным числу витков аргумента. Далее таким же образом производится совмещение оставшихся витков пороговой обмотки со следующим аргументом и так до пол5

50 ного исключения пороговой обмотки. В результате совмещения пороговой обмотки общее число витков уменьшается в предельном случает до 50%.

По первому варианту (фиг.1) в начальный такт производится импульсом тока запись аргументов обмотки 4 — 6 записи.

В результате записи ампер-витки обмоток суммируются, в элементе реализуется пороговая функция. Например, при реализации функции и трех аргументов обмотки записи содержат по одному витку. Суммарные ампер-витки на наборах с Xi Х Хз по

Х Х Хз равны -5,-3,-3,-1,-3,-1,-1 ед, соответственно и намагничивают микросердечник в отрицательное состояние, а на наборе

Xi Х Хз суммарные ампер-витки равны +1 ед. и намагничивают микросердечник в положительное состояние. После записи в следующий такт производится считывание вычисленного значения логической функции, для чего на шину 7=1 считывания подается импульс тока считывания, который проходит через диод 2-1 или 2-2 в зависимости от величины импеданса нелинейного дросселя многовитковой обмотки 3-1 и 3-2 считывания в соответствующей ветви.

По второму варианту (фиг.2) в начальный такт импульсом тока производится начальная установка обмоткой 15 начальной установки, затем следующим тактом производится импульсом тока запись аргументов обмотки 14=1 — 14=3 записи аргументов.

В результате записи ампер-витки обмоток суммируются, в элементе реализуется пороговая функция. Например, при реализации функции И трех аргументов обмотки записи и обмотка начальной установки содержат по одному витку. Суммарные ампер-витки на наборах с Х> Х Хз по Xi Х Хз равны

-2, -1, -1, О, -1, О, О ед. соответственно и намагничивают микросердечник в отрицательное состояние. Нулевые ампер-витки не перемагничивают микросердечник, он остается в отрицательном состоянии, установленный обмоткой начальной установки. На наборе Xi Х Хз суммарные ампер-витки равны +1 ед. и намагничивают микросердечник в положительное состояние. После записи в следующий такт производится считывание вычисленного значения логической функции, для чего на шину 16=1 считывания подается импульс считывания, который проходит через диод 12-1 или 12-2 в зависимости от величины импеданса нелинейного дросселя, многовитковой обмотки 13-1 и

13--2 считывания в соответствующей ветви.

Для ввода инверсного значения функции достаточно соединить выходные шины функции и шины записи аргумента крест накрест.

1190517

Фиг. 2

Составитель С. Ранов

Редактор О. Юрковецкая Техред И. Верес Корректор С. Черни

Заказ 7002/58 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4