Синхрогенератор

Иллюстрации

Показать всеРеферат

СИНХРОГЕНЕРАТОР, содержащий последовательно соединенные фазовый детектор, фильтр нижних частот, генератор, управляемый напряжением, счетчик импульсов горизонтальной дискретизации, а также выходной формирователь, первый и второй выходы которого соединены с вторым входом счетчика импульсов горизонтальной дискретизации и первым входом фазового детектора соответственно, счетчик импульсов вертикальной дискретизации, первый и второй входы которого соединены с третьим I BBiM и четвертым выходами выходного формирователя соответственно, второй вход фазового детектора является входом сигнала внешней синхронизации, пятый выход выходного формирователя является выходом синхрогенератора , отличающийся тем, что, с целью расширения функциональных возможностей путем расширения набора формируемых сигналов при произвольном стандарте разложения , введены первый и второй блоки памяти , контроллер памяти, а также первый и второй селекторы адреса, первые входы которых соединены с выходами счетчика импульсов горизонтальной дискретизации и счетчика импульсов вертикальной дискретизации соответственно, вторые входы - с первым и вторым выходами контроллера паi мяти соответственно, а выходы - с первыми входами первого и второгб блоков памяти СЛ соответственно, вторые входы которых соединеныс третьим и четвертым выходами контроллера памяти соответственно, а выходы - с первым и вторым выходами выходного формирователя соответственно, при этом управляюш,ий вход контроллера памяти является входом управляюш,его сигнала. со о СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 5ц 4 Н 04 N 5/06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ Ф

С1 ьф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3657170/24-09 (22) 31.10.83 (46) 07.11.85. Бюл. № 41 (72) В. И. Борисенко, Л. С. Чесалин, Ю. В. Труль, А. Ю. Халтурин и Н. А. Чарушин (71) Институт космических исследований

АН СССР и Кировский политехнический институт (53) 621.397 (088.8) (56) Патент США № 4162508, кл. Н 04 N 5/06, опублик. 198!.

Патент США № 4328513, кл. Н 04 N 5/06, опублик. 1982. (54) (57) СИНХРОГЕНЕРАТОР, содержащий последовательно соединенные фазовый детектор, фильтр нижних частот, генератор, управляемый напряжением, счетчик импульсов горизонтальной дискретизации, а также выходной формирователь, первый и второй выходы которого соединены с вторым входом счетчика импульсов горизонтальной дискретизации и первым входом фазового детектора соответственно, счетчик импульсов вертикальной дискретизации, первый и второй входы которого соединены с третьим

„,Я0„„1190540 А и четвертым выходами выходного формирователя соответственно, второй вход фазового детектора является входом сигнала внешней синхронизации, пятый выход выходного формирователя является выходом синхрогенератора, отличающийся тем, что, с целью расширения функциональных возможностей путем расширения набора формируемых сигналов при произвольном стандарте разложения, введены первый и второй блоки памяти, контроллер памяти, а также первый и второй селекторы адреса, первые входы которых соединены с выходами счетчика импульсов горизонтальной дискретизации и счетчика импульсов вертикальной дискретизации соответственно, вторые входы — с первым и вторым выходами контроллера памяти соответственно, а выходы — с первыми ® входами первого и второго блоков памяти соответственно, вторые входы которых сое- Ц Ф динены с третьим и четвертым выходами С контроллера памяти соответственно, а выходы — с первым и вторым входами выходного формирователя соответственно, при этом управляющий вход контроллера памяти является входом управляющего сигнала.

1190540

30

50

Изобретение относится к телевизионной технике и может использоваться в передающих телевизионных системах, а также в системах обработки изображений телевизионного тина.

Цель изобретения — расширение функциональных возможностей синхрогенератора путем обеспечения произвольной формы выходных сигналов и произвольного стандарта разложения.

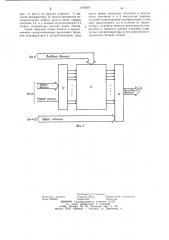

На фиг. 1 представлена структурная электрическая схема синхрогенератора; на фиг. 2 — структурная электрическая схема блока памяти, не требующего использования селектора адреса.

Синхрогенератор (фиг. 1) содержит фазовый детектор (ФД) 1, фильтр нижних частот (ФНЧ) 2, генератор 3, управляемый напряжением (ГУН), счетчик 4 импульсов горизонтальной дискретизации, счетчик 5 импульсов вертикальной дискретизации, первый 6 и второй 7 блоки памяти, выходной формирователь 8, контроллер 9 памяти, первый !О и второй 11 селекторы адреса.

Блоки 6 и 7 памяти по второму варианту выполнения (фиг. 2) содержат дешифратор

12 адреса записи, матрицу 13 памяти и мульгиплексор 14 чтения.

Синхрогенератор (фиг. 1) работает следующим образом.

На второй вход ФД 1 поступает сигнал внешней синхронизации (при работе в ведомом режиме), а с выхода ФД 1 через ФНЧ 2 управляющий сигнал поступает на вход ГУН

3, подстраивая его частоту под частоту сигнала внешней синхронизации. Частота ГУН

3 определяется из выражения

Н где M-количество элементов разложения в одной строке изображения;

Н вЂ” время развертки строки изображения.

Деление частоты ГУН 3 до частоты строчной развертки осуществляется счетчиком 4 импульсов горизонтальной дискретизации, а число строк разложения определяется модулем счета счетчика 5 импульсов вертикальной дискретизации. Модули счета счетчиков

4 и 5 импульсов горизонтальной и вертикальной дискретизации определяются информацией, записанной в первом 6 и во втором

7 блоках памяти, выходные сигналы которых через выходной формирователь 8 поступают на первые входы (входы сброса) счетчиков

4 и 5 импульсов горизонтальной и вертикальной дискретизации. Информация о форме выходных сигналов синхрогенератора и стандарте разложения вводится в первый 6 и второй 7 блоки памяти через контроллер 9 памяти, например, из ЭВМ. При этом для перекл1очения режимов записи и чтения первого 6 и второго 7 блоков памяти и коммутации адресов записи — чтения служат первый 10 и второй 11 селекторы адреса, на первые входы которых поступают адреса чтения с выходов счетчиков 4 и 5 импульсов горизонтальной дискретизации и вертикальной дискретизации, а на вторые входы поступают адреса записи и сигнал включения режима записи с первого и второго выходов контроллера 9 памяти, с третьего и четвертого выходов которого на вторые входы первого 6 и второго 7 блоков памяти поступает информация, подлежащая записи в указанные блоки, которая при считывании поступает на первый и второй входы выходного формирователя 8, представляющего собой логическую схему для преобразования последовательности считанных из первого 6 и второго 7 блоков памяти данных в выходные сигналы и сигналы обратной связи, определяющие модули счета счетчиков 4 и 5 импульсов горизонтальной и вертикальной дискретизации. Кроме этого, с первого выхода выходного формирователя 8 на первый вход ФД 1 поступает сигнал обратной связи. Например, при использовании в качестве такого сигнала импульсов с частотой кадров возможна подстройка частоты синхрогенератора под частоту сети с целью устранения асинхронной помехи.

Количество значащих разрядов счетчика

4 импульсов горизонтальной дискретизации определяется из расчета требуемой точности отображения по формуле:

К = ) loggN+0,5 (, гдеК-количество значащих разрядов счетчика 4 импульсов горизонтальной дискретизации;

1 - количество дискретных элементов разложения строки изображения; "1 — операция выделения целой части числа.

Количество значащих разрядов счетчика

5 импульсов вертикальной дискретизации определяется требованиями телевизионного стандарта, на который настроен синхрогенератор, по формуле

M =) logaL+0,5 (. гдето-количество значащих разрядов счетчика 5 импульсов вертикальной дискретизации; - — количество строк в кадре развертки данного телевизионного стандарта; .).-.I — операция выделения целой части числа.

Влияние времени программирования синхрогенератора на непрерывность формирования выходных сигналов можно полностью исключить, применив блоки памяти, построенные по представленной на фиг. 2 структурной электрической схеме. Основное отличие данного блока от аналогичного, показанного на фиг. 1, состоит в отсутствии селектора адреса и наличии отдельных дешифратора

12 адреса записи и мультиплексора 14 чтения. Благодаря этому чтение и запись матрицы 13 памяти выполняются независимо

1190540

От У

0779

0m 4/Х) Составитель Л. Стасенко

Техред И. Верее Корректор М. С амборская

Тираж 658 Подпиено«

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, ж — 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Реда кто р С. Лыж о ва

Заказ 7005/60 друг от друга по разным адресам. С выходов дешифратора 12 записи снимаютсй непосредственно адреса записи ячеек памяти

1 матрицы 13, а к входам мультиплексора 14 чтения подключ ены выходы ячеек чтения.

Таким образом, блоки памяти в предложенном синхрогенераторе выполняют функции дешифраторов и мультиплексоров, задаюших форму выходных сигналов и модуль счета счетчиков 4 и 5 импульсов горизонтальной и вертикальной дискретизации (стандарт разложения), но в отличие от аналогичных устройств имеется возможность оперативно в процессе работы изменять параметры синхрогенератора путем изменения содержимого блоков памяти.