Цифровой измеритель сдвига фаз

Иллюстрации

Показать всеРеферат

ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА ФАЗ, содержащий ограничитель сигнала , соединенный двумя выходами с первыми входами двух элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, эталонный генератор, соединенный с вторыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первыйи второй счетчики, выходы которых соединены с цифровым процессором, генератор импульсов, соединенный через элемент совпадения со счетными входами первого и второго счетчиков, времязадаювдий блок, вход которого соединен с генератором импульсов, а выходы с входами установки первого и второго счетчиков, с управляющим вхог дом цифрового процессора и с элементом совпадения, о т л и ч а ющ и и с я тем, что, с целью повышения точности измерения сдвига фаз, в него введены первый и второй стробируемые компараторы, информационные входы которых соединены соответSS ственно с выходами перйого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а (Л выходы - с управляющими входами соответственно первого и второго счетчиков, выход элемента совпадения соединен с управляющими входами стробируемых компараторов. . , со 00 4 to

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

КСПУБЛИН (gg)4 G О! R 25/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

Г1О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3746698/24-21 (22) 30.05.84 (46) 15.11.85. Бюл. ¹- 42 (71) Научно-производственное объединение "Сибцветметавтоматика (72) В.И.Кокорин, П.А.Лопардин,.

И.П.Розманов и Н.В.Салюк (53) 621.317.77(088.8) (56) Авторское свидетельство СССР

¹ 773517, кл. G 01 R 25/08, 1980.

Патент Франции № 2417116, кл. G.01 R 25/00, 1978. (54)(57)ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА

ФАЗ, содержащий ограничитель сигнала, соединенный двумя выходами с первыми входами двух элементов ИСКЛЮЧА10ЩЕЕ ИЛИ, эталонный генератор, соединенный с вторыми входами элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй счетчики, выходы которых соединены с цифровым процессором, генератор

„„Я0„„1191842 импульсов, соединенный через элемент совпадения со счетными входами первого и второго счетчиков, времязадающий блок, вход которого соединен с генератором импульсов, а выходы— с входами установки первого и второго счетчиков, с управляющим входом цифрового процессора и с элементом совпадения, о т л и ч а юшийся тем, что, с целью повышения точности измерения сдвига фаз, в него введены первый и второй стробируемые компараторы, информационные входы которых соединены соответственно с выходами перВого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы — с управляющими входами соответственно первого и второго счетчиков, выход элемента совпадения соединен с управляющими входами стробируемых компараторов.

1191842

Изобретение относится к измерительной технике и может быть использовано для измерения фазового сдвига с повышенной точностью и помехоустойчивостью сигнала известной часто10

20 частоты и помех, поступает на ограничитель l, с выхода ограничителя снимаются прямоугольные импульсы, которые подаются на логические элементы 2 и 6. Эталонный генератор

5 вырабатывает два прямоугольных квадратурных колебания, первое колебание поступает на логический элемент 2, второе, сдвинутое на 90 относительно первого, — на логический элемент 6.

Логические элементы 2 и 6 обеспечивают выполнение операций перемножения сигнала с выхода ограничителя 1 с эталонными колебаниями.

Импульсные последовательности с выходов логических элементов 2,6поступают на информационные входы стробируемых компараторов 3 и 7 соответственно, на управляющие входы компараторов подается сигнал с элеты в радионавигационных и радиогеодезических системах.

Цель изобретения — повышение точности измерения фазового сдвига.

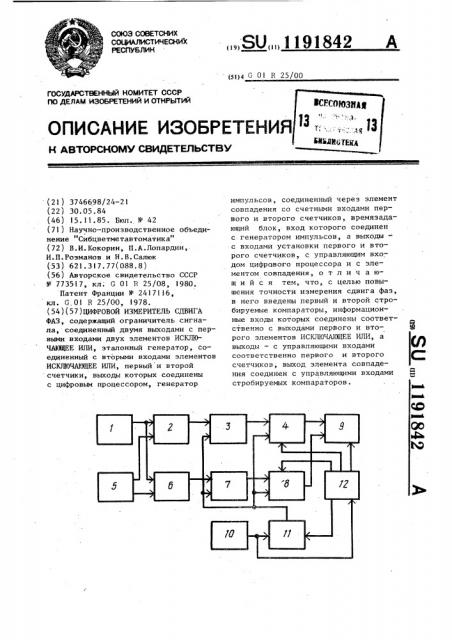

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит последовательно соединенные ограничитель сигнала 1, первый элемент ИСКЛ10ЧА10ЩЕЕ

ИЛИ 2, первый стробируемый компаратор 3, первый счетчик 4, последовательно соединенные эталонный генератор 5, второй элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 6, второй стробируемый компаратор 7, второй счетчик 8, выходы счетчиков 4, 8 соединены с цифровым процессором 9, генератор 10 импульсов соединен с элементом ll, совпадения, выход которого соединен с управляющими входами стробируемых компараторов 3 и 7 и со счетными входами счетчиков 4,8, времязадающий блок

12, выходы которого соединены с входами установки счетчиков 4 и 8, с управляющим входом цифрового процес- З0 сора 9 и с элементом совпадения 11, а вход подключен к генератору 10 импульсов.

Устройство работает следующим образом. 35

Измеряемый сигнал, представляющий смесь полезного сигнала известной мента 11 совпадения. Сигналы с выходов компараторов 3,7 используются для управления режимом работы счетчиков 4 и 8, которые подсчитывают количество импульсов, поступающих от генератора 10 импульсов.

Уровни выходного напряжения стробируемых компараторов 3 и 7 устанавливаются в момент воздействия импульсного сигнала от генератора 10 импульсов на управляющие входы ком- . параторов 3 и 7 и зависят от уровней сигналов на информационных входах компараторов 3 и 7. При этом амплитуда и длительности выходных сигналов компараторов 3 и 7 стандартизированы, длительность сигналов не может быть меньше периода повторения импульсов от генератора 10.

Выходные сигналы компараторов 3 и 7 жестко зафиксированы по времени относительно счетных импульсов, посту-, пающих на счетчики 4,8 с выхода элемента 11 совпадения. Таким образом, при флуктуации входного сигнала устройства под воздействием помех стандартизация по амплитуде и фиксация по времени сигналов управления режимом работы счетчиков 4 и 8 с помощью стробируемых компараторов 3 и 7 исключает сбои счетчиков 4 и 8 при подсчете импульсов от генератора 10 импульсов.

По окончанию измерительного цикла Т, формируемого времязадающим блоком 12, элемент 11 совпадения закрывается, коды чисел, накопленные в счетчиках 4 .и 8 за измерительный цикл и пропорциональные соответственно косинусу и синусу измеряемого сдвига фаз; переписываются в цифровой процессор 9, счетчики 4,8 затем устанавливаются в исходное (нулевое) состояние, элемент 11 совпадения открывается, и цикл измерения повторяется.

Цифровой процессор 9 вычисляет функцию арктангенса отношения измеренных величин и определяет сдвиг фаз между принимаемым и эта-. лонным сигналами.

В качестве логических элементов

2 и 6 используются элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, которые обеспечивают на выходе сигналы логической "1" при несовпадении полярностей входных импульсов и сигналы логическо1191842

15

Составитель В.Шубин

Редактор М.Келемеш Техред С.Мигунова Корректор М.Самборская

Заказ 7152/42 Тираж 747 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,.Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 го 0, когда полярности входных импульсов совпадают.

Счетчики 4 и 8 могут быть реализованы в виде суммирующих счет— чиков или в виде реверсивных счетчиков. . При использовании реверсивных счетчиков 4 и 8 сигналы с выходов стробируемых компараторов 3,7 управляют режимом счета, т.е. в моменты совпадения полярностей входных импульсов логических элементов

2,6 реверсивные счетчики 4,8 работают на суммирование, при несовпадении — на вычитание.

В случае применения суммирующих счетчиков 4 и 8 в моменты совпадения полярностей входных импульсов логических элементов 2 и 6 счетчики 4 и 8 суммируют. импульсы, поступающие от 20 генератора 10, при несовпадении полярностей входных импульсов — не считают.. Для вычисления фазы сигнала (в цифровом процессоре 9) из результатов, накопленных в суммирующих 25 счетчиках 4 и 8, вычитаются поправки,равные половине известного количества импульсов генератора 10 за измерительный цикл.

Времязадающий блок 12 обеспечивает формирование длительности цикла измерения, синхронизирует работу счетчиков 4,-8 и цифрового процессора 9.

Таким образом, в предлагаемом устройстве повышается точность измерения сдвига фаз при наличии во входном сигнале помех, благодаря исключению сбоев счетчиков, обусловленных совпадениями по времени многократных пересечений нулевого уровня смесью сигнал — шум и счетных импульсов, поступающих на счетчики от генератора импульсов. Стробируемые компараторы 3 и 7, счетчики 4 и 8, элемент 11 совпадения, генератор 10 импульсов с указанными связями осуществляют преобразование интервалов времени, выделяемых логическими элементами 2 и 6 в цифровые коды при наличии во входном сигнале помех.