Устройство для контроля логических схем

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ, содержащее формирователь импульсов, соединенный первым и вторым входами соответственно с первым и вторым выводами переключателя , соединенного третьим выводом с общей щиной устройства, щуп, соединенный выходом с выходом формирователя импульсов, D-триггер, соединенный D-BXOдом и инвертирующим -входом с выходом генератора импульсов, прямым выходом - с первым входом сумматора по модулю два, соединенного выходом с первым входом индикатора, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены первый и второй компараторы, первый и второй коммутаторы , операционный усилитель, переменный резистор, ограничивающий резистор, кнопка, причем выход щупа -соединен через замыкающие контакты кнопки с первым выводом ограничивающего резистора и вычитающим входом операционного усилителя , а непосредственно - с первым входом первого компаратора, соединенного вторым входом с первым входом устройства , выходом - с управляющими входами первого и второго коммутаторов, с С-входом /)-триггера и с вторым входом сумматора по модулю два, первый и второй информационные входы второго коммутатора соединены соответственно с вторым и третьим входами устройства, выход - с первым входом второго компаратора, соединенного выходом с вторым входом индикатора , вторым входом - с выходом операционного усилителя и с первым и вторым выводами переменного резистора, соединенного третьим выводом с вторым выводом ограничивающего резистора, суммиi рующий вход операционного усилителя соединен с выходом первого коммутатора, (Л соединенного первым и вторым информационными входами соответственно с четвертым и пятым входами устройства, третий вход индикатора соединен с шиной питания устройства. 2. Устройство по п. 1, отличающееся тем, что индикатор содержит первый и второй инверторы, соединенные входами соотсо ветственно с вторым и первым входами индикатора, выходами через соответствуюоо щие первый и второй светодиоды - с пер4 выми выводами первого и второго резисторов , соединенных вторыми выводами с третьим входом индикатора.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 G 01 R31 28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3755030/24-21 (22) 16,05.84 .(46) 15.11.85. Бюл. № 42 (72) Ф. Ф. Шнайдер, А. Г. Ташлински и и В. А. Куликов (53) 681.325 (088.8) (56) Авторское свидетельство СССР № 551575, кл. G 01 R 31/28, 1972.

Авторское свидетельство СССР № 716040, кл. G 01 R 21/28, 1976. (54) (57) 1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ, содержащее формирователь импульсов, соединенный первым и вторым входами соответственно с первым и вторым выводами переключателя, соединенного третьим выводом с общей шиной устройства, щуп, соединенный выходом с выходом формирователя импульсов, D-триггер, соединенный D-входом и инвертирующим R-входом с выходом генератора импульсов, прямым выходом — с первым входом сумматора по модулю два, соединенного выходом с первым входом индикатора, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены первый и второй компараторы, первый и второй коммутаторы, операционный усилитель, переменный резистор, ограничивающий резистор, кнопка, причем выход щупа соединен через замыкающие контакты кнопки с первым выводом ограничивающего резистора и вычитающим входом операционного уси„.SU„„1191847 A лителя, а непосредственно — с первым входом первого компаратора, соединенного вторым входом с первым входом устройства, выходом — с управляющими входами первого и второго коммутаторов, с С-входом D-триггера и с вторым входом сумматора по модулю два, первый и второй информационные входы второго коммутатора соединены соответственно с вторым и третьим входами устройства, выход — с первым входом второго компаратора, соединенного выходом с вторым входом индикатора, вторым входом — с выходом операционного усилителя и с первым и вторым выводами переменного резистора, соединенного третьим выводом с вторым выводом ограничивающего резистора, сумми- д рующий вход операционного усилителя сое- @ динен с выходом первого коммутатора, уу соединенного первым и вторым информа- %Ю ф ционными входами соответственно с четвертым и пятым входами устройства, третий вход индикатора соединен с шиной питания устройства.

2. Устройство по п. 1, отличающееся тем, что индикатор содержит первый и второй инверторы, соединенные входами соответственно с вторым и первым входами индикатора, выходами через соответствующие первый и второй светодиоды — с пер- QQ ными выводами первого и второго резисто- Д ров, соединенных вторыми выводами с третьим входом индикатора.

1191847

Изобретение относится к контрольноизмерительной технике и может быть использовано для контроля и, настройки устройств, построенных на логических микросхемах, например ТТЛ-микросхемах.

Цель изобретения — повышение достоверности контроля путем обеспечения возможности выявления замыкания информационных связей и контроля выходного тока логических элементов.

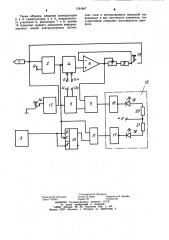

На чертеже приведена схема предлагаемого устройства.

Устройство содержит щуп 1, первый

2 и второй 3 компараторы, первый 4 и второй 5 коммутаторы, операционный усилитель 6, переменный резистор 7, ограничивающий резистор 8, генератор 9 импульсов, D-триггер 10, сумматор 11 по модулю два, индикатор 12, кнопку 13, переклю. чатель 14, формирователь 15 импульсов.

Индикатор 12 содержит первый 16 и второй 17 инверторы, первый 18 и второй

19 светодиоды, первый 20 и второй 21 резисторы.

Первый и второй входы формирователя

15. импульсов соединены соответственно с первым и вторым выводами переключателя 14, соединенного третьим выводом с общей шиной устройства. Выход щупа 1 соединен с выходом формирователя 15 импульсов. D-вход и инвертирующий R-вход

D — триггера 10 соединены с выходом генератора 9 импульсов, прямой выход — с первым входом сумматора 11 по модулю два, соединенного выходом с первым входом индикатора 12. Выход щупа 1 соединен через замыкающие контакты кнопки 13 с первым выводом ограничивающего резистора 8 и вычитающим входом операционного усилителя 6, а непосредственно — с первым входом первого компаратора 2, соединенного вторым входом с первым входом устройства, выходом — с управляющими входами первого 4 и второго 5 коммутаторов, с С-входом D-.триггера 10 и с вторым входом сумматора 11 по модулю два. Первый и второй информационные входы второго коммутатора 5 соединены соответственно с вторым и третьим входами устройства, выход — с первым входом второго компаратора 3, соединенного выходом с вторым входом индикатора 12, вторым входом — с выходом операционного усилителя 6 и с первым и вторым выводами переменного резистора,7, соединенного третьим выводом с вторым выводом ограничивающего резистора 8, суммирующий вход операционного усилителя 6 соединен с выходом первого коммутатора

4, соединенного первым и вторым информационными входами соответственно с четвертым и пятым входами устройства, третий вход индикатора соединен с шиной питания устройства. В индикаторе 12 первый 16 и, второй 17 инверторы соедине5

55 ны входами соответственно с вторым и первым входами индикатора, выходами через соответствующие первый 18 и второй 19 светодиоды — с первыми выводами соответствующих первого 20 и второго 21 резисторов, соединенных вторыми выводами с третьим входом индикатора.

Устройство работает следующим образом.

Устройствб позволяет: контролировать логическое состояние в исследуемой точке электрической цепи логической схемы; фиксировать наличие в исследуемой цепи импульсной последовательности, а также замыкание ее на одну из шин питания; производить безразрывный контроль выходного тока логических элементов.

Для контроля .логического состояния электрической цепи и определения наличия в ней импульсной последовательности служат компактор 2, генератор 9, D-триггер

10, сумматор 11 по модулю два, а также щуп 1 и индикатор 12, использующийся во всех режимах. Компаратор 2 выполняет функции буферного элемента и служит для увеличени я входного сопротивления.

Чтобы логическое состояние на выходе компаратора 2 соотвегствовало состоянию на выходе щупа 1, на его опорный вход подают напряжение Uo, находящееся между уровнями «О» и «1» исследуемых логических элементов (примерно 1,5 В для ИС

ТТЛ серий). Сигнал с генератора 9, вырабатывающего короткие отрицательные импульсы, поступает одновременно на R- u

D-входы D-триггера 10. Благодаря этому при неизменном состоянии на С-входе D-триггера 10 на его прямом выходе присутствует потенциал логического «О», а на выходе сумматора 11 по модулю два, выполняющего функцию сравнения, — логическое состояние контролируемой логической схемы, которое отражается на индикаторе 12 светодиодом 19, подключенным через инвертор 17 к выходу сумматора

11 по модулю два (при «1» íà щупе 1 включается светодиод 19). Резистор 21 ограничивает ток светодиода 19. При наличии в исследуемой цепи импульсной последовательности D-триггер 10 (при совпадении момента прихода импульса на С-вход с единичным состоянием на D-входе), переключается в состояние с логическим нулем на прямом выходе. В результате свечение светодиода 19 становится прерывистым.

Частоту генератора 9 выбирают из условия, чтобы «мигание» светодиода 19 было хорошо заметным для глаза. . Для определения факта замыкания исследуемой цепи на одну из шин питания служит формирователь 15 импульсов и переключатель 14. При коммутации переключателя 14 формирователь 15 импульсов вырабатывает положительный и отрицательный импульсы, мощность которых достаточна для принудительного переключе1191847

10 ния (на время импульса) выхода исследуемого элемента в противоположное состояние, но не достаточна для изменения потенциала шин питания. Наличие принудительного переключения (о чем свидетельствует мигание светодиода 19) свидетельствует об отсутствии замыкания цепи на шину питания. На выходе формирователя 15 импульсов должна быть предусмотрена развязка (например, диодная) от выхода щупа 1. Длительность импульсов формирователя 15 выбирается из удобства их визуальной регистрации и исключения выхода из строя микросхемы.

Контроль выходного тока исследуемых логических элементов без изъятия их из последовательной логической схемы осуществляется с помощью коммутаторов 4 и 5, компаратора 3, операционного усилителя 6 и кнопки 13. Выходной ток исследуемого логического элемента складывается из входных токов элементов, на которые он нагружен. Принцип безразрывного контроля выходного тока заключается в том, чтобы осуществить «перехват» тока нагрузки данного элемента и переключить его из цепи выхода исследуемого элемента в цепь данного устройства, где возможно его измерить. С этой целью щуп 1 подключается к выходу исследуемого логического элемента и в зависимости от состояния его выхода на выходе компаратора 2 формируется сигнал логического «0» или логической «1». Если на щупе 1 имеется логический «О», на управляющие входы коммутатора 4 и коммутатора 5 поступает сигнал логического «О», коммутатор 4 подключает к суммирующему входу усилителя 6 напряжение «земли» «0» со своего первого информационного входа, а коммутатор 5 подключает к входу компаратора 3 эталонное напряжение U> со своего первого информационного входа. Если на щупе 1 имеется логическая «1», на управляющие входы коммутатора 4 и коммутатора 5 поступает сигнал логического «О», коммутатор 4 подключает к суммирующему входу усилителя 6 напряжение питания Uï, со своего второго информационного входа, а коммутатор 5 подключает к входу компаратора 3 эталонное напряжение U co своего второго информационного входа.

В этом случае, если на суммирующем входе усилителя 6 задается сигнал «О», ввиду наличИя отрицательной обратной связи выхода усилителя 6 через резисторы 7 и 8 с его вычитающим входом на этом входе также устанавливается уровень

«земли» «О». При замыкании кнопки 13 выходной ток 3m x исследуемого элемента переключается с выхода этого элемента и втекает в цепь: щуп 1; кнопка 13; резисторы 7 и 8; выход усилителя 6, поскольку указанная цепь фактически шунтирует выход исследуемого логического элемента на

«землю», задаваемую с вычитающего входа усилителя 6.

При этом на входе усилителя 6 устанавливается отрицательное Us ., определяющееся из соотношения — Uâûõ+ Э вых (Яу+ Rs) = О (1) где R7 и Rs — сопротивления резисторов 7 и 8 соответственно.

Из соотношения (1) следует, что ц Us — вьюк R

-1 вых (2) т. е., что при постоянном значении Uswx, например при Us+$_#_ = U1, величина сопротивления К„пропорциональна величине контролируемого тока 3», .

Следовательно, задав на вход компаратора 3 значение Ui через коммутатор 5 и меняя величину сопротивления резистора

7, по срабатыванию компаратора 3 можно судить о наличии на выходе усилителя 6 напряжения U>.

В момент срабатывания компаратор

3 через инвертор 16 и ограничивающий резистор 20 включается светодиод 18, свидетельствуя о том, что заданный уровень напряжения U (U ) на выходе усилителя 6 достигнут. При этом величина сопротивления резистора 7 .пропорциональна току

Л.ы (соотношение 1), связав резистор 7 со шкалой и проградуировав шкалу, можно по ее показаниям определить величину тока нагрузки исследуемых логических элементов.

Аналогично устройство работает и при логической «1» íà щупе 1. При этом на вычитающем входе усилителя 6 формируется уровень напряжения питания и устройство перехватывает ток питания входов элементов, нагружающих выход исследуемого элемента на себя. ТокЗ„ вытекает из цепи: выход усилителя 6; резисторы 7, 8; кнопка 13, щуп 1, и втекает в нагрузку исследуемого логического элемента. Измерение тока осуществляется регулировкой с помощью резистора 7 положительного выходного напряжения усилителя 6 и компаратора

3 до величины 14.

Контроль выходного тока логических элементов позволяет, например, производить поиск такого распространенного и трудно определяемого дефекта логических схем, как замыкание двух информационных связей. Поскольку величина входного тока по нулю и единице нормируема, ток выхода элемента при его обратном смещении известен и слабо меняется от элемента к элементу; предлагаемое устройство позволяет определить число входов, подключенных к выходу контролируемого элемента. Таким образом, сравнивая реальное и требуемое число входов можно выявить указанный дефект.

1191847

Составитель В. Дворкин

Редактор М. Келемеш, Техред И. Верес Корректор И. Эрдейи

Заказ 7153I43 Тираж 747 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская на 6., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4

Таким образом, введение компараторов

2 и 3, коммутаторов 4 и 5, операционного усилителя 6, резисторов 7 и 8, кнопки

13 позволяет выявить замыкания информационных связей контролируемых логических схем и контролировать выходной ток входящих в них логических элементов, что существенно повышает достоверность контроля.