Устройство для суммирования двоичных чисел

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ ДВОИЧУЫХ ЧИСЕЛ, содержащее параллельньйсумматор, разряды первогс числового входа которого соединены с первой входной числовой шиной устройства, разряды второго числового входа - с второй входной чи шовой шиной устройства, разряды первого и второго входов знака параллельного сумматора - с соответствующими входными шинами знака устройства, выходы разрядов и знака параллельного сумматора - соответственно с разрядами выходной числовой шины и выходной шины знака устройства, о тличающееся тем, что, с целью расширения области применения путем обеспечения возможности суммирования чисел как в дополнительном, так и в обратном коде, устройство дополнительно содержит три элемента И, два элемента ИЛИ и два элемента ЗАПРЕТ, пр4}чем первый разряд первой входной шины знака соединен с первым входом первого элемента И, с прямым входом первого элемента ЗАПРЕТ и с инверсным входом второго элемента ЗАПРЕТ, первый разряд второй входной шины знака соединен с вторым входом первого элемента И, с инверсным входом первого элемента ЗАПРЕТ и с прямым входом второго элемента ЗАПРЕТ, СП выходы первого и второго элементов ЗАПРЕТ соединены с первыми входами с соответственно второго и третьего элементов И, вторые входа которых § подключены соответственно к первому и второму входам задания режима устройства и первому и второму вхосо со дам первого элемента ИЛИ, выход которого соединен с третьим входом первого элемента И, выходы первого, а второго и третьего элементов И О) подключены к соответствующим входам ел второго элемента ИЛИ, выход которого соединен с входом переноса младшего разряда параллельного сумматора.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

15Р4 G 06 F,7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

l)O ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЖ (21) 3739628/24-24 (22) 11.05.84 (46) 23.11.85.Бюл.¹ 43 (71) Тернопольский финансово-экономический институт (72), 3.И.Домбровский.и M.À.Äóäà (53) 681.325(088.8) (56) Соловьев Г.Н. Арифметические устройства ЭВМ.М: Энергия, 1978, с.89, рис.4-)5a.

Самофалов К.Г., Корнейчук В.И., Тарасенко В.П./Под ред.К.Г.Самофалова. Электронные цифровые вычислительные машины. Киев: Впща школа, )976, с.167, рис.112 а (54)(57) УСТРОЙСТВО ДЛЯ СУИМИРОВА

НИЯ ДВОИЧНЫХ ЧИСЕЛ, содержащее параллельный сумматор, разряды первогс числового входа которого соединены с первой входной числовой шиной устройства, разряды второго числового входа †. с второй входной числовой шиной устройства, разряды первого и второго входов знака. параллельного сумматора — с соответствующими входными шинами знака устройства, выходы разрядов и знака параллельного сумматора — соответственно с разрядами выходной числовой шины и выходной шины знака устройства, о т- л и ч а ю щ е е с я тем, что, с

„„SU„„1193665 А целью расширения области применения путем обеспечения воэможности суммирования чисел как в дополнительном, так и в обратном коде, устройство дополнительно содержит три элемента

И, два элемента ИЛИ и два элемента

ЗАПРЕТ, причем первый разряд первой входной шины знака соединен с первьм входом первого элемента И, с прямым входом первого элемента ЗАПРЕТ и с инверсным входом второго элемента

ЗАПРЕТ, первый разряд второй входной шины знака соединен с вторым входом первого элемента И, с инверсным входом первого элемента ЗАПРЕТ и с прямым входом второго элемента ЗАПРЕТ, выходы первого и второго элементов

ЗАПРЕТ соединены с первыми входами соответственно второго и третьего элементов И, вторые входы которых подключены соответственно к первому и второму входам задания режима устройства и первому и второму входам первого элемента ИЛИ, выход которого соединен с третьим входом первого элемента И, выходы первого, второго и третьего элементов И подключены к соответствующим входам второго элемента ИЛИ, выход которого соединен с входом переноса младшего разряда параллельного сумматора.

93665

1 11

Изобретение относится к вычисли-тельной технике и может быть использовано при построении арифметических устройств 3ВМ.

Целью изобретения является расширение области применения устройства путем обеспечения возможности суммирования чисел как в дополнительном, так и в обратном коде.

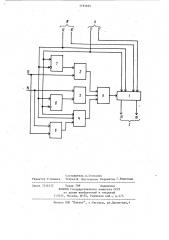

На чертеже представлена структурная схема устройства для суммирования двоичных чисел.

Устройство содержит параллельный сумматор 1, элементы И 2-4, ИЛИ 5 и 6 и ЗАПРЕТ 7 и 8. Устройство содержит входные числовые шины 9 и 10 слагаемых и входные шины 11 и 12 знаков, а также входы 13 и 14 задания режима и выходную числовую шину 15, выходную шину 16 знака.

Устройство для суммирования двоичных чисел работает следующим образом.

Числа А и В, поступающие на соответствующие входные шины 9,11 и

10,)2 устройства, представлены и числовыми и двумя знаковыми разрядами, а результат С на шинах 15 и 16 устройства представлен также и числовыми и двумя знаковыми разрядами.

При этом числа А и В, поступающие на соответствующие шины 9, 11 и

10,12 устройства, кодируются обратными или дополнительными модифицированными кодами, а результат С на шинах 15 и 16 устройства - только в дополнительном модифицйрованном коде.

Если числа А и В представлены в дополнительных модифицированных кодах, то на входах 13 и 14 задания режима устройства должны быть нулсвые сигналы. При этом результат суммирования С также представлен в дополнительном модифицированном коде.

Если число А представлено в обратном модифицированном коде, а число  — в дополнительном модифицированном коде, то на входе 13 за-. дания режима устройства должен быть единичный сигнал, а на входе 14— нулевой сигнал. Если число А отрицательное, а число В положительное, то на выходе элемента ЗАПРЕТ 7, а следовательно, и на выходах элементов И 2 и ИЛИ 5 будут единичные сигналы, вследствие чего в младший разряд сумматора 1 поступает дополнительная единица. Если числа А и В отрицательные, то на выходе элемента И 4, а следовательно, и на выходе элемента ИЛИ 5 будет единичный сигнал, вследствие чего в младший разряд сумматора 1 также поступает дополнительная единица. Если числа А и В положительные или число

А положительное, а число В отрицательное, то на выходах элементов

ЗАПРЕТ 7, И2, И4 и ИЛИ 5 будут нулевые сигналы; вследствие чего в младший разряд сумматора 1 дополнительная единица не поступает . Результат суммирования С представлен в дополнительном модифицированном коде.

Если число А представлено в дополнительном модифицированном коде, а число  — в обратном модифицированном коде, то на входе 14 задания режима устройства должен быть единичный сигнал, а на входе 13 — нулевой сигнал. Если число В отрицательное, а число А положительное, то на выходе элемента ЗАПРЕТ.8, а следовательно, и на выходах элементов И 3 и ИЛИ 5 будут единичные сигналы, вследствие чего в младший разряд сумматора 1 поступает дополнительная единица. Если числа А и В отрицательные, то на выходе элемента

И 4, а следовательно, и на выходе элемента ИЛИ 5 будет единичный сигнал, вследствие чего в младший разряд сумматора 1 также поступает дополнительная единица. Если числа

А и В положительные или число В положительное, а число А отрицательное, то на выходах элементов ЗАПРЕТ

8 И 3, И 4 и ИЛИ 5 будут нулевые сигналы, вследствие чего в младший разряд сумматора 1 дополнительная единица не поступает. Результат суммирования С представлен в дополнительном модифицированном коде.

1193665

11 9

Тираж 70.9 Подписное

ВНИ1П1И Государственного комитета СССР по делам изобретений и открытий

I13035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 7316/52

Филиал ППП "Патент", г.ужгород, ул.Проектная,4

Составитель .А.Степанов

Редактор Р.Цицика Техред Ж.. Кастелевич Корректор Г.Решетник