Аналого-цифровой интегратор синусоидальных сигналов

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ, содержащий интегрирующий усилитель, первый вход которого является входом интегратора и через ключ соединен с вторым входом интегрирующего усилителя, третьим входом связанного через цифроаналоговый преобразователь с выходом первого аналого-цифрового преобразователя, подключенного входом к выходу интегрирующего усилителя, а выходом - к первому входу блока суммирования кодов приращений, выход которого является выходом интегратора, а второй вход через блок элементов ИЛИ-НЕ соединен с выходом суммирующего блока , -входы которого подключены к выходам первого и второго регистров. формирователь интервалов интегрирования , первый выход которого подключен к стробирующим входам аналого-цифрового и цифроаналогового преобразователей и входу разрешения блока суммирования кодов приращений, а второй выход соединен с управляющим входом ключа, второй аналого-цифровой преобразователь, выход которого подключен к информационному входу первого регистра, информационный вход второго регистра соединен с выходом блока суммирования кодов приращений , выход блока квантования по времени через формирователь имI пульсов подключен к входу синхрони (Л зации второго аналого-цифрового преобразователя , первого и второго регистров и блока суммирования кодов приращений, отличающийся тем, что, с целью повьшения точности интегрирования, он содержит фазовращатель и многовходовый элемент ИЛИ-НЕ, включенный между выходом сумсо мирующего блока и вторым входом бло00 ка элементов ИЛИ-НЕ, вход фазовращаа теля подключен к входу интегратора, а выход соединен с входами второго 4;: аналого-цифрового преобразователя и входом блока 1 вантования по времени.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И), (51) 4 G 06 F 7/68

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3743318/24-24 (22) 18.05.84 (46) 23.11.85.Бюл. Ф 43 (72) П.А.Сависько, А.А.Манько, А.А.Коекин, С.Л.Наугольных и В.Г.Спирин (53) 681.335(088.8) (56) Авторское свидетельство СССР

1(- 842867, кл. G 06 3 1/00, 1979.

Авторское свидетельство СССР

NP 1056227, кл. G 06 J 1/00, !982 ° (54)(57) АНАЛОГО-ЦИФРОВОЙ ИНТЕГРА-

Т0Р СИНУСОИЛАЛЬНЫХ СИГНАЛОВ, содержащий интегрирующий усилитель, первый вход которого является входом интегратора и через ключ соединен с вторым входом интегрирующего усилителя, третьим входом связанного через цифроаналоговый преобразователь с выходом первого аналого-цифрового преобразователя, подключенного входом к выходу интегрирующего усилителя, а выходом — к первому входу блока суммирования кодов приращений, выход которого является выходом интегратора, а второй вход через блок элементов ИЛИ-HE соединен с выходом суммирующего блока, -входы которого подключены к выходам первого и второго регистров, формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и цифроаналогового преобразователей и входу разрешения блока суммирования кодов приращений, а второй выход соединен с управляющим входом ключа, второй аналого-цифровой преобразователь, выход которого подключен к информационному входу первого регистра, информационный вход второго регистра соединен с выходом блока суммирования кодов приращений, выход блока квантования по времени через формирователь импульсов подключен к входу синхронизации второго аналого-цифрового преобразователя, первого и второго регистров и блока суммирования кодов приращений, отличающийся тем, что, с целью повышения точности интегрирования, он содержит фазовращатель и многовходовый элемент

ИЛИ-НЕ, включенный между выходом суммирующего блока и вторым входом блока элементов ИЛИ-НЕ, вход фазовращателя подключен к входу интегратора,. а выход соединен с входами второго аналого-цифрового преобразователя и входом блока квантования по времени.

3674

1 119

Изобретение относится к вычислительной технике и может быть использовано при проектировании аналого-цифровых вычислительных средств.

Цель изобретения — повышение точ- 5 ности интегрирования синусоидальных сигналов.

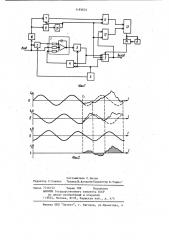

На фиг. 1 представлена функциональная схема предлагаемого интегратора; на фиг.2 — эпюры сигналов, по- 10 ясняющих принцип работы интегратора: 1-входной сигнал, Е-сигнал на выходе фазовращателя, S — график закона,.по которому изменяется код на выходе предлагаемого устройства, ъ -выделен-I5 ная помеха, по закону которой изме- . няется код на выходе суммирующего блока.

Аналого-цифровой интегратор(фиг.1 содержит интегрирующий усилитель 1, 20 ключ 2, аналого-цифровой преобразователь (,АЦП)3, цифроаналоговый преобразователь (ЦАП ) 4,, блок 5 суммирования кодов приращений, формирователь 6 интервалов интегрирования, дополнительный АЦП 7, блок 8 квантования по времени, многовходовый элемент HJIH-HE 9, фазовращатель 10, первый 11 и второй 12 регистры, суммирующий блок 13, блок 14 элементов 36

ИЛИ-НЕ, формирователь 15 импульсов.

Устройство работает следующим образом..

При поСтуплении на вход аналогоцифрового интегратора синусоидаль- 35 ного сигнала без помехи происходят интегрирование сигнала на интегрирующем усилителе 1, преобразование выходного сигнала интегрирования в цифровой код АЦП 3. Этот код посту- 40 пает на вход блока 5 суммирования кодов приращений, выходной код которого изменяется по закону косинуса (фиг.2в ).

Входной сигнал поступает также на фазовращатель 10, который осуществляет сдвиг фазы входного сигнала на 7(/2. С выхода фазовращателя сигнал подается на вход дополнительного

AgII 7 и вход блока 8 квантования по времени. Импульсы.на выходе блока 8 квантования по времени, частота которых зависит от скорости изменения входного сигнала, поступают на вход формирователя 15 импульсов. Импульсы с выхода формирователя 15 синхро2 низируют АЦП.7, первый 11 и второй

12 регистры, блок 5 суммирования кодов приращения. Дополнительный AIJg-7 преобразует сдвинутый по фазе входной сигнал в код. Этот код записывается на первой регистре 11 и затем суммируется в суммирующем блоке 13 с кодом выходного сигнала интегратора, который записывается на втором регистре 12. При отсутствии помехи, сумма этих кодов на выходе блока 13 равна нулю (фиг.2г, интервал СО, t„)J.

При этом на выходе многовходового элемента ИЛИ-НЕ 9 присутствует логическая "1", которая поступает на блок 14 элементов ИЛИ-НЕ и тем самым блокирует съем кода с выхода суммирующего блока 13.

При воздействии на входной сигнал помехи любой длительности и любой амплитуды (фиг.2а, интервал (t<, a j) на выходе АЦП 7 изменение кода под воздействием помехи имеет вид (фиг.26, интервал (t „, )). На выходе блока 5 суммирования кодов приращений в момент поступления по- мехи t„ на суммирующий блок 13 имеет место код синусоидального сигнала без .помехи (фиг.26 ). Эти коды складываются на суммирующем блоке 13, на выходе которого присутствуют текущие значения помехи, фиксированные с частотой квантования блока 8 квантования. При этом при появлении на одном из выходов блока 13 хотя бы одной логической "1", на выходе многовходового элемента HJIH-НЕ 9 появляется логический "0", который поступает на блок 14 элементов

ИЛИ-НЕ, открывая доступ сигнала с выхода суммирующего блока 13 на блок 5 суммирования кодов приращений.

При поступлении на вход 1 блока

5 сигнала с помехой последняя компенсируется. В результате этих процессов на выходе блока 5 суммирования кодов приращений всегда имеется чистый сигнал без помехи.

Преимуществом изобретения по сравнению с известным устройством является повышение точности интегрирования синусоидального сигнала при воздействии помехи любой амплитуды и длительности (у известного устройства при длительности помехи

Тп 7 2 Т она не устраняется).

1193674 фигЛ х, Составитель С.Белан

Редактор С.Саенко Техред И:.Асталош Корректор Е.Рошко" ,Заказ 7316/52 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

11 %35, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул.Проектная, 4