Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ, содержащее ретгистр номера такта контроля, два. дешифратора, -первый элемент ИЛИ, элемент И, группу элементов И, п блоков контроля (где п - .число входов или выходов контролируемого логического блока ), каждый из которых , содержит первую группу элементов И, первую схему сравнения, реrjiCTp , причем первые входы элементов И первой группы i-ro блока контроля соединены с соответствующими выходами первого дещифратора, выходы элементов И первой группы каждого i-ro блока контроля соединены с информационными входами регистра, информа-, ционные входы регистра номера такта контроля подключены к входу номера такта контроля устройства, выходы второго дешифратора соединены с первыми входами соответствующих элементов И группы, входы контролируемого логического блока являются информационными входами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за контроля дис-: кретных автоматов с памятью, в него, введены счетчик, элемент задержки. регистр эталона, три элемента ШШ, а .в каждый i-й блок контроля - триггер , вторая группа элементов И,., вторая схема сравнения, причем. входы первого элемента ИЛИ соединены с соответствующими входами конфролируемого логического блока, выход первого элемента ИЛИ соединен со счетным входом счетчика и с входом элемента задержки, выход которого соединен с входами-разрешения первых схем сравнения блоков контроля , группа информационных выходов счетчика соединена с группой информационных входов первого дешифратора , выходы которого соединены с соответствук«дими входами второго (О . элемента ШШ и с вторыми входами соответствующих элементов И группы, с выход второго элемента ИЛИ соединен § . с первыми входами первых схем сравнения блоков контроля,, второй вход первых схем сравнени-я блоков контроля соединен с соответствующими входа ми контролируемого логического блока, , оо выход первой схемы сравнения каждого . Од : i-ro блока контроля соединен с вторыми входами элементов И первой группы и со счетным входом триггера своего блока со контроля, в каждом i-M блоке контроля выходы региатра соединены с первыми входами соответствующих элементов И второй группы, выход триггера соединен с первым вх.одом второй схемы сравнения, йнформа11;ионные входы регистра эталонного сигнала под-г ключены к входу эталона устройства, каждый i-й информационный.:вьрсод регистра эталона соединен с вторым входом второй схемы сравнения одноимеиного блока контроля, выход цесрав

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„1193679 (5D4 G 06 У 11 00

1

1 Д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY. СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTMA (21) .3746070/24-24 (22) 25. ° 05.84 (46) 23.11.85. Бюл. № 43 (72) О.Ф. Жуков, А.Н, Гришуткин, К).Г. .Нехорошев и Н.Н. Новиков (53) 681.3 (088 ° 8 ) (56) Авторское свидетельство СССР

¹ 661552, кл. G 06 F 11/00, 1976.

Авторское свидетельство .СССР № 1048476, кл. G 06 F, 11/00, 1981 (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

ЛОГИЧЕСКИХ БЛОКОВ, содержащее ре. гистр номера такта контроля, два. дешифратора, первый элемент ИЛИ, элемент И, группу элементов И, и блоков контроля (где п — число входов или выходов контролируемого логического блока ), каждый из которых содержит первую группу элементов И,. первую схему сравнения, регистр, причем первые входы элементов

И первой группы i-го блока контроля соединены с соответствующими выходами первого дешифратора, выходы эле™ ментов И первой группы каждого i-ro блока контроля соединены с информа . ционными входами регистра, информа-, ционные входы регистра номера такта контроля подключены. к входу номера такта контроля устройства, выходы второго дешифратора соединены с первыми входами соответствующих элементов И группы, входы контролируемого логического блока являются информационными входами устройства, о т л и ч .а ю щ е е с я тем. что, с целью расширения функциональных возможностей за счеу контроля дискретных автоматов с памятью,.в него. введены счетчик, элемент задержки, регистр эталона, три элемента ИЛИ, а в каждый -й блок контроля - триггер, вторая группа элементов И,, вторая схема сравнения, причем. входы первого элемента ИЛИ соеди- нены с соответствующими входами кон1ролируемого логического блока, выход первого элемента ИЛИ соединен со счетным входом счетчика и с входом элемента задержки, выход которого соединен с входами. разрешения первых схем сравнения блоков контроля, группа информационных выходов счетчика соединена с группой информационных входов первого дешифратора, выходы которого соединены с 19

Ф соответствующими входами второго элемента ИЛИ и с вторыми входами соответствующих элементов И гРуппы, . См выход второго элемента ИЛИ соединен ,с первыми входами первых схем срав- Я нения блоков контроля„ второй вход первых схем сравнения блоков контроля соединен с соответствующими входами контролируемого логического блока,, CO выход первой схемы сравнения каждого . фм

: i-го блока контроля соединен с вторыми фф входами элементов И первой группы и Д со счетным входом триггера. своего блока 1 © контроля, в каждом i-м блоке контроля выходы региетра соединены с первыми входами соответствующих элементов И второй группы, выход триггера соединен с первым входом второй схемы сравнения, информациоиные входы регистра эталонного сигнала под-,. ключены к входу эталона устройства, каждый i-й информационный, выход регистра эталона соединен с вторым входом второй схемы сравнения одноименного блока контроля, выход несрав11 нения второй схемы сравнения i-го блока контроля соединен с вторыми входами элементов И второй группы

Ъ данного блока контроля, выходы эле ментов И второй группы блоков контроля подключены к выходу индикации устройства, выход сравнения второй схемы сравнения i-ro блока контроля соеди-. нен с соответствующим входом элемента

И,выход которого соединен с первым вхо.дом третьего элемента ИЛИ, второй вход которого соединен с входами

93679 сброса регистра эталона, регистра номера такта контроля, регистров блоков .контроля и подключен к входу сброса устройства, выход третьего элемента ИЛИ соединен с входом обнуления счетчика, входами обнуления регистров и триггеров блоков контроля, выходы элементов И группы соединены с соответствующими входами четвертого элемента ИЛИ, выход которого соединен с.входами разрешения вторых схем сравнения. блоков контроля.

Изобретение относится к вычислительной .технике и может быть использовано при функциональном диагностировании аппаратуры.

Цель изобретения — расширение функциональных возможностей за счет контроля дискретных автоматов с памятью..

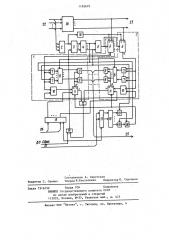

На чертеже представлена блоксхема предлагаемого устройства.

Устройство содержит i-й блок 1 контроля (i=1,...,n, где и — число выходов контролируемого логического блока), первый элемент ИЛИ 2, счетчик 3, первый дешифратор 4, вторс": элемент ИЛИ 5, в каждом i-м блоке контроля содержатся первая схема 6 сравнения, первая группа элементов И

7, регистр. 8, вторая группа элементов И 9, триггер 10, вторая схема

11 сравнения, элемент И 12, регистр

13 эталона, третий элемент ИЛИ 14, второй дешифратор 15, элемент 16 задержки, регистр 17 номера такта контроля, четвертый элемент ИЛИ 18, группа элементов И 19, вход 20 сброса устройства, вход 21 номера такта контроля устройства, информационные входы 22 устройства, информационные выходы 23 контролируемого логического блока, вход 24 эталона уст" ройства, выход 25 индикации устройства, контролируемый логический блок 26, Устройство работает следующим образом.

Перед началом работы по сигналу, поступающему на вход 20 сброса уст-ройства, приводятся в исходное сос-тояние счетчик 3, регистры 8, 13 и

17, триггеры 10, для контроля функционирования блока

26 по входу 21 номера такта контроля устройства в регистр 17 записывается номер такта, на котором необходимо сравнить состояние триггера

10 с информацией, записанной в ре10 гистре 13. Перед началом работы в регистр .13, как и в регистр 17, после приведения устройства в исходное состояние, записывается эталонное значение по входу 24 эталона

15 устройства.

Входные воздействия поступают по входным. шинам 22 на вход блока

26 и через элемент ИЛИ 2 на. счетный вход счетчика 3.

Количество входных воздействий (тактов ), поступающих на вход контролируемого блока, подсчитывается счетчиком 3, его выходные сигналы. поступают на дешифратор 4, а с него— на первые входы элементов, И .7, на первый вход группы элементов И 19, подготавливая их к открытию, а так-. же через элемент ИЛИ 5 - на первый с вход схемы 6 сравнения, синхронизация работы которых осуществляется по сигналу, поступающему с выхода элемента ИЛИ 2 через элемент 16 задержки, Схемы 6 сравнения реализуют логическую функцию сумматора

55 по модулю два. Выходная функция, принимающая значение логического нуля или единицы, со схемы 6 сравнения записывается через подготовлен1193679 ный к открытию один из элементов И

7 в соответствующий разряд регистров

8 в каждом i-м блоке контроля. Одновременно с выхода схем 6 сравнения выходной сигнал поступает на счетный вход триггера 10 в каждом i-м блоке контроля. Счет входных воздей= ствий счетчиком 3 прэисходит до тех пор, пока количество входных воздействий, в нем записанное, не совпадает с количеством импульсов, записанных в регистре 17. При их совпадении открывается соответствующий элемент И 19, выходной сигнал с которого поступает через элемент

ИЛИ 18 на управляющий вход схем

11 сравнения в каждом i-м блоке I контроля. Если значение выходных сигналов -триггеров 10 совпадает с соответствующим эталонным значением, записанным в регистре 13, то схемы

11 сравнения выдают сигнал "Равно", который соответствует логической ,единице. Эти сигналы поступают на элемент И 12. Выходным сигналом элемента И 12 в этом случае через элемент ИЛИ 14 производится приведение в исходное состояние счетчика 3 регистров 8, триггеров 10 блоков контроля.

Далее проверка проводится аналогично через количество тактов, которое записано в регистре 17, Если для продолжения проверки блока 26 необходимо изменить номер такта, на кото .ром необходимо сравнить значение выходных сигналов триггера 10 с эталонным значением, записанным в регистре 13, то необходимо ввести

10 йовую информацию в регистр 17 ° Если измеряется и значение эталонных выходных сигналов, то в регистр 13 записывается также новая информация, !

5 Если например, при сравнении информации, поступающей на вход схемы 11 сравнения, она вырабатывает сигнал "Неравно", то он открывает . элементы И 9, на первый вход которых

20 поступает информация с регистра 8.

Выходная информация с группы элементов И 9 поступает на выход 25 индикации. В этом случае сброс. устройства через элемент ИЛИ 14 не происходит, 25 так как эпемент И 12 закрыт.

Информация, поступающая в этом случае в выходов группы элементов

И 9, обеспечивает дальнейшую лока30 лизацию неисправности.

1193679

Составитель А. Сиротская

Редактор С. Саенко Техред Ж.Кастелевич Корректор Е. Сирохман

Заказ 73)6/52 Тираж 709 : Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4