Умножитель частоты

Иллюстрации

Показать всеРеферат

УМНОЖИТЕЛЬ ЧАСТОШ, содержа1ций двухполупериодный выпрямитель, к выходу которого подключены перВЫ& входы первого и второго амплитудных компараторов, вторые входы которых соединены с выходт1и соответственно первого и аторого делителей напряжения, а выходы первого и второго амплитудных компараторов подключены к входам соответственно первого и второго формирователей импульсов, выходы которых подключены к соответствующим входам сумматора , отличающийся тем, что, с целью повышения точности умножения частоты, в него введены последовательно соединенные дифференциатор и третий амплитудный компаратор , выход которого подключен к управляющему входу введенного блока запоминания пикового напряжения , входы первого второго делителей напряжения объединены и подключены к выходу блока запоминания пикового напряжения, сигнальный вход которого объединен с входом дифференциатора и подключен к выходу (Л двухполупериодного выпрямителя, а другой вход третьего амплитудного компаратора является опорным входом умножителя частоты.

СОЮЗ СОВЕТСНИХ

СОЩИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (ц Н 03 В 19/10

/

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВМ cð 7

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3700531/24-09 (22) 10. 02. 84 (46) 23.11 85. Бюл. У 43 (71) Уфимский ордена Ленина авиационный институт им. Орджоникидзе (72) В.Н. Турбабин и А.Ф. Павлов (53) 621. 374.4 (088.8) (56} Авторское свидетельство СССР

Ф 780147, кл. Н 03 В 19/10, 10.04.78.

Авторское свидетельство СССР

В 285987, кл. Н 03 В 19/10,03.06 .68. (54)(57) УИНОЖИТЕЛЬ ЧАСТОТЫ, содержащий двухполу выпрямитель, к выходу которого подключены первые входы первого и второго амплитудных компараторов, вторые входы которых соединены с выходами соответственно первого и второго делителей напряжения, а выходы первого и второго амплитудных компараторов подключены к входам соответственно

„„SU„„1193764 первого и второго формирователей импульсов, выходы которых подключены к соответствующим входам сумматора, отличающийся тем, что, с целью повышения точности умножения частоты, в него введены последовательно соединенные дифференциатор и третий амплитудный компаратор, выход которого подключен к управляющему входу введенного блока запоминания пикового напряжения, входы первого и второго делителей напряжения объединены и подключены к выходу блока запоминания пикового напряжения, сигнальный вход которого объединен с входом дифференциатора и подключен к выходу двухполупериодного выпрямителя, а другой вход третьего амплитудного компаратора является опорньпк входом умножителя частоты.

1193764

Изобретение относится к радиотехнике и может найти применение в различных устройствах вычислительной и измерительной техники, в Ко торых требуется преобразование гармонического напряжения в периодическую последовательность импульсов, период которых в целое число раз меньше периода гармонического напряжения.

Целью изобретения является повышение точности умножения частоты.

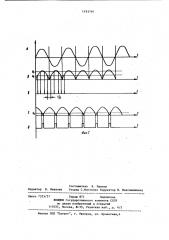

На фиг.1 приведена электрическая структурная схема умножителя частоты; на фиг.2 — диаграммы, поясняющие работу умножителя частоты.

Умножитель частоты содержит двухполупериодный выпрямитель 1, дифФеренциатор 2, первый амплитудный компаратор 3, второй ампдитудный компаратор 4, первый 5 и второй 6 делители напряжения, третий амплитудный компаратор 7, блок 8 запоминания пикового напряжения, первый 9 и второй 10 формирователи импульсов и сумматор 11.

Умножитель частоты работает следующим образом.

Напряжение входного сигнала (фиг.2at) поступает на двухполупериодный выпрямитель 1, на выходе которого формируется последовательность импульсов (фиг.2 Е). Эти импуль. сы в первом 3 и втором 4 амплитудных компараторах сравниваются с опорными постоянными напряжениями, которые подаются на вторые входы первого и второго амплитудных компараторов соответственно с первого

5 и второго 6 делителей напряжения.

При совпадении уровней напряжений импульсов, снимаемых с выхода двухполупериодного выпрямителя 1 с опорными напряжениями (U и U „ фиг.26), поступающими с первого 5 и второго 6 делителей напряжений, на выходах первого 3 и второго 4 амплитудных компараторов появляются управляющие сигналы, которые в

f5

ЗО

45 первом 9 и втором 10 формирователях импульсов преобра уются в последовательности импульсов. Эти последовательности импульсов поступают на соответствующие входы сумматора на выходе которого формируется периодическая последовательность импульсов (фиг.2e), период которой в целое число раэ (для показанного на фиг.2 примера в 8 раэ) меньше периода входного сигнала. Для того, чтобы длительность периодов следования выходных импульсов в пределах периода входного сигнала поддерживалась с высокой точностью при изменениях амплитуды входного сигнала, в умножителе частоты имеется цепь для формирования опорных постоянных напряжений, которая содержит последовательно соединенные дифференциатор 2, третий амплитудный компаратор 7 и пиковый запоминающий блок 8. С выхода двухполупериодного выпрямителя 1 на вход дифференциатора 2 поступают импульсы, которые в нем смещаются по фазе на

90 и в третьем амплитудном компараторе 7 сравниваются с опорным напряжением Uo (фиг.2e). На выходе третьего амплитудного компаратора

7 формируется последовательность импульсов (фиг.2 i) поступающих на вход управления пикового запоминающего блока 8, сигнальный вход которого соединен с выходом двухполупериодного выпрямителя 1.

При поступлении каждого последующего импульса (фиг. 2 г) в пиковом запоминающем блоке 8 происходят стирание предыдущей записи и запись уровня амплитуды следующей полуволны напряжения, поступающего на сигнальный вход блока запоминания пикового напряжения 8. В интервале времени до следующего импульса (фиг.2 ъ) это напряжение поступает на первый 5 и второй 6 делители напряжения для установки опорйых напряжений U< и U < (фиг.26).

1193764

Составитель Н. Павлов

Редактор В. Иванова Техред С.Мигунова Корректор М. Макснмишинец

Заказ 7323/57 Тирам 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. У кгород, ул. Проектная,4