Усилитель-ограничитель

Иллюстрации

Показать всеРеферат

1. УСИЛИТЕЛЬ-ОГРАНИЧИТЕЛЬ, содержащий первый и второй дифференциальные каскады, выполненные на транзисторах и подключенные, к соответствующим шинам источника питания, транзисторы первого плеча каждого дифференциального каскада включены по схеме с общим коллектором, транзисторы второго плеча каждого дифференциального каскада - по схеме с общей базой, в общей эмиттерной цепи транзисторов каждого дифференциального каскада включен соответствующий генератор тока, базы транзисторов соответствующих плеч обоих да1фференциальных каскадов объединены, коллектор транзистора второго плеча одного из дифференциальных каскадов является выходом усилителя-ограничителя, при этом один дифференциальШ| й каскад выполнен на транзистсфах n-p f структуры , а другой - на транзисторах p-h-p-структуры, отличающийся тем, что, с целью уменьшения фазовой погрешности, в него введены конденсатор, включенный между коллекторами транзисторов плеч обоих дифференциальных каскадов, и параллельная RC-цепь, вкшоченная W между базами транзисторов первых плеч обоих дифференциальных каскадов и общей шиной, причем базы транзис§ торов вторых плеч обоих дифференциальных каскадов подключены к общей шине. 2. Усилитель-ограничитель по п.1, ;о отличающийся тем, что 00 между его выходом и одной из шин источника питания включена последова тельная RС-цепь. СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)4 Н 03 6 11/00

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

Н AST0PCKOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

Il0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3698015/24-09 (22) 02.02.84 (46) 23. 11.85. Бюл. В 43 (71) Институт прикладных проблем механики н математики АН УССР (72) Б.С.Вус и В;И.Сизов (53) 621.395.664(088.8) (56) Нестеренко Б.Х. Интегральные операционные усилители. М.: Энергоиздат, 1982, с. 76-77.

Титце У. и др. Полупроводниковая схемотехника. M.: Иир, 1983, с.233234. (54)(57) 1. УСИЛИТЕЛЬ-ОГРАНИЧИТЕЛЬ, содержащий первый и второй дифференциальные каскады, выполненные на транзисторах и подключенные, к соответствующим шинам источника питания, транзисторы первого плеча каждого дифференциального каскада включены по схеме с общим коллектором, транзисторы второго плеча каждого дифференциального каскада — по схеме с общей базой, в общей эмиттерной цепи транзисторов каждого дифференциального каскада включен соответствующий

„„SU„„1193??5 A генератор тока, базы транзисторов соответствующих плеч обоих дифференциальных каскадов объединены коллектор транзистора второго плеча одного, иэ дифференциальных каскадов является выходом усилителя-ограничителя, при этом один дифференциальный каскад выполнен иа транзисторах n-P-лструктуры, а другой - на транзисторах р-ь-р-структуры, о т л и ч а ю шийся тем, что, с целью уменьшения фазовой погрешности, в него введены конденсатор, включенный между коллекторами транзисторов вторых

Я плеч обоих дифференциальных каскадов, З и параллельная РС-цепь, включенная между базами транзисторов первых плеч обоих дифференциальных касхадов и общей шиной, причем базы транзисторов вторых плеч обоих дифференциальных каскадов подключены к общей шине.

2. Усилитель-ограничитель по п.1, отличающийся тем, что между его выходом и одной иэ шин источника питания включена последовательная РС-цепь.

1193775

Изобретение относится к радиотехнике и может использоваться в различных устройствах для ограничения амплитуды сигнала и формирования сигнала типа меандр.

Целью изобретения является уменьшение фазовой-погрешности.

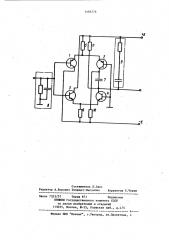

На чертеже представлена принципиальная электрическая схема усилителяограничителя.

Усилитель-ограничитель содержит первый и второй транзисторы 1 и 2 первого дифференциального каскада, третий и четвертый транзисторы 3 и 4 второго дифференциального каскада, генератор 5 тока первого дифференциального каскада, генератор 6 тока второго дифференциального каскада конденсатор 7, параллельную 8 и последовательную 9 РС -цепи, а также первый и второй резисторы 10 и 11.

Усилитель-ограничитель работает следующим образом.

При отсутствии входного сигнала транзисторы находятся в закрытом состоянии. При этом потенциал относительно общей шины обкладки конденсатора 7„ подключенной к коллектору второго транзистора 2, — отрицательньй, а обкладки данного конденсатора, подключенной к коллектору четвертого транзистора 4, — положительный.

При поступлении на вход усилителяограчнчителя синусоидального сигнала его положительный полупериод вызывает открывание второго транзистора 2, и конденсатор 7 разряжается через коллекторно-базовый переход второго транэисгора 2 и первый резистор 10.

Поскольку положительный полупериод входного сигнала вызывает смещение эмиттерно-базового перехода запертого четвертого транзистора 4 в обратном направлении, потенциал обкладки конденсатора 7, подключенной к коллектору четвертого транзистора 4, становится положительным, равным напряжению источника питания + Е, а потенцИал его второй обкладки становится равным нулю. Затем отрицательный полупериод входного сигнала приводит к резкому запиранию второго транзистора 2, смещению его. эмиттерно-базового перехода в обратном направлении н открыванию четвертого транзистора 4. При этом поочередное смещение эмиттерно-базовых переходов транзисторов 2 и 4, работающих в

16

40 режиме ограничения, приводит к нейтрализации влияния зарядовых емкостей, указанных переходов, на смещение переходов через ноль в выходном сигнале. В момент изменения полупериода положительной полярности, полупериодом отрицательной полярности (перехода .через ноль входного сигнала) конденсатор 7 оказывается включенным последовательно с зарядовой емкостью коллекторно-базового перехода запирающегося второго транзистора 2, и к коллектору четвертого транзистора 4 прикладывается напряжение положительной полярности, превышающее напряжение источника питания Е. Это приводит к ускорению переходного процесса, сопровождающего формирование фронтов выходного напряжения прямоугольной формы, и нейтрализации влияния паразитных зарядовых емкостей коллекторно-базовых переходов транзисторов, работающих в режиме ограничения, на выходной сигнал. В данном случае наличие зарядовых емкостей переходов транзисторов, приводящих к паразитному фазовому сдвигу выходного сигнала, не только нейтрализуется, но и выполняет положительную роль, энергия зарядовых емкостей используется для ускорения процесса открывания ограничивающих транзисторов.

Сигналы с выходов дифференциальных усилителей суммируются на резисторе последовательностей RC -цепи

9, что приводит к дальнейшему уменьшению паразитных зарядовых емкостей переходов транзисторов, а также к ослаблению несинфазных гармоник, ограниченных сигналов, которые могут появиться в случае недостаточной симметрии параметров элементов усилителя-ограничителя.

При работе усилителя-ограничите; ля в моменты переходов через ноль входного сигнала переходные процессы в транзисторах 2 и 4, возникающие при формировании фронтов выходного ограниченчого сигнала прямоугольной формы, вызывают их искажения паразитнымн колебаниями. Однако их влияние уменьшается благодаря наличию параллельной RC-цепи 8, конденсатор которой улучшает привязку без трэнзисторов к общей шине в моменты переходов через ноль входного сигнала

Составитель Л.Закс

Редактор А.Ворович ТехредС.Мигунова Корректор С.Черни

Заказ 7323/57 Тирам 87.1 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r.укгород, ул.Проектная, 4