Устройство для преобразования фурье

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее блок синхронизации , первьй выход которого подключен к первому установочному входу триггера, тактовому входу квантователя , первому входу первого элемента ИЛИ и первому входу формирователя адреса, первый выход которого подключен к управляющему входу коммутатора, выход которого подключен к первому информационному входу сумматора-вычитателя, выход которого подключен к информационному входу блока буферной памяти, информащюн- .ный выход которого является информационным выходом устройства и подключен к второму информационному входу сумматора-вычитателя, управляющий вход которого подключен к выходу сумматора по модулю два, первый и второй входы которого подключены соответственно к второму выходу формирователя адреса и выходу первого элемента ИЛИ, второй вход которого подключен к выходу знакового разряда регистра, информационный вход которого подключен к выходу квантователя, информационньйвход которого является информационным JJ:7.,,,; входом устройства, информационный выход регистра подключен к информационному входу преобразователя код частота , первый и второй выходы триггера подключены к первым входам соответственно первого и второго элементов И, группу элементов И, отличающееся тем, что, с целью упрощения устройства, оно содержит блок, памяти, второй элемент ИЛИ и дешифратор, выход старшего разряда которого подключен к входам обнуления первого и второго счетчиков, второму установочному входу триггера и входу сброса преобi разователя код - частота, выход ко (Л торого подключен к счетному входу второго счетчика, выход i-ro (i l,m; m - разрядность ) разряда которого подключен к первому входу 1-го элемента И группы, выход которого подключен к входу i-го разряда копа адреса блока памяти, выход j-ro ( j I ,к; к N/4; N- размер со СП преобразования )разряда, которого подключен к j-му информационному 00 ел входу коммутатора, второй выход блока синхронизации подключен к вторым 00 входам первого и второго элементов И, выходы которых подклточены соответственно к второму входу формирователя адреса и счетному входу первого счетчика, информационный выход которого подключен к входу дешифратора, j-й выход которого подключен к )-му входу второго элемента ИЛИ, выход которого подключен к управляющему входу блока памяти и вторым входам элементов И группы.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (Ц) (5D4 G 06 F IS 332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3741301/24-24 (22) 15.05.84 (46) 30. 11.85. Бюл. - 44. (72) В.И.Якименко, N.Á.Столбов, А.Ф.Бульбанюк и Ц.Б.Эпштей»н (53) 681.32(088.8) (56) Патент США И - 4138730, кл, G 06 F 15/332, опубл. 1977.

Авторское свидетельство СССР

Ф 1043663. кл. G Об Г 15/332, 1982. (54)(57) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ФУРЬЕ, содержащее блок синхронизации, первый выход которого под.ключен к первому установочному входу триггера, тактовому входу квантователя, первому входу первого элемента ИЛИ и первому входу формирователя адреса, первый выход которого подключен к управляющему входу коммутатора, выход которого подключен к первому информационному входу сумматора-вычитателя, выход которого подключен к информационному входу блока буферной памяти, информацион- . .ный выход которого является информационным выходом устройства и подключен к второму информационному входу сумматора-вычитателя, управляющий вход которого подключен к выходу сумматора по модулю два, первый и второй входы которого подключены соответственно к второму выходу формирователя адреса и выходу первого элемента ИЛИ, второй вход которого подключен к выходу знакового разряда регистра, информационный вход которого подключен к выходу квантователя, информационный вход которого является информационным входом устройства, информационный выход регистра подключен к информационному входу преобразователя код— частота, первый и второй выходы триггера подключены к первым входам соответственно первого и второго элементов И, группу элементов И, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит блок. памяти, второй элемент ИЛИ и дешифратор, выход старшего разряда которого подключен к входам обнуления первого и второго счетчиков, второму установочному входу триггера и входу сброса преобразователя код — частота, выход которого подключен к счетному входу второго счетчика, выход 1-го (i=l,m; m — разрядность ) разряда которого подключен к первому входу

1-ro элемента И группы, выход которого подключен к входу i-ro разряда кода адреса блока памяти, выход

j-го (1= I,к; к = N/4; N - размер преобразования ) разряда. которого подключен к 1-му инбормационному входу коммутатора, второй выход блока синхронизации подключен к вторым входам первого.и второго элементов

И, выходы которых подключены соответственно к второму входу формирователя адреса и счетному входу первого счетчика, информационный выход которого подключен к входу дешифратора, 1-й выход которого подключен к

j-му входу второго элемента ИЛИ, вь ход которого подключен к управляющему входу блока памяти и вторым входам элементов И группы.

1 l!

Изобретение относится к специали- " зированным средствам вычислительной техники, предназначенным для автоматизации анализа спектральных свойств случайных процессов в реальном масштабе времени, использования в системах распознавания, например, в биокибернетике, радиофизике.

Цель изобретения — упрощение устройства.

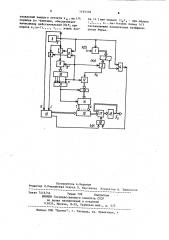

На чертеже приведена структурная схема предлагаемого устройства.

Фурье-преобразователь содержит квантователь 1, регистр 2 отсчета, преобразователь 3 код — частота, элемент ИЛИ 4, блок 5 синхронизации, триггер б, элементы И 7 и 8, счетчик

9, дешифратор 10, элемент ИЛИ II, счетчик 12, группу элементов И 13, блок 14 памяти, формирователь 15 адреса, коммутатор 16, сумматор-вычитатель 17, блок 18 буферной памяти и сумматор 19 по модулю два.

Устройство работает следующим образом, Перед началом вычислений все блоки установлены в нулевое состояние, а дешифратор 10 имеет к выходов и настроен таким образом, что на каждом

i-ом вьгсоде формируется импульс через интервал времени ЙТ; после импульса с предыдущего (i-1)-го выхода,.образуя ряд интервалов дТ;, пропорциональных приращениям синусной функции на первой четверти периода представления. При этом объем памяти блока 14 памяти должен составлять к = И/4 кодов (где 1- объем памяти блока 18 памяти ), Исследуемый случайный сигнал х(г) подается на вход квантователя 1 и по тактовым m импуabeaM с выхода блока

5 синхронизации преобразуется в дискретную форму х (mat). При получении первого отсчета х(1 М )он записывается в регистр 2 в виде модуля (х1) знака 8яп(х1): знаковый выход при этом подключается через элемент

ИЛИ 4 на вход сумматора 19 по модулю два, задавая знак второго слагаемого в усреднителе 17 = 1+(-1) — СЩ 1

, 1 где = 0 или 1, соответствующие положительному или отрицательному знаку Sgn(x ); С . — функция, счи- тываемая с блока !4 памяти.

Подключенный к входу преобразователя 3 код — частота код (х „1 преоб95358

6 . = Х(141) Sir—

7 1й

1-! В

55!

0 !

Разуется в лоток импульсов соответствующей частоты I „, которые подаются в счетчик !2.

Одновременно этот же (ю =1) импульс с выхода блока 5 синхронизации поступает на первый установочный вход триггера 6, устанавливая

oего в состояние, при котором через элемент И 7 поступают тактовые импульсы на вход счетчика 9, т.е. счетчики 9 и 12 одновременно начинают счет импульсов соответствующих потоков Рт и Г, . При достижении в счетчике 9 числа импульсов равного

g„, срабатывает дешифратор 10 по первому выходу: импульс с выхода элемента ИЛИ ll поступит на вторые входы группы элементов И 13 и на управляющий вход блока 14 памяти, осуществляя при этом соответственно считывание кода В; „ с выхода счетчика 12 и запись его в первую ячейку блока 14 памяти.

При дальнейшем счете импульсов счетчиком 9 дешифратор 10 срабатывает через интервалы времени пропорциональные изменению (приращению ) ординат синусной функции, и формирует импульсы последовательно на 2,3,..., к-ом выходах, которые через элемент ИЛИ 11 подаются на вторые входы группы элементов И 13.

При этом через соответствующие интервалы времени,„ с выхода счетчика 12 считывается код 8, 8„ ..., 9< >, который записйвается соответственно в 2 3 к-ю ячейку блока 14 памяти. Поскольку счетчик

12 непрерывно считает количество импульсов в потоке „ за указанные интервалы времени (частота F npo1 порциональна амплитуде отсчета х ), 1 в 1-х ячейках блока 14 памяти запоминаются коды 6,, пропорциональные произведению отсчета х„ на соответствующую i-ю выборку четверти периода синусной функции где В F — масштабный коэффициент, Сформированный на к-м выходе дешифратора 10 импульса поступает также на управляющие входы "Сброс" преобразователя 3 код — частота, а также счетчиков 9 и !2, а триггер 6 опрокидывается во второе состояние, при котором закрывается элемент И 7

-(а

8 =х e:052 lt((,„

1,la в„

25

35

3 1195 и открывается элемент И 8 для прохож- . дения тактовых импульсон в формирователь 15 адреса.

Так как для вычисления комплексных коэффициентов Фурье необходимо осуществить Sin-преобразование Фурье (,Х Г„) и ros-преобразование Фурье (Re F ), н блок 18 иэ блока 14 через коммутатор 16 необходимо считать коды 81, в определенной последователь- 10 ности: для йормирования ) шГ„ считываются коды 9 <, где e=0,1,2,..., 1, к...1,0,1,..., à для еГ „ — коды

9„, где щ=к- 1, т.е. коды считываются в последовательности =к, (к-l), (к-2),..., 1,0,1,... (к-l), к,..., что соответствует произведению:

Например, опрос при формировании

R F осуществляется следующим о6разом.

При первом цикле считывания кодов

91 (m 1) опрос выходов блока 14 памяти осуществляется с шагом аА=а1=1, т.е. опрашинаются выходы

1(m-к )=к, (к-1), (к-2 )..., и через блок 17 распределяются н ячейки =1,2,..., к= 1/4 блока 18. После записи кода в ячейку N/4 блока 18 в нем оказывается накопленной 1/4 периода функции RgFy 8,, после чего из формирователя 15 адреса поступает импульс на второй вход сумматора

19 по модулю дна, при этом в блоке !

7 устанавливается отрицательный знак Sp11 0 = — 1 (соответствующий отрицательной полунолне косннусной функции )и усреднение следующих кодов 9 п,, записываемых в ячейки

N/4 1(3 k /4 блока 18 памяти, осуществляется в соответствии с формулой:

358 4

Sgn х =(-1}q, с второго выхода регист ра 2 отсчета поступает через элемент

ИЛИ 4 на вход начальной установки знака в сумматоре 19 по модулю два (т.е. задавая операции "Сложение" или "Вычитание" в блоке 17 при первых N/4 тактах усреднения ). Одновременно с этим в преобразователе 3 код — частота формируются поток импульсов частоты Р2, пропорциональной амплитуде х(2 ), который поступает на счетный вход счетчика 12.

Импульс запуска щ = 2 с блока 5 синхронизации поступает также на перный вход триггера 6, опрокидывает его, устанавливая элемент И 7 в режим пропускания тактовых импульсов на счетный вход счетчика 9. Аналогично циклу rn =1 в блок 14 памяти с ныхода счетчика 12 считываются коды

92;, записываясь последовательно в

1,2,..., к-ю ячейки памяти.

Считывание кодон 8 2; при помощи формирователя 15 адреса осущестнляется при этом с шагом дAg=tn=2, т.е. опрашиваются выходы =к, (к-2 ),..., 2,0,2,... блока 14 памяти и результаты опроса через коммутатор 16 поступают н блок 17, в котором усредняются с результатами предыдущего цикла R

1,2,3... блока 18.

Коды адресов вычисляются в формирователе 15 адресов в соответствии с выражением:

Rg= (p — -вт); n =eR-le, р= 02 т, где р — номер перехода гармонической функции через нулевой уровень.

Закон изменения знаков в блоке 17 при вычислении Re Р описынается следуюшими соотношениями:

Яе F, = Re F m»„- —, 81

После и микрокоманд каждого m --го цикла опроса во всех N ячейках блока 18 будут накоплены результаты усреднения, после чего блоки Фурьепреобразователя подготовлены для

; осуществления преобразования (eRe +1 )-го цикла.

Так, при втором цикле (m =2 ) по импульсу с первого выхода блока 5 синхронизации в квантователе 1 формируется отсчет входного сигнала, который записывается в регистр 2 отсчета. Выделенный при этом знак предыдущий знак при: }pm}ь — +р- )1

Sge1 9 измененный знак }- }> - „.-,1.

Г и рт) Таким образом, после и-го цикла обработки входного сигнала в блоке

i8 накапливается сумма, описываемая выражением:

2m H

ReF<(e t)=ee, > (-eI Åå„ (e.ed) .

p=0 Вв1

Следовательно, опрос буферного блока 14 памяти, содержащего К про"

1195358

Составитель А.Варанов

Редактор Л.Пчелинская Техред Л. Мартяшова Корректор А. Зимокосов

Заказ 7416/54 Тираж 709 Подписное

ВНИИПИ Государственного-комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 изведений каждого отсчета хщ, на 1/4 периода Sin -функции, обеспечивает вычисление действительной (Re F> при опросе к,(к-1),..., 1,... ячеек бло/ ка 14 ) или мнимой (1щР» — при ойросе

1,2,..., к...4к= N ячеек блока 14 ) составляющих комплексных коэффициентов Фурье.