Аналого-цифровое устройство задержки

Иллюстрации

Показать всеРеферат

АНАЛОГО-ЦИФРОВОЕ УСТРОЙСТВО ЗАДЕРЖКИ, содержащее масштабный блок, вход которого является входом устройства, п-разрядный аналого-цифровой преобразователь, вход которо го соединен с выходом масштабного блока, п регистров сдвига, входы которых соединены с выходами аналого-цифрового преобразователя, генератор тактовых импульсов, подключенный выходом к тактовым входам регистров сдвига, цифроаналоговый преобразователь, отличающееся тем, что, с целью расширения области .применения за счет возможности получения плавной перестройки времени задержки по закону, близкому к линейному, и возможности изменения скорости перестройки задержки, в него введены п мультиплексоров, распределитель импульсов и делитель частоты с переменным коэффициентом деления, вход которого соединен с выходом генератора тактовых импульсов , а выход соединен с входом распределителя импульсов, выход которого соединен с управляющими входами мультиплексоров, информационные выходы которых соединены с разрядными вькодами регистров сдвига, а л выход мультиплексоров подключены к входам цифроаналогового преобразователя , выход которого является выходом устройства. СО сд 4 00 4

„„SU„„1195434 А

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК(5l) 4 " 03 К 5/13

М

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ р

ОПИСАНИЕ ИЗОБРЕТЕНИЯ " !3

М ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3702352/24-21 (22) 16.02.84 (46) 30.11.85. Бюл. У 44 (72) А;Т.Муравьев, В.П.Полященко и Ю.С.Иванченко (53) 621, 374 (088. 8) (56) Авторское свидетельство СССР .У 879758, кл. Н 03 К 5/13, 15.06.79. (54)(57) AHAJIOI 0-ЦИФРОВОЕ УСТРОЙСТВО ЗАДЕРЖКИ, содержащее масштабный блок, вход которого является входом устройства, п-разрядный аналого-циф ровой преобразователь, вход которого соединен с выходом масштабного блока, и регистров сдвига, входы которых соединены с выходами аналого-цифрового преобразователя, генератор тактовых импульсов, подключенный выходом к тактовым входам регистров сдвига, цифроаналоговый преобразователь, о т л и ч а ю щ е— еся тем,,что, с целью расширения области .применения sa счет возможности получения главной перестройки времени задержки по закону, близкому к линейному, и возможности изменения скорости перестройки задержки, в него введены и мультиплексоров, распределитель импульсов и делитель частоты с переменным коэффициентом деления, вход которого соединен с выходом генератора тактовых импульсов, а выход соединен с входом распределителя импульсов, выход которого соединен с управляющими входами мультиплексоров, информационные выходы которых соединены с разрядными выходами регистров сдвига, а выход мультиплексоров подключены к входам цифроаналогового преобразователя, выход которого является выходом устройства.

1195434

Изобретение относится к радиотех- нике и может быть использовано в f устройствах для формирования и обработки сигналов, при построении автоматических корреляторов и устройств для вычисления свертки функцийi

Целью изобретения является расширение области применения аналогоцифрового устройства задержки за счет возможности получения плавной перестройки времени задержки по за кону, близкому к линейному, и возможности изменения скорости перестройки времени задержки.

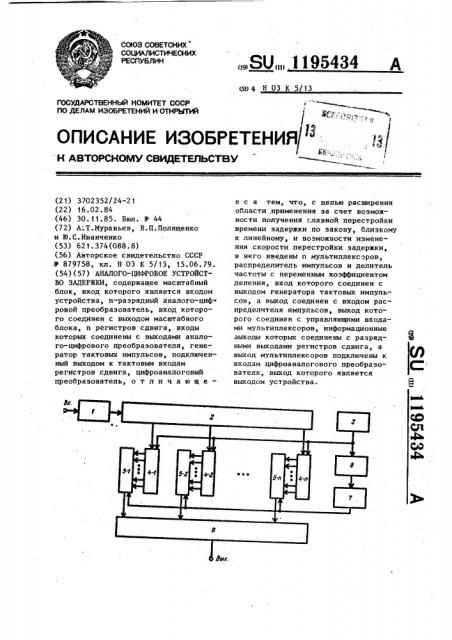

На чертеже представлена структурная схема аналого-цифрового устройства задержки.

Аналого-цифровое устройство задержки содержит масштабный блок 1, аналого-цифровой преобразователь (АЦП) 2, генератор 3 тактовых импульсов (ГТИ), и регистров 4-1-4-и сдвига, п мультиплексоров 5-1-5-и делитель 6 частоты с переменным коэффициентом деления (ДПКД), распределитель 7 импульсов и цифроаналоговый преобразователь (ЦАП) 8.

Вход масштабного блока 1 является входом устройства, а его выход подключен к входу АЦП 2. Выходы АЦП 2 подключены к входам регистров

4-1-4-п сдвига, тактовые входы которьп соединены с выходом тактового генератора 3, а разрядные выходы— с информационными входами мультиплек. соров 5-1-5-п. Вход ДПКД6 подключен к выходу тактового генератора

3, а выход — к входу распределителя

7 импульсов, выходы которого соединены с управляющими входами мультиплексоров 5-1-5-11, Выходы мультиплексоров 5-1-5-и подключены к входам ЦАП 8, выход которого является выходом устройства., Масштабный блок 1 представляет собой усилитель с автоматической регулировкой усиления, в качестве которого можно гспользовать например микросхемы 235 УРЗ и 235 УР9.

АЦП 2 представляет собой типовой блок и может быть выполнен например на интегральной микросхеме К 572 ПВ

1А-В.

Генератор 3 тактовых импульсов выполнен по схеме автоколебательно-. го мультивибратора с кварцевой ста10

55 билизацией частоты на микросхеме

155 ЛАЗ.

ДПКД 6 выполнен на микросхеме

155 ИЕ8, коэффициент деления может устанавливаться, например, вручную при помощи переключателей.

ЦАП 8 выполнен на микросхеме К 575 ПА1А.

Мультиплексор 5 также может представлять собой типовой блок, например, на интегральной микросхеме

155КП5.

Распределитель 7 импульсов может быть выполнен, например, в виде двоичного счетчика, разрядные выходы которого подключены к управляющим входам мультиплексоров 5-1-5-п.

Аналого-цифровое устройство задержки работает следующим образом.

Исследуемый аналоговый сигнал, подлежащий задержке, поступает на масштабный блок 1, где он усиливается по амплитуде и подается на вход

АЦП 2, который преобразует аналоговый сигнал в разрядный цифровой сигнал, представленный в параллельном коде.

Далее цифровой сигнал с выходов

АЦП 2 подается на входы регистров

4- 1-4-и сдвига, где происходит временная задержка исследуемого сигнала за счет его записи и сдвига в разрядах регистров 4-1-4-и с помощью импульсов, поступающих от генератора 3 тактовых импульсов.

Величина задержки в каждый момент времени определяется номером разрядов регистров, с которого производится считывание информации и который, в свою очередь, соответствует коду, поступающему на управляющие входы мультиплексоров 5-1-5-п с выхода распределителя 7 импульсов.

При поступлении импульсов на вход распределителя 7 импульсов с .

ДПКД .6 изменяется состояние сигналов на его выходах и соответственно на управляющих входах мультиплексоров 5-1-5-и. Вр.-:.мя задержки при этом изменяется дискретно, величина дискрета задержки определяется временем задержки одного разряда регистра. Время перестройки линии задержки от О до с „ определяется коэффициентом деления ДКПД 6. Изменение времени задержки аппроксимируется при этом линейным законом.

При необходимости время задержки такого устройства можно изменять по произвольному закону, который

195434

Составитель А.Титов

Редактор А.Лежнина Техред р.йеце . Корректор E.Снрохман

Заказ 7422/57

Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР ло делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4 э 1 задается распределителем 7 импульсов, в качестве которого может быть использована жесткая логика, ЦВМ или клавишное наборное поле. Скорость перестройки времени задержки определяется частотой следования импульсов, подаваемых на вход распреде" лителя 7 импульсов, и может изменяться в широких пределах с помощью изменения коэффициента де-, ления ДПКД 6. С выходов. мультиплексоров 5- I- 5 — n задержанный цифровой сигнал поступает на входы ЦАП 8, с выхода которого снимается задержанный аналоговый сигнал.