Устройство для вычисления квадратного корня из суммы квадратов чисел

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (59 4 С 06 Р 7 544 7 552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3763139/24-24 (22) 29.06.84 (46) 07.12.85. Бюл. 9 45 (72) Е.Я.Ваврук, А.Н.Елагин, В.E.Òèìîôååíêî и А.А.Филимонов (53) 681.325(088.8) (56) Авторское свидетельство СССР .9 1024912, кл. G 06 F 7/552, 1982.

Авторское свидетельство СССР

М 1027719э кл. С 06 F 7/552ю 1982 ° (54) (57) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ

КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ЧИСЕЛ, содержащее первый и второй регистры операндов, первый и второй коммутаторы, регистр суммы, распределитель импульсов, сумматор, первый, второй и третий выходы распределителя импульсов подключены к входам стробирования записи первого и второго регистров операндов, к управляющему входу первого коммутатора и к входу стробирования записи регистра суммы соответственно, выход регистра суммы подключен к первому информационному входу первого коммутатора и является выходом результата устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства, за счет воэможности вычисления выражения

„ + (+ х ;, в него введены третий

4 1 э Ф регистр операнда, блок приоритета, вычитатель, схема сравнения, вход стробирования записи третьего регистра операнда подключен к первому входу распределителя импульсов, выходы первого, второго н третьего регистров операндов подключены к первому, второму и третьему входам блока приоритета, первый,. второй и третий выходы которого подключены к второму, третьему и четвертому информационным входам первого коммутатора соответственно, первый выхбд которого подключен со смещением на один разряд в сторону младших разрядов к входу первого операнда сумматора, выход которого подключен к первому вхо-, ду схемы сравнения и к первому информационному входу второго коммутатора, выход которого подключен к информационному входу регистра суммы, второй выход первого коммутатора подключен к второму входу схемы сравнения, к второму информационному входу второго коммутатора, к входу уменьшаемого вычитателя и со смещением на три разряда в сторону младших разря-. дов — к входу вычитаемого вычитателя, выход которого подключен к входу второго операнда сумматора, выход "Меньtl ше схемы сравнения подключен к управляющему входу второго коммутатора. происходит в два этапа. этап вычисления z< = x„+ х

П этап вычисления z =/x + Хс;

8 2/ /

7 1 макс при выполнении условия /х„/) /х />/х /.

Как известно, ошибка вычисления

z„- E (37, т.е. ошибка вычисления

z — 5 6Х.

Устройство работает следующим образом.

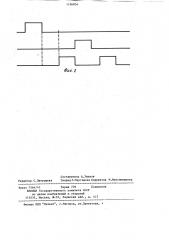

По начальному пуску (цепи начальной установки на фиг. 1, не приведены) вырабатывается тактовый импульс

Т1 (фиг.2), по переднему фронту которого осуществляется запись операндов в регистры 1-3. Блок 5 построен так, что на первых выходах получаем большее число, на вторых - среднее, на третьих — меньшее. Для описания дальнейшей работы примем, что

/х„/7 /х / 7 /x3/, т.е. на первом выходе блока 5 - x> на третьем—

На втором выходе распределителя

4 импульсов — уровень логического нуля, что свидетельствует о том, что на выход первого коммутатора 6 проходит информация с его второго и третьего информационных входов, т.е

1 11968

Изобретение относится к цифровой вычислительной технике и предназначено для использования в специализированных вычислительных устройствах.

Цель изобретения — расширение

S функциональных» возможностей за счет обесцечениям возможности вычисления ,I квадратного корня из суммы. квадратов, рех чисел z = х + х + х".

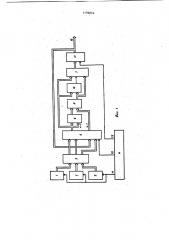

На фиг.1 приведена с»труктурная схема устройства; на. фиг. 2 — времен.ная диаграмма работы распределителя импульсов.

Устройство содержит первый 1, второй 2, третий 3 регистры операнда, распределитель 4 импульсов, блок 5 приоритета, первый 6 и второй 7 коммутаторы, вычитатель 8, сумматор 9, схему 10 сравнения, регистр 11 суммыр выход 12.

Сущность изобретения заключается в том, что вычисление функции z

54 2 на первом выходе первого коммутатора значение /х /, на втором /х„/.

Значение /х / поступает на вход. уменьшаемого вычитателя 8. На вход вычитаемого вычитателя 8 поступает значение /х„/, сдвинутое на три двоичных разряда в сторону младших разрядов, т.е. — /х„/ (сдвиг органи1 зован монтажно).

На выходе вычитателя 8 получаем

7 значение 8 /х„/, которое поступает на сумматор 9, на вход второго операнда которого поступает значение

/х / ° На Выходе сумматора

7 1

9: /х „/ + /х /. Это значе8 ние поступает на первый вход схемы

10 сравнения, на второй вход кото-. рой поступает значение /х„/. Если

/х /+ — /х / (/х / то схема

7 1

2, и

10 сравнения вырабатывает сигнал управления вторым коммутатором, который разрешает прохождение на его выход значения /х„/; в противном

7 1 случае /х /+ — /х /. Одно или

8 1, 2 другое значение по передненму фронту

Т3 (фиг.2) распределителя 4 импульсов записывается в регистр 11 суммы (значение z ) .

После этого распределитель 4 импульсов формирует сигнал Т2 (фиг.2), по которому первый и четвертый информационные входы коммутатора 6 подключаются на его два выхода, т.е. .на первом выходе первого коммутатора

6 — /х /, на втором — z

Дальнейшая работа происходит аналогично описанному, т.е. на выходе

7 вычитателя 8 : z на выходе

7 1 сумматора 9 : — z + †/х /

8 " 2 на выходе второго коммутатора 7— значение

7 в=ма с IEg в + 2 / g/ которое по переднему фронту второго импульса ТЗ записывается на регистр

11 суммы и поступает на выход 12 устройства. На этом устройство прекращает работу.

Дальнейшая работа устройства возобновляется по приходу сигнала

"Начальный пуск".

1196854

1196854

Составитель А. Ушаков

Техред Л.Мартяшова Корректор М.Максимишинец

Редактор С.Патрушева

Филиал ППП "Патент", r.Ужгород, ул.Проектная, 4

Заказ 7564/47 Тираж 709 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5