Устройство для формирования адресов

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ, содержащее три регистра, три блока элементов И-ИЛИ, сумматор адреса , дешифратор и элемент И, выходы/ первого и второго регистров соединены соответственно с первыми входами первого и второго блоков элементов И-ШШ, выходы которых с.оединены .с входами сумматора адреса, отличающееся тем, что, с целью расширения функциональных возможностей , за счет формирования адресов элементов матрицы при произвольном шаге, в него введены два счетчика, восемь элементов И-ИЛИ, пять триггеров , два регистра и дешифратор, причем вход Ответ ОЗУ устройства соединен с первыми входами с первого по четвертый элементов И-ШШ и с входом первого триггера, вход Начальная установка устройства - с вторым входом третьего элемента ИИЛИ , вход записи количества по первому иэмерению матрицы устройства с входом записи третьего регистра, вход записи количества по второму измерению матрицы устройства - с вторым входом четвертого элемента И-ИЛИ и с первым входом режима работы первого счетчика, вход записи начального адреса устройства - с вторым входом первого элемента И-ИЛИ, с первым входом пятого элемента ИИЛИ и с входом второго триггера, вход записи шага по первому измерению матрицы устройства - с входом записи второго регистра, вход записи шага по второму измерению матрицы устройства - с вторым входом пятого .элемента И-ШШ и с единичным входом третьего триггера, выход четвертого элемента И-ИЛИ - с вторым входом режима работы первого счетчика, выход первого элемента И-ШШ -с вторым входом второго элемента И, четвертого элемента И-ИЛИ и с первым входом режима работы второго счетчика, выход второго элемента И-ИЛИ - с вторым (Л входом режима работы второго счетчика , выход третьего элемента с нулевым входом третьего.триггера, выход первого дешифратора - с третьим входом третьего элемента И-ИЛИ, выход второго дешифратора - с входом четвертого триггера, с четверсо а тым входом третьего элемента И-ИЛИ, с третьими входами.первого и чет00 О5 вертого элементов И-ИЛИ, выход третьего триггера является выходом запрещения обращения в ОЗУ устрой ства, выход второго триггера соединен с первым входом элемента И, с первым входом шестого элемента ИИПИ , с вторым входом второго блока элементов И-ИЛИ, выход первого триггера - с вторым входом элемента И, с первым входом седьмого элемента И-ИЛИ, выход второго триггера - с входом пятого триггера, с первым входом восьмого элемента И-ИЛИ, с первым входом третьего блока элементов И-ИЛИ, выход пятого триггера

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„! 196867 (5ц4G06F936

ЗСЕСОВ, НЮЯ ц "." ."".. 13

ИЬ МОТР А, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ . (21) 3747408/24-24 (22) 04.06.84 (46) 07.12.85. Вюл. У 45 (72) Ю.С.Варакин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Н - 924709, кл. G 06 F 9/36, 1982.

Авторское свидетельство СССРР 440880, кл. G 06 F 9/36, 1972. (54) (57) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

АДРЕСОВ, содержащее три регистра, три блока элементов И-ИЛИ, сумматор адреса, дешифратор и элемент И, выходы первого и второго регистров соединены соответственно с первыми входами первого и второго блоков элементов

И-ИПИ, выходы которых соединены,с входами сумматора адреса, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет формирования адресов элементов матрицы при произвольном шаге, в него введены два счетчика, восемь элементов И-ИЛИ, пять триггеров, два регистра и дешифратор, .причем вход "Ответ ОЗУ" устройства соединен с первыми входами с первого по четвертый элементов И-ИЛИ и с входом первого триггера, вход "Начальная установка" устройства — с вторым входом третьего элемента ИИЛИ, вход записи количества по первому измерению матрицы устройства— с входом записи третьего регистра, вход записи количества по второму измерению матрицы устройства — с вторым входом четвертого элемента

И-ИЛИ и с первым входом режима работы первого счетчика, вход записи начального адреса устройства †с вторым. входом первого элемента И-ИЛИ э с первым входом пятого элемента ИИЛИ и с входом второго триггера, вход записи шага по первому измерению матрицы устройства — с .входом записи второго регистра, вход записи шага по второму измерению матрицы устройства — с вторым входом пятого .элемента И-ИЛИ и с единичным входом третьего триггера, выход четвертого элемента И-ИЛИ вЂ” с вторый входом режима работы первого счетчика, выход первого элемента И-ИЛИ вЂ” с вторым входом второго элемента И, четвертого элемента И-ИЛИ и с первым входом режима работы второго счетчика, выход Е

C второго элемента И-ИЛИ вЂ” с вторым входом режима работы второго счетчика, выход третьего элемента И-ИЛИ вЂ” . с нулевым входом третьего. триггера, . выход первого дешифратора — с треть- Я им входом третьего элемента И-ИЛИ

Э выход второго дешифратора — с .входом четвертого триггера, с четвертым входом третьего элемента И-ИЛИ, с третьими входами первого и чет- ф вертого элементов И-ИЛИ, выход QO третьего триггера является выходом ф запрещения обращения в ОЗУ устрой- . ства, выход второго триггера соединен с первым входом элемента И, с первым входом шестого элемента ИИЛИ, с вторым входом второго блока элементов И-ИЛИ, выход первого триггера — с вторым входом элемента И, с первым вхбдом седьмого элемента

И-ИЛИ, выход второго триггера — с входом пятого триггера, с первым входом восьмого элемента И-ИЛИ, с первым входом третьего блока элементов И-ИЛИ, выход пятого триггера—

1196867 с вторым входом шестого элемента

И-ИЛИ и с вторым входом седьмого элемента И-ИЛИ, выход элемента И— с вторыми входами восьмого и третьего блоков элементов И-ИЛИ, выход восьмого элемента И-ИЛИ вЂ” с входом записи первого регистра, выход седьмого элемента И-ИЛИ вЂ” с входом запиСи четвертого регистра, выход пятого элемента И-ИЛИ вЂ” с входом записи пятого регистра, прямой выход шестого элемента И-ИЛИ вЂ” с вторым входом блока элементов И ИЛИ и с третьим входом второго блока элементов И-ИЛИ, инверсный выход шестого элемента И-ИЛИ вЂ” с третьим входом первого блока элементов И-ИЛИ-, информационный вход устройства — с информационными входами первого счетчика, второго, третьего и пятого регистров, выход первого регистра—

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных процессорах, выполняющих циклические программы, в частности, адресацию операндов, представляющих собой матрицы, содержащие строк по элементов в строке, причем элементы в строке отличаются адресами на величину, называемую шагом по первому измерению (Ш1), а адреса начала строк отличаются на величину, называемую шагом по второму измерению (Ш2), при этом j есть количество по первому измерению (KI), a j — количество по второму измерению (К2).

Цель изобретения — расширение функциональных возможностей устройства за счет формирования адресов элементов матрицы при произвольном шаге.

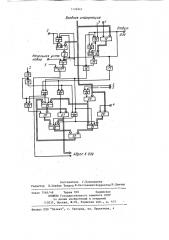

На.чертеже приведена функциональ- ная схема предлагаемого устройства.

Устройство содержит управляющие входы 1-5, четвертый элемент. И-ИЛИ

6, первый счетчик 7, первый дешифратор 8, третий элемент И-ИЛИ 9, третий триггер 10, первый элемент ИИЛИ 11, третий регистр 12, второй элемент И-ИЛИ 13, второй счетчик

14, второй дешифратор 15, первый с информационным входом второго счетчика, выход которого соединен с входом второго дешифратора,выход первого счетчика соединен с входом первого дешифратора, выход лятого регистра — с третьим входом третьего блока элементов И-ИЛИ и с четвертым входом второго блока элементов И-ИЛИ выход третьего блока элементов ИИЛИ вЂ” с информационным входом первого регистра, выход сумматора адреса — с-информационным входом четвертого регистра и с четвертым входом третьего блока элементов И-ИЛИ, выход четвертого регистра — с четвертым входом первого блока элементов

И-ИЛИ и является выходом адреса устройства, выход третьего элемента И вЂ” ИЛИ соединен с нулевым входом третьего триггера.

16, четвертый 17, второй 18, пятый

19 триггеры, элемент И 20, седьмой 21, пятый 22 и восьмой 23 элементы И-ИЛИ, третий блок элементов ИИЛИ 24, пятый 25, первый 26 и четвертый 27 регистры, шестой элемент ИИЛИ 28, второй регистр 29, первый

30 и второй 31 блоки элементов И10 ,ИЛИ и сумматор 32 адреса. При этом два счетчика 7 и 14 представляют собой микросхемы серии 100, у которых V è Ч, — управляющие входы.

При V = V< = 1 происходит прием входной информации в: счетчик. При

V< = 1 и V =0 счетчик работает на вычитание единицы из содержащейся в нем информации в каждый момент поступления импульса синхронизации.

При V, = Ч, 0 содержимое счет20 чика блокируется.

Устройство формирования адресов работает следующим образом.

Пусть необходимо сформировать адреса матрицы, у которой начальный

25 адрес (А„ ) равен 2, К1 равно 8, К2 равно 3, Ш1 равен 2, Ш2. равен 17, т.е. адреса элементов матрицы должны иметь следующее значение:

2 4 6 8 10 12 14 16

ЗО 19 21 23 25 27 29 31 33

36 38 40 42 44 46 48,.50

1196867

Перед началом выполнения в процесс соре операций на вход устройства подается сигнал "Начальная установка", .который устанавливает на выходе триггера 10 нулевой сигнал, запрещающий обращение в ОЗУ.

Цо управляющему сигналу "1" на регистр 12 принимается К1 = 8. По управляющему сигналу "2-" на счетчик 7 при- 1О нимается К2=3 ° По управляющему сиг. налу "3" на регистр 25 принимается

А„=2, который затем через блок элементов И-ИЛИ 24 принимается в регистр

26 по управляющему сигналу с триггера 18.

По управляющему сигналу "4" на регистр 29 принимается Ш1=2.

По управляющему сигналу "5" на регистр 25 принимается Ш2 =17 и устанавливается в единичное состояние выход триггера 10.К этому времени начальный адрес „ из регистра 26 через блок элементов И-ИЛИ 30 по управляющему сигналу с прямого выхода эле- 25 мента И-ИЛИ 28 поступает на вход сумматора 32 адреса. Блок элементов

И-ИЛИ 31 в это время заблокирован нулевыми сигналами с инверсного выхода элемента И-ИЛИ 28 и триггера 16 по30 этому на выходе сумматора 32 формируется значение, равное А„ . Далее содержимое сумматора, т.е. Д„, переписывается в регистр 27 по управляющему сигналу с элемента И-ИЛИ 21. С регистра 27 адреса А поступает на вход

ОЗУ, а также на вход сумматора 32 через блок элементов И-ИЛИ 30 по управляющему сигналу с инверсного выхода элемента И-ИЛИ 28. Одновременно на сумматор 32 подается содержимое ре- 40 гистра 29 через блок элементов И-ИЛИ

31 по управляющему сигналу с инверсного выхода элемента И-ИЛИ 28 ° Таким образом на сумматоре 32 готовится следующий адрес . A„ + Ш1 =4.

По сигналу "Ответ ОЗУ" устанавливается в единичное состояние выход триггера 17,по управляющему сигналу

4 с элемента И-ИЛИ 21 на регистр 27 записывается новый адрес и начинает формироваться следующий.

С каждым приходом сигнала "Ответ

ОЗУ" содержимое счетчика 14 уменьшается на единицу, а в ОЗУ поступают адреса, равные 2,4,6,8, 10; 12,14 и 16.

Когда содержимое счетчика 14 становится равным единице, дешифратор 15 сформировывает сигнал, по которому устанавливается в единичное состояние выход триггера 16,благодаря чему через блок элементов И-ИЛИ 30 на пер- вый вход сумматора 32 поступает .=2,через блок. элементов И-ИЛИ 31 на второй вход сумматора 32 поступает Ш2=17, а на выходе сумматора сформируется адрес, равный 19, т.е. адрес начала следующей строки.

С приходом сигнала "Ответ ОЗУ" содержимое сумматора 32 записывается в регистр 26 по управляющему сигналу с элемента И 20 и в регистр

27, в результате чего адрес первого элемента второй строки поступает на вход ОЗУ, в счетчик 14 вновь записывается содержимое регистра 12, т.е.

К1 .=8, счетчик 7 уменьшается на единицу и процесс формирования адресов для второй строки элементов матрйцы повторяется. Когда начинают формироваться адреса для третьей строки элементов матрицы, содержимое счетчика 7 становится равным единице.

При формировании последнего адреса третьей строки элементов матрицы счетчик 14 также становится равньм единице. Таким образом, на элемент И-ИЛИ

9 с дешифратора 8 и 15 поступают единичные сигналы,а с приходом сигнала "Ответ ОЗУ" на выходе элемента

И-ИЛИ 9 формируется единичный сигнал, устанавливающий триггер 10 в нулевое состояние. Причем сигнал с выхода триггера 10 запрещает прием адресов в ОЗУ и служит сигналом окончания формирования адресов для данной матрицы.

1196867

Жо0ная инцзормация

Составитель Г.Пономарева .

Редактор И.Дербак Техред Ж.Кастелевич Корректор М.Лемчик

Заказ 7565/48 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4