Устройство приоритета

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ПРИОРИТЕТА, содержащее элемент И, элемент ИЛИ,два регистра, группу элементов ИЛИ, группу элементов И, при этом единичные выходы первого регистра соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с ответным входом устройства, выходы четных элементов И группы соединены с первыми входами следующих нечетного и четного элементов И группы,выходы нечетных элементов И группы являются выходами устрой ,ства, отличающее с я тем, что, с целью сокращения оборудования , оно содержит элемент задержки, причем каждый вход запроса устройства канала соединен с синхронизирующим входом одноименного разряда первого регистра, информационные входы которого соединены с входом логичес-кой единицы устройства, входы сброса первого регистра соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых соединены с входом сброса устройства и с входами сброса второго, регистра, единичные выходы первого регистра соединены с информационными Ьходами второго регистра, синхронизирующие входы второго регистрасоединены с выходом элемента И, с соответствующим входом элемента ИЛИ и входом элемента задержки, выход которого сл соединен с первыми входами первого и второго элементов И группы, вторые входы нечетных элементов И группы соединены с выходами соответствующих разрядов второго регистра,вторые входы четных элементов И группы соединены инверсными выходами соотю ветствующих разрядов второго регистО ) ра, выходы устройства соединены с 00 вторыми входами одноименных элеменР со тов ИЛИ группы.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (ll) (5D 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3769925/24-24 (22) 06.07.84 (46) 07. 12.85, Бюл. У 45 (72) А.В.Гвоздев,Е.Г.Мазур и Е.П.Пархоменко (53) 681.325(088.8) (56) Авторское свидетельство СССР 81-1260,. кл. G 06 F 9/46, 1979.

Авторское свидетельство СССР

Ф 811256, кл. G 06 F 9/46, 1982. (54)(57) УСТРОЙСТВО ПРИОРИТЕТА, содержащее элемент И, элемент ИЛИ,два регистра, группу элементов ИЛИ, группу элементов И, при этом единичные выходы первого регистра соединены с входами элемента ИЛИ, выход которого соединен с первым входом элемента И, второй вход которого соединен с ответным входом устройства, выходы четных элементов И группы соединены с первыми входами следующих нечетного и четного элементов И группы>выходы нечетных элементов

И группы являются выходами устрой,ства, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, оно содержит элемент задержки, причем каждый вход запроса устройства канала соединен с синхрониэирующим входом одноименного разряда первого регистра, информационные входы которого соединены с входом логичес-. кой единицы устройства, входы сброса первого регистра соединены с выходами соответствующих элементов ИЛИ группы, первые входы которых соединены с входом сброса устройства и с входами сброса второго. регистра, единичные выходы первого регистра соединены с информационными входами второго регистра, синхронизирующие входы второго регистра соединены с выходом элемента И, с соответствующим входом элемента ИЛИ и входом элемента задержки, выход которого соединен с первыми входами первого и второго элементов И группы, вторые входы нечетных элементов И группы соединены с выходами соответствующих разрядов второго регистра,вторые входы четных. элементов И группы соединены инверсными выходами соответствующих разрядов второго регистра, выходы устройства соединены с вторыми входами одноименных элементов ИЛИ.группы.

1196869

1О

25

35

Изобретение относится к вычислительной технике в частности к уст ройствам управления различными объектами в условиях поступления множества заявок на обслуживание.

Цель изобретения — сокращение оборудования.

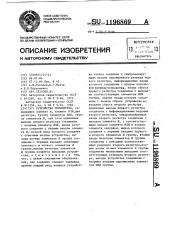

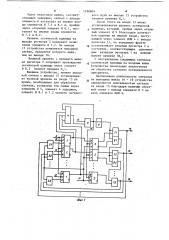

На фиг.1 представлена функциональная схема устройства;,на фиг.2 — временная диаграмма его работы.

Устройство приоритета содержит регистры 1 и 2, элементы HJIH 3.1—

3.3 и 4, элемент И 5, элемент 6 задержки, элементы И 7.1-7.3 и 8.18.2, вход 9 логической единицы устройства, входы 10-12 запросов устройства, ответный вход 13 устройства выходы 14-16, вход 17 сброса устройства, синхронизирующий вход 18 ре-. гистра 2.

Устройство работает следующим образом.

В исходном положении регистры

1 и 2 находятся в нулевом состоянии.

На выходах 14-16 устройства присутствуют нулевые сигналы. На входе 9 постоянно присутствует уровень. логической единицы. На входе 13 установлен уровень логической единицы, соответствующий готовности внешнего устройства к приему и обработке выходных сигналов устройства. Этот уровень подготавливает к включению элемент И 5. С нулевых выходов регистра 2 уровни логической единицы подготавливают к включению элементы И 8. На временной диаграмме это состояние устройства показано до момента времени M .

Пусть в момент времени М на входах 10 ы 12 одновременно появятся входные сигналы с уровнем логической единицы. Благодаря наличию логической единицы на входе 9 по переднему фронту входного сигнала устано вятся в единичное состояние соответствующие разряды регистра 1 (момент времени М ). При этом на выходе элемента ИЛИ 4 установится единичный уровень, который откроет элемент И

5. Сигнал логической единицы с выхо-, да элемента И 5 по переднему фронту установит соответствующие разряды регистров 2 в единичное состояние.

Одновременно сигнал с выхода элемента И 5 поступает на элемент 6 задержки и на вход элемента ИЛИ 4 ° Через время, соответствующее задержке, сигнал логической единицы поступает на первые входы элементов И 7.1 и

8.1. Благодаря тому, что второй вход элемента И 7.1 открыт уровнем.логической единицы с единичного выхода соответствующего разряда регистра 2, а элемент И 8.1 закрыт логическим нулем с нулевого выхода этого разряда, на выходе 14 устройства появляется выходной сигнал (момент времени M„), который переводит соответствующий разряд регистра 1 в нуль.

На остальных выходах 15-16 устройства будет присутствовать уровень логического нуля.

Внешнее устройство, приняв сигнал логической единицы с выхода

14 устройства, устанавливает нулевой уровень на входе 13 на время, необходимое для его обработки.

Нулевой уровень на входе 13 закрывает элемент И 5 и,соответственно, пройдя через элемент 6 задержки закрывает элемент И 7.1. На выходе

14 устройства устанавливается нулевой уровень (момент времени M ).

После обработки выходного. сигнала внешнее устройство вновь устанавливает уровень логической единицы на входе 13 (момент времени М ).

Если за промежуток времени от

М, до H поступит входной сигнал, например, на вход 11, то он по переднему фронту установыт,соответствующий разряд регистра 1 в едичное состояние. Элемент И 5 подготовлен к включению по своему первому входу благодаря поступающей через элемент ИЛИ 4 логической единице с выхоДов регистра 1.

Уровень логической единицы на входе 13 открывает элемент И 5 и по переднему фронту устанавливает разряды регистра 2 в состояние, соответствующее одноименным разрядам регистра 1 на данный момент времени (М ).

Одновременно сигнал с выхода элемента И 5 поступает на вход элемента 6 задержки и на вход элемента ИЛИ 4. Нулевой уровень на выходе регистра 2 закрывает элемент

И 7.1, а логическая единица с нулевого выхода этого. регистра подготавливает к включению элемент И 8.1. по второму входу. Время задержки на элементе 6 должно быть больше времени переключения регистра 2.

Через некоторое время, соответствующее задержке, сигнал с выхода элемента 6 поступает на первые входы элементов И 7.1 и 8.1 и, пройдя через открытый элемент И 8.1, поступает на первые входы элементов

И 7.2 и 8.2.

Уровень логической единицы на выходе регистра 2 разрешает включение элемента И 7.2. На выходе

15 устройства появляется выходной сигнал, приоритет которого выше, чем на выходе 16, Нулевой уровень с нулевого выхода регистра 2 запрещает прохождение логической единицы через элемент

И 8.2 (момент времени M„).

Внешнее устройство, приняв выходной сигнал с выхода 15 устанавливает нулевой ровень на входе 13 на время, необходимое для обработки сигнала,. установив тем самым через элементы И 5, элемент 6 задержки, элемент И 8. 1 и 7.2 уровень логичес96869 4 кого нуля на выходе 15 устройства (момент времени M,).

После этого на входе 13 вновь устанавливается уровень логической единицы, который, пройдя через открытый элемент И 5 (благодаря логической единице на первом входе, поступающей через элемент ИЛИ 4 с выхода регистра 1), по переднему фронту устанавливает разряды регистра 2 в состояние, соответствующее одноименным разрядам регистра 1 на данный момент времени (И ).

С поступлением следующих сигналов логической единицы на входные шины устройства происходит аналогичная их обработка согласно установленного приоритета.

Необходимая длительность сигналов на выходных шинах 14 — 16 устройства определяется длительностью сигнала на входе 13 благодаря наличию обратной связи с выхода элемента И 5 на вход элемента ИЛИ 4.

1196869

/"/ м ю и мц м м м м и .

Фиг. 2

Составитель M.Êóäðÿøåâ

Редактор А.Шишкина Техред Л.Мартяшова КорректорМ.Максимишинец

Заказ 7565/48 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4