Устройство для вывода информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ВЬШОДА ИНФОРМАЦИИ , содержащее триггер, первый делитель частоты, первый и второй эле-г менты И-НЕ, первый вход первого элемента И-НЕ соединен с выходом делителя частоты, о тличающ е е с я тем, что, с целью расширения диапазона изменения его пропускной способности , в него введены второй делитель частоты, блок сравнения, первый и второй дешифраторы и реверсивный счетчик, суммирукнций вход которого соединен с выходом первого элемента И-НЕ, а вычитающий - с.выходом второго элемента И-НЕ, выход реверсивного счетчика соединен с первым входом второго делителя частоты и с входами первого и второго дешифраторов , выходы которых соединены соответственно с вторым входом первого и первым входом второго элементов И-НЕ, второй .вход второго элемента И-НЕ соединен с выходом блока срав нения, первьш вход которого соединен с выходом второго делителячастоты и с входом установки в 1 триггера, второй вход блока сравнения соединен с входом установки в О триггера и является стробирующим входом устройства , второй вход второго делителя частоты является синхровходом устрой (Л ства, первый выход триггера является с выходом запроса данных устройства, второй выход триггера соединен с входом первого делителя частоты, выход которого является управляющим выходом устройства, второй вход второго делителя частоты является синхровходом со а устройства. 00 00

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

09) (и) (594 G 06 F 13 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЦТИЙ (21) 3759741/24-24 (22) 22.06.84 (46) 07.12.85. Бюл. ¹ 45 (71) Специальное конструкторское бюро сейсмического приборостроения (72) Н.А.Макаев (53) 681.327.21(088.8) (56) Авторское свидетельство СССР

, № 890559, кл. G 06 F 13/00, 1980.

Авторское свидетельство СССР № 792574, кл. G 06 F 13/00, 1979. (54)(57) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОР-.

МАЦИИ, содержащее триггер, первый де-. литель частоты, первый и второй эле-. менты И НЕ, первый вход первого элемента И-НЕ соединен с выходом делителя частоты, о т л и ч а ю щ е е с я тем, что, с. целью расширения диапазона изменения его пропускной способности, в него введены второй делитель частоты, блок сравнения,. первый и второй дешифраторы и реверсивный счетчик, суммирующий вход которого соединен с выходом первого элемента И-НЕ, а вычитающий — с выходом второго элемента И-НЕ, выход реверсивного счетчика соединен с первым входом второго делителя частоты и с входами первого и второго дешифраторов, выходы которых соединены соответственно с вторым входом первого и первым входом второго элементов И-HE второй вход второго элемен-. та И-НЕ соединен с выходом блока сравнения, первый вход которого соединен с выходом второго делителя. частоты и с входом установки в "1" триггера, второй вход блока сравнения соединен с входом установки в "0" триггера и является стробирующим входом устройс ства, второй вход второго делителя Щ частоты является синхровходом устрой- ства, первый выход триггера является МФ выходом запроса данных устройства, второй выход триггера соединен с входом первого делителя частоты, выход которого является управляющим выходом устройства, второй вход второго делителя частоты является синхровходом устроиства

1 1

Изобретение относится к вычислительной технике и может использоваться для вывода информации на устройства отображения выходных данных и для согласования их работы с 3ВМ в широком диапазоне скоростей.

Целью изобретения является расширение диапазона изменения пропускной способности устройства.

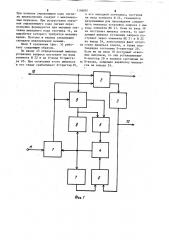

На фиг. 1 представлена структурная схем 1 предлагаемого устройства;

i на фиг. 2 — структурная;: схема вто-рого делителя частоть1 на фиг. 3 схема блока сравнения.

Устройство имеет. делитель 1 частоты, триггер 2, делитель 3 частоты, реверсивный счетчик 4, первый 5 и второй 6 элементы И-НЕ, первый 7 и второй 8 дешифраторы, блок 9 сравнения, стробирующий вход 10, синхровход 11, выход 12 запроса данных, управляющий выход 13, двоичный счетчик 14, двоичный сумматор 15, другой триггер 16, первый вход 17, элемент 18 задержки, выход 19, D-триггер 20, элемент НЕ 21, элемент И 22, первый вход 23, выход 24.

Устройство работает следующим образом.

В исходном состоянии коэффициент деления делителя 1 частоты и период его выходных импульсов максимальны.

Со входа 11 тактовые импульсы поступают на второй вход делителя 1 частоты, и на его выходе вырабатываются .импульсы установки запроса, которые поступают на единичный вход триггера 2 и устанавливают его в единичное состояние. С первого выхода триггера 2 потенциальный сигнал запроса данных через выход 12 поступает в ЭВМ (на фиг. 1 не показана) для осуществления вывода данных по принципу "Запрос — ответ". Из ЭВМ на сигнал запроса выдается слово данных

° в сопровождении импульса ответа, который через вход 10 поступает на нулевой вход триггера 2, возвращая его в исходное состояние. В результате в процессе вывода данных из ЭВМ триггер 2 переключается с частотой поступления данных. Импульсы переключения триггера 2 с его второго выхода подаются на вход делителя 3 частоты, с выхода которого дифференцированные импульсы пониженной частоты поступают на первый вход первого элемента И-НЕ 5, на второй вход . которого поступает разрешающий потен196881 2 циал с выхода первого дешифратора 7.

Выходные импульсы первого элемента ИНЕ 5, воздействуя на суммирующий вход реверсивного счетчика 4, увеличивают значение его выходного кода, который поступает в качестве управляющего кода на первый вход делителя 1 частоты. Каждому значению управляющего кода соответствует определенная величина периода следования выходных имf0 пульсов делителя 1 частоты. Единичное приращение кода уменьшает этот период на величину периода тактовых импульсов, поступающих на второй вход делителя 1 частоты. Например, при

15 для дальнейшего увеличения скорости является недостаточное быстродействие программ ЭВМ, при котором Не на каж45 дый импульс установки запроса успевает выработаться ответный импульс.

Анализ отсутствия ответных импульсов осуществляется в блоке 9 сравнения, на выходы которого подаются импульсы установки запроса и ответные импульсы. Если в промежутке времени между двумя соседними импульсами уста новки запроса не поступает ответный импульс, то с выхода блока 9 сравнения поступает импульс на первый

55 вход второго элемента И-НЕ 6, на второй вход которого поступает разрепериоде следования тактовых импульсов, равном 1 мкс, и четырехразрядном управляющем коде период следования выходных импульсов может принимать значения от 15 до 1 мкс с дискретностью в 1 мкс, Таким образом, частота переключений триггера 2, а,следовательно, и скорость прохождения данных возрастают по мере выработки импульсов на выходе делителя 3 частоты. Эти импульсы поступают также на выход 13 и используются в приводе носителя изображения в качестве запускающих

30 и обеспечивающих перемещение носителя изображения синхронно с поступлением данных. Коэффициент деления делителя 3 частоты выбирается из расче,та получения частоты его выходных импульсов в диапазоне рабочих частот привода, которые при таком режиме постепенного увеличения скорости работы могут быть доведены до значений, существенно превышающих номиналь. ные.

Возрастание скорости прохождения данных может прекратиться в двух случаях, В одном из них препятствием

3 11 шающий потенциал с выхода вторбго дешифратора 8 при ненулевых состояниях реверсивного счетчика 4. Выходной импульс второго элемента И-HE 6, воздействуя на вычитающий вход реверсивного счетчика 4, уменьшает значение его выходного кода, в результате чего. период следования импульсов установ- . ки запроса увеличивается на величину периода тактовых импульсов и на каждый импульс установки запроса вновь начинают поступать ответные импульсы. Это продолжается до момента выработки импульса на выходе делителя 3 частоты. Его выходной импульс поступает через первый элемент И-НЕ 5 на суммирующий вход реверсивного счетчика 4, и значение управляющего кода на первом входе делителя 1 частоты вновь возрастает, период следования импульсов установки запроса уменьшается, появляются пропуски ответных импульсов с соответствующими воздействиями на вычитающий вход реверсивного счет-, чика 4 -и т.д. Устанавливается динамическое равновесие, когда величина периода следования импульсов установки запроса поддерживается на уров не, определяемом быстродействием программы ЭВМ, с точностью до величины периода следования тактовых импульсов.

Другой случай ограничения скорости прохождения данных имеет место при достаточно большом быстродействии программы ЭВМ и меньшем быстродействии устройства отображения выходных данных, когда при любой скорости на каждый импульс установки запроса успевает .выработаться ответ-. ный импульс. При этом скорость прохождения данных возрастает до того момента, когда период следования импульсов установки запроса достигает величины, равной времени обработки принятого слОва данных в устройстве отображения. В этот момент управляющий код на выходе реверсивного счетчика 4 достигает заданного значе. ния и первым дешифратором 7 вырабатывается запрещающий потенциал на втором входе первого элемента И-НЕ 5

В результате блокируются импульсы запуска реверсивного счетчика 4 по суммирующему входу, и его выходной код с соответствующей ему скоростью прохождения данных фиксируются на достигнутом значении. При остановке программы ЭВМ ответные импульсы от96881 4 сутствуют, и блок 9 сравнения вырабатывает импульсы, поступающие через второй элемент И-НЕ 6 на вычитающий вход реверсивного счетчика 4 и увеличивающие период следования импульсов установки запроса, уменьшая тем самым скорость прохождения данных при возможном возобновлении обмена.

Если обмен не возобновляется, то вы10 ходной код реверсивного счетчика 4 достигает нулевого значения, при котором срабатывает второй дешифратор 8, и его низким выходным потенциалом через второй элемент И-НЕ 6 блокируется запуск счетчика 4 по вы. читающему входу, предохраняя его от переполнения и перехода на верхний уровень скорости обмена. При этом устанавливается максимальный период

20 следования импульсов установки за-. проса и соответствующая ему минимальная скорость прохождения данных при возможном возобновлении обмена. Аналогичным образом устройство приходит в исходное состояние при включении электропитания, когда еще отсутствует обмен с ЭВМ.

Делитель 1 частоты (фиг. 2) работает следующим образом.

Через первый вход 17 на первчю

30 гРуппу входов двоичного сумматора 15 поступает управляющий двоичный код с выхода .реверсивного счетчика 4.

На вторую группу входов двоичного сумматора 15 с выхода счетчика 14 . поступает двоичный код, изменяю35 щийся по своему значению от нулевого до максимального, так как счетчик 14 постоянно запускается через второй вход 11 тактовыми импульса40 ми. Если управляющий код на первой группе входов сумматора 15 принимает нулевое значение, то при достижении выходным кодом .счетчика 14 максимального значения (во всех разрядах

45 единицы) на выходе сумматора 15 формируется сигнал переполнения (переноса в старший разряд), поскольку на

его вход переноса постоянно подается логический уровень единицы. По сигна50 лу переполнения срабатывает триггер 16, сигнал которого поступает на выход 19 и на сброс счетчика 14, приводя его в нулевое состояние.

Триггер 16 обеспечивающий устой55 чивый сброс всех разрядов счетчика 14, возвращается в исходное состояние через элемент 18 задержки сдвинутыми тактовыми импульсами.

S 1196

При нулевом управляющем коде сигналы переполнения следуют с максимальным периодом. При возрастании значения управляющего кода сигнал переполнения формируется при меньшем значении выходного кода счетчика 14, на выработку которого требуется меньшее время. Поэтому и период следования сигналов переполнения меньше.

Блок 9 сравнения (фиг. 3) работает следующим образом.

По входу 23 отрицательный импульс установки запроса поступает на вход элемента И 22 и на С-вход D-триггера 20. При окончании этого импульса 15 и его спаду срабатывает D-триггер 20, 881 а и его выходной потенциал, поступая на вход элемента И 22, становится разрешающим для прохождения следующего импульса установки запроса с выхода элемента НЕ 21, Если на вход 10 не поступает импульс ответа, то следующий импульс установки запроса поступает через элементы НЕ 21 и И 22 на выход 24, констатируя факт отсутствия импульса ответа, а также подтверждая состояние D-триггера 20.

Если же на вход 10 поступают ответные импульсы, то они устанавливают

D-триггер 20 в нулевое состояние по

R-входу, запрещая выработку импульсов на выходе 24.

1196881

Фиг. 2

Составитель И.Алексеев

Редактор О.Бугир Техред Л.Мартяшова Корректор С.illexMap

«т

Заказ 7565/48 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óæãoðoä, ул.Проектная, 4