Многоканальное устройство ввода информации

Иллюстрации

Показать всеРеферат

МНОГОКАНАЛЬНОЕ.УСТРОЙСТВО ВВОДА ИНФОРМАЦИИ, содержащее входной регистр, выходной регистр, блок запоминания , блок синхронизации, элемент ИЛИ и элемент И, причем информационный вход устройства подключен к информационному входу входного .регистра, выход младших разрядов которого подключен к входу адреса считывания блока запоминания, инфррт мационный вход которого подключен к входу признаков выборки канала устройства, вход тактовых импульсов блока запоминания подключен к первому входу тактовых импульсов устройства , выход элемента И подключен к синхровходу выходного регистра, выход которого подключен к информационному выходу устройства, второй вход тактовых импульсов устройства подключен к входу запуска сигнала стробирования признаков блока синхронизации , отличающееся тем, что,, с целью повышения достоверности функционирования, в него введены регистр сос гояния, регистр условий и две группы элементов И, причем второй вход тактовых импульсов устройства подключен к синхровходу входного регистра, выход которого подключен к информационному входу выходного регистра, вход начальной устаноткй устройства подключен к установ.очнрму входу регистра состояния и к входу признака адреса данных блока запоминания, информационный вход которого подключен к входу условий выборки канала устройства ,, выход Кто разряда информационного выхода блока запоминания подключен к первому входу К-го элемента И первой группы (, К, где М - количество признаков выборки I канала), выход М+К-го разряда информационного вькода блэка запоминания (Л подключен к первому входу М+К-го элемента И первой группы, вторые входы элементов И первой группы подключены к выходу стробирования признаков блока синхронизации и соединены с синхровходом регистра условий,., выходы К-го и М+К-го элементов И со первой группы подключены соответст.О5 венно к входам разрешения установки оо: в единицу и разрешения установки оо в ноль К-го разряда регистра состояtsD ния, выход К-го разряда регистра сое-, тояния подключен к первому входу К-го элемента И второй группы, выход и второй вход которого подключены соответственно к К-му входу элемента ШШ и к К-му выходу регис.тра условий , выход

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1196882 (51)4 G 06 F 13/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ЗСЕСОЩ5ю g

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13: „, 13

Н А9ТОРСКОМУ СВИДЕТЕЛЬСТВУ (2.1) 3775459/24-24 (22) 25.07.84 (46) 07. 12.85. Бюл. Ф 45 (72) В.С.Лупиков, С.С.Спиваков, О.В.Белоус и Б.С.Маслеников (53) 681.32(088.8) (56) Авторское свидетельство СССР

N- 1070538, кл. G 06 F 3/04, 1984.

Авторское свидетельство СССР

В 860043, кл. G 06 F 3/00, 1979. (54) (57) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО

ВВОДА ИНФОРМАЦИИ, содержащее входной регистр, выходной регистр, блок запомйнания, блок синхронизации, элемент ИЛИ и элемент И, причем информационный вход устройства подключен к информационному входу входного .регистра, выход младших разрядов которого подключен к входу адреса считывания блока запоминания, инфор-. мационный вход которого подключен к входу признаков выборки канала устройства, вход тактовых импульсов блока запоминания подключен к первому входу тактовых импульсов устройства, выход элемента И подключен к синхровходу выходного регистра, выход которого подключен к информационному выходу устройства, второй вход тактовых импульсов устройства подключен к входу запуска сигнала стробирования признаков блока синхронизации, отличающееся тем, что, с целью повышения достоверности функционирования, в него введены регистр состояния, регистр условий и две группы элементов И, причем второй вход тактовых импульсов устройства подключен к синхровходу входного регистра, выход которого подключен к информационному вхо, ду выходного регистра, вход начальной установки устройства подключен к установочному входу регистра состояния и к входу признака адреса данных блока запоминания, информационный вход которого подключен к входу условий выборки канала устройства,. выход К-го разряда информационного выхода блока запоминания подключен к первому входу К-ro элемента И первой группы (К=1, М, где М вЂ” количество признаков выборки канала), выход М+К-ro разряда инфор- Ж мационного выхода блока запоминания подключен к первому входу М+К-ro элемента И первой группы, вторые входы элементов И первой группы под с ключены к выходу стробирования признаков блока синхронизации и соединены с синхровходом регистра условий,. выходы К-го и М+К-го элементов И первой группы подключены соответст.— венно к входам разрешения установки © . в единицу и разрешения установки

QO в ноль К-го разряда регистра состояния, выход К-го разряда регистра состояния подключен к первому входу

К-ro элемента И второй группы, выход и второй вход которого подключены соответственно к К-му входу элемента ИЛИ и к К-му выходу регистра условий, выход (2М+К)-го разряда информационного выхода блока запоминания подключен к входу К-.ro разряда информационного входа регистра условий, выход элемента ИЛИ подключен к первому входу элемента И, второй вход и выход которого подключены соответ1196882 ственно к выходу стробирования записи данных и к входу запуска сигнала готовности данных блока синхронизации, выход стробирования данных которого подключен к выходу признака готовности информации устройства, причем блок запоминания содержит блок. памяти, коммутатор, регистр .адреса, два элемента И и триггер, причем выход блока памяти подключен к информационному выходу блока, информационный вход блока памяти подключен к информационному входу регистра адреса и соединен с информационным входом блока, адресный вход блока памяти подключен к выходу коммутатора, первый и второй информаци-.. онные входы которого подключены соот4

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для селекции информационных каналов в многоканальных системах сбора, регистрации и обработки измерительной информации.

Целью изобретения является повышение достоверности функционирования за счет анализа логических условий ввода.

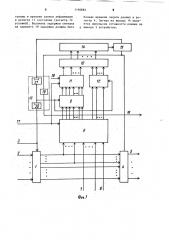

На фиг. 1 изображена функциональная схема устройства; на фиг.2функциональная схема блока запоминания.

Устройство содержит входной ре-. гистр 1, информационный вход 2 .устройства, вход 3 -тактовых импульсов устройства, выходной регистр 4, информационный выход 5 устройства, блок 6 запоминания, вход 7 признаков выборки канала, вход 8 тактовых импульсов устройства, группы элементов И 9 и 10, регистр 11 состояния, регистр 12 условий, блок 13 синхрони. зации, элемент ИЛИ 14, элемент И 15,, выход 16 признака готовности информации устройства, входы начальной установки 17 и условий выборки канала 18 устройства, элементы 19 — 21 задержки. I ветственно к входу адреса считывания блока и к выходу регистра адреса, синхровход которого подключен к выходу первого элемента И блока, вход записи/считывания блока памяти под. ключен к выходу второго элемента И блока, вход тактовых импульсов блока подключен к счетному входу триггера блока, к первым входам элементов И блока, вход признака адреса данных блока подключен к входу установки . в ноль триггера блока, инверсный и прямой выходы которого подключены к. вторым входам соответственно первого и второго элементов И блока и соединены соответственно с первым и вторым управляющими входами кож утатора.

Блок запоминания содержит элемент И 22, триггер 23, блок 24 памяти, коммутатор 25, регистр 26 адреса, элемент И 27.

В блоке 6 по адресам, .однозначно соответствующим адресным признакам измерительных каналов, хранятся управляющие слова, которые имеют три поля, а именно: поле для задания разрешения на установку условий, поле,для задания разрешения на сброс условий и поле для задания признаков выборки данных измерительных каналов на обработку при выполнении соответ15 ствующих условий.

Регистр состояния характеризует текущее состояние процесса выборки, его разрядность, как и разрядность регистра условий, равна количеству условий выборки, а значение каждого разряда регистра состояния определяет факт выполнения условий в текущий момент времени.

Устройство работает следующим образом.

Перед началом работы регистр 11 состояния и счетный триггер 23 блока 6 сигналом по входу 17 начальной установки устанавливаются в нулевые

ЗО с з

1196882 единичном состоянии счетного триггера 23. По окончании загрузки блока 6 устройство готово к работе в режиме выборки данных измерительных каналов.на обработку.

В режиме выборки данных измерительных каналов на обработку устройство работает следующим образом.

С приходом информационной посылки на вход 2 в сопровождении импульса по входу 3 по переднему фронту импульса сопровождения данные с входа 2 переписываются во входной регистр 1. По окончании записи адресная часть сообщения поступает на первые входы блока 6 запоминания и через коммутатор 25 на адресные входы блока 24> Низкий уровень сигнала на входе 8 задает для блока 24 режим . чтения. Производится чтение данных соответствующему адресной части сообщения. Стробирующим сигналом на выходе элемента 20 задержки содержимое ячейки блока 24 через элементы И 9 первой группы непосредственно модифицирует содержимое соответственно регистра 11 состояния и регистра 12 больше суммы времен,. необходимых для записи данных во входной регистр 1 и чтения данных из блока 24. Выходы одноименных разрядов регистра 11 состояния и регистра 12 условий подключены к входам одноименных элементов И 10 второй группы. При наличии совпадения на одном из элементов И 10 на выходе элемента ИЛИ 14, а следовата И 15 появляется высокий уровень. сигнала. Стробирующий сигнал на выходе элемента 21 через элемент И 15 обеспечивает перепись информации из входного регистра 1 в выходной регистр 4. По окончании переписи на выходе элемента 19 задержки появляетработки. При отсутствии совпадений на элементах И 10 второй группы данные измерительного канала на обработку не выдаются.

Величина задержки сигнала на элементе 21 задержки должна быть больше суммы времей задержки сигнала на элеУстройство имеет два режима работы: режим начальной загрузки блока памяти и режим выборки данных измерительных каналов на обработку.

В режиме начальной загрузки бло- 5 ка 6 по всем адресам блока 24 памяти производится запись. управляющих слов.

Управляющее слово, записываемое по К-му адресу блока 24, содержит

"единицы" в р1азрядах поля разрешения на установку., соответствующих разрядам регистра 11, которые необходимо установить при поступлении данных

К-го измерительного канала. Аналогично, управляющее слово, записываемое по К-му адресу, содержит "единицы" в разрядах поля разрешения на. сброс, соответствующих разрядам регистра 11, которые необходимо сбросить при поступлении данных К-го измерительного канала. Это управляющее из блока 24 по адресу, однозначно слово содержит "единицы" в тех разрядах поля признаков выборки, которые определяют условия, при выполнении которых и при приеме данных 25

К-го измерительного канала последние выдаются на обработку.

Начальная загрузка блока 6 выполняется следующим образом. условий. Величина задержки сигнала

На вход 7 в сопровождении сигнала M на элементе 20 задержки должна быть на входе 8 поступают коды адресов блока 24 и коды управляющих слов, записываемых по этим адресам. Коды адресов и управляющих слов чередуются между собой таким образом, что первый и все последующие нечетные посылки на входе 7 являются кодами адресов, а второй и все последующие четные посылки являются кодами управляющих слов. Первый и все последую- 4р тельно, и на первом входе элеменщие нечетные импульсы, поступающие по входу 8, проходя через открытый элемент И 27, осуществляют запись адреса управляющего слова с входа 7 в регистр 26 адреса и задним фронтом 45 модифицируют (изменяют на противоположное) состояние счетного триггера 23. Второй и все последующие ся сигнал, свидетельствующий о необчетные импульсы сопровождения по вхо- ходимости ввода данных в систему обду 8, проходя через открытый эле- у мент И 22, .осуществляют запись кода управляющего слова с входа 7 в блок 24 по адресу, хранящемуся на регистре 26 адреса, и задним фронтом модифицируют состояние счетного тригге- 5 ра 23. Выходные сигналы регистра 26 адреса подключаются к адресным входам блока 24 через коммутатор 25 при менте ИЛИ 14, элементах И 10 второй («У

1196882

Фиг.1 группы и времени записи информации в регистр 11 состояния (регистр 12 условий). Величина задержки сигнала на элементе 19 задержки должна быть больше времени записи данных в регистр 4. Сигнал на выходе 16 является импульсом готовности данных на выходе 5 устройства.

ii96882

Составитель M.Ñèëèí

Редактор О.Бугир ТехредС.Мигунова Корректор С,йекмар

Заказ 7565/48 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óæãoðîä, ул.Проектная, 4