Устройство для обмена данными

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ , содержащее N регистров, м коммутаторов , генератор тактовых импульсов , группу дешифраторов, первьй и второй элементы И, группу элементов И и блоки анализа, каждый из которых содержит два дешифратора , два элемента И и два элемента ИЛИ, причем с первого по N й входы данных устройства соединены соответственно с первыми информационными входами с первого noN-й коммутаторов, выходы которых соединены с информационными входами соответственно с первого по N-Й ре- . гистров, синхровходы которых соединены с первым выходом генератора тактовых импульсов, группа разрядных выходов i -го регистра соединена с вторым информационным в.ходом (. + 1)-го коммутатора, группа выходов разрядных данных N -го регистра соединена с вторым информационным входом первого коммутатора, группы выходов разрядов данных с первого по Ю-й регистров являются с первого по N-и выходами данных устройства, группы выходов разрядов адресов первого и i. -го регистров соединены соответственно с . входами первых дешифраторов первого и второго блоков анализа, причем в каждом блоке анализа первая группа выходов первого дешифратора соединена с входами первого элемента ИЛИ,выход которого соединен с первым входом второго элемента ИЛИ, группа выходов разрядов адресов с второго по (-2)-й и с (i+1)-ro ; по (М-1)-й регистров соединены с входами соответствующих дешифрато8 S . ров группы, первый выход первого дешифратора первого блока анализа, (Л первые выходы с первого по

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5l)4 G 06 F 13/36

ВСЕСОЮЗПИ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

13,",., ".;. „ :„„13

БИБЛИОТЕКА

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3768822/24-24 (22) 11.07.84 (46) 07.12 85. Бюл, Ф 45 (72) Б.М.К: норев., В.С.Харченко, С,Б.Никольский, Г.Н.Тимонькин, С.Н.Ткаченко, М.А.Чернышов и А.В,Бек (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Р 1072047, кл, С 06 F 9/46,. 1984.

Экспресс-информация, сер, ВТ, 1982, У 35, с.12, рис, 3, (54)(57) УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ, содержащее м регистров, коммутаторов, генератор. тактовых импульсов, группу дешифраторов, первый и второй элементы И, группу элементов И и блоки анализа, каждый из которых содержит два дешифратора, два элемента И и два элемента ИЛИ, причем с первого по м -й входы данных устройства соединены соответственно с первыми информационными входами с первого по и -й коммутаторов, выходы которых соединены с информационными входами соответственно с первого по Ь1-й регистров, синхровходы которых соединены с первым выходом генератора тактовых импульсов, группа разрядных выходов i -го регистра соединена с вторым информационным входом (i+1)-го коммутатора, группа выходов разрядных данных N --ro регистра соединена с вторым информационным входом первого коммутатора, группы выходов разрядов данных с первого по й-й регистров являются с первого по м -й выходами данных

„„Я0„„1196885 A устройства, группы выходов разрядов адресов первого и -го регистров соединены соответственно с входами первых дешифраторов первого и второго блоков анализа, причем в каждом блоке анализа первая группа выходов первого дешифратора соединена с входами первого элемента ИЛИ,выход которого соединен с первым входом второго элемента ИЛИ, группа выходов разрядов адресов с второго по (q-2)-й и с (<+1)-ro по (й -1)-й регистров соединены с входами соответствующих дешифрато.ров группы, первый выход первого дешифратора первого блока анализа, первые выходы с первого по (-3)-й дешифраторов группы, выход второго дешифратора первого блока анализа, первый выход первого дешифратора второго блока анализа, первый выход (N-4)-го дешифратора группы и вьгход второго дешифратора второго блока анализа являются соответственно с первого по и -й выходами прерываний устройства, о т л и ч а ю, щ е е с я тем, что, с целью повышения производительности, оно содержит третий и четвертый элементы И, а в каждый блок анализа введены третий элемент ИЛИ и третий элемент И, причем в блоке анализа вторая группа выходов первого дешифратора соединена с группой входов третьего элемента ИЛИ, выход которого соединен с первыми входами первого и третьего элементов И, первый выход первого дешифратора соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом

11 генератора тактовых импульсов, соединенным также с первыми входами элементов И группы и третьего, четвертого элементов И, выходы вторых элементов И первого и второго блоков анализа соединены соответственно с входами сброса первого и

q-го регистров, первые выходы дешифраторов группы соединены с вторыми входами, соответствующих эле...ментов И группы, выходы которых соединены с входами сброса с второго по (- 2)-й и с (i+1)-го по (й-1)-й регистров соответственно, а в каж- . дом блоке анализа выход второго дешифратора соединен с вторым входом третьего элемента И, выход которого соединен с вторым (инверсным) входом первого элемента И, выход которого соединен с вторым входом .второго элемента ИЛИ, выходы вторых дешифраторов первого и второго блоков анализа соединены соответственно с первыми входами первого и второго элементов И и вторыми вхо-, дами третьего и четвертого элементов И, выходы первого и второго элементов И соединены соответственно с первыми управляющими входами

6-ro и первого коммутаторов, выходы третьего и четвертого элементов И

96885 соединены с входами сброса (-1)-го и М -го регистров: соответственно, вторые выходы первых дешифраторов первого и второго блоков анализа соединены соответственно с первыми управляющими входами второго и (i+1)-ro коммутаторов и вторыми входами соответственно первого и второго элементов И, выходы третьих элементов И первого и второго блоков анализа соединены соответственно с вторыми управляющими входами -ro и первого коммутаторов, выходы вторых элементов ИЛИ первого и второго блоков анализа соединены соответствен.;о с вторыми управляющими входами второго и (q -1)-го коммутаторов, вторые выходы дешифраторов группы соединены соответственно с управляющими входами с третьего по (j -1)-й и с (i+2)-ro no N - и коммутаторов, группы разрядных выходов первого и -го регистров соединены . соответственно с третьими информационными входами <-го и первого коммутаторов, группы выходов разрядов адреса (<-1)-ro и м -горегистров соединены соответственно с входами вторых дешифраторов первого и второго блоков анализа.

Изобретение относится к вычислительной технике и может быть использовано в качестве коммутирующей сети для управления и обмена данными в распределенных .системах ,с контролем.

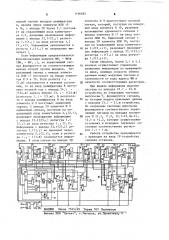

Целью изобретения является повышение производительности устройства путем обеспечения возможности изменения направления сообщений по вращающейся шине, На чертеже представлена функци,ональная схема устройства.

Устройство содержит первый - N -й регистры 1,1 — 1,И соответственно, первый — N -й коммутаторы 2, триг- гер 3, генератор 4 тактовых импульсов, первый 5.1 и второй 5 2 блоки анализа, первый дешифратор 6, пер2 вый — (H-4)-й дешифраторы 7.1

7,.(8-4) группы, дешифратор 8, третий элемент И 9, первый элемент И 10 второй элемент И 11, первый— (й-4)-й элемент И 12.1 †. 12. (N-4), первый 13,1 и второй 13,2 элемен.ты И,третий 14.1 и четвертый 14,2 элементы И,первый элемент ИЛИ 15 элемент ИЛИ 16, третий элемент. ИЛИ 17

1О . вход 18 пуска устройства, вход 19 останова устройства, первый — N -й входы 20 ° 1 — 20. N данных устройства, первый — и -й выходы 21,1 — 21. и данных устройства, первый t4-й выходы 22. 1 — 22, и прерываний устройства, выходы 23,1 - 23, N соответственно первого — N --ro регистров 1.1 — 1. М выходы 24,1 — 24.

11адресов выходов регистров 1,1 — 1.

10 анализа.

Устройство работает следующим образом.

В исходном состоянии все регистры и триггер устройства находятся в нулевом состоянии. Цепи установки в исходное состояние на функциональной схеме условно не показаны.

15.Работа устройства начинается с момента прихода на вход 18 устройства сигнала пуска ° Триггер 3 устанавливается в единичное состояние, генератор 4 тактовых импульсов на,чинает формировать на своих выхо дах 25„1 и 25,2 две последовательности сдвинутых друг относительно друга тактовых импульсов и

11

Данные.на входы 20.1 — 20. l4 устройства от функциональных модулей могут поступать асинхронно друг относительно друга. Рассмотрим особенности приема данных по входам

20.3. — 20. (; -1); 20. (+2) -20. М устройства. Данные со входа 20,3 устройства, пройдя через коммутатор 2.3, записываются в регистр 1.3 по очередному тактовому импульсу 1,, Разрешающим сигналом для прохождения данных через коммутатор 2,3 является единичный сигнал, посту.пающий с выхода дешифратора 7,1 на вход которого поступает нулевой код адреса функционального модуля— признак пустого предыдущего регистра 1.2. Аналогичным образом данные 45 с входов 20.4 — 20.(1-1) и 20.(; +2)

20.14 устройства соответственно че-.. рез коммутаторы 2,4 — 2.(1 -1) и

2.(1,+2) — 2. N по разрешающим сиг налам с выходов дешифраторов 7.2 — 50

7.(i-3) и 7. 1 — 7.(11-4) записываются в регистры.1.4 — 1,(1-1) и

1,(с +2) — 1. и по тактовому импульсу 1,. По очередному тактовому им.пульсу данные из 1 -го регистра 55 записываются в 0 +1)-й регистр, где 1 -l, N . .Пбд (й+1)-м регистром подразумевается регистр 1.1.

1196

/\l соответственно, первый и второй выходы 25.1 и 25.2 генератора 4 . тактовых импульсов соответственно; второй выход 26 первого дешифратора 6, выход 27 элемента ИЛИ 15, 5 выход 28 элемента ИЛИ 16, выход 29 элемента И 9 выход 30 элемента И 11, выход 31.1 и 31 ° 2 соответственно первого 5.1 и второго 5,2 блоков

Рассмотрим особенность приема данных от функциональных модулей . по входам 20,2 и 20. (i.+1 ) устройства. Данные со входов 20.2 и 20. (i+1) устройства соответственно по разрешающим сигналам с выходов 26 блоков 5 ° 1 и 5.2 анализа, пройдя соответственно через коммутаторьг 2.2 и 2.(i,+1), по очередному тактовому импульсу 1, записываются Соответст-. венно в регистры !.2 и 1.(i +1).

Разрешающие единичные сигналы на выходах 26 блоков 5,1 и 5 ° 2 для прохождения данных с входов 20.2 и 20.(1+1) устройства появляются в результате поступления на входы первого дешифратора 6 нулевых кодов адресов с выходов 24.1 и 241 адресов, выходов 23.1 и 23; соответственно регистров 1.1 и 1.1 которые являются признаками. свободных регистров 1,1 и 1,(1 - 1). Таким образом, данные с входов 20,2 и

20.(i +1.) устройства не пересекаются с информацией, передаваемой по вращающейся шине.

Запись данных со входа 20. 1(20,1 ) устроиства через коммутатор 2.1 (2.1 ) в регистр 1.1 (1.1 ) возможна при пустых регистрах 1, N (1. 1-.1) и 1. 1 (1.1). При этом с выхода элемента И 13 на первый управляющий вход коммутатора 2.1(2.1 ) поступает единичный разрешающий сигнал. Этот сигнал формируется при поступлении единичных сигналов с выхода 31.2. (31. 1), Данные, записанные.в регистры

1.1 — 1.й, по очередным тактовым импульсам 1„ перемещаются последовательно из (1 — 1)-го регистра в

L-й регистр, где 1 =1д . акая по-. следовательность перемещения информации из регистра в регистр может быть нарушена только при записи данных в регистры 1.1 и 1.1.

При записи информации в регистр

1.1(1.i) код адреса с выхода 24. 1 (24, ) поступает на вход дешифратора 6, В зависимости от номера кода адреса на выходе первой или второй группы выходов дешифратора б формируется управляющий сигнал.

Если информация, записанная в регистре 1, 1(1.i.),ëðåäíàçíà÷åíà функциональным Модулем ФМ вЂ” ФМ1.1-1) (ФМ,,„ - ФМ11 ), то управляющий сигнал появляется на одном из выходов

1196885

/2 2/5! (гi-(2/i

iir(г/i+I сь(20.i

4 г а

24.И

2(1è

2И г/.н

2И ((c.ц Ю

22.2-/

2Н

2iч/.г ггг

f2.i-з

l2.f

//ЖЗ йl

5 / a

/8

aS C

ыг

ВНИИПИ Заказ 7565/48 Тираж 709 Подписное

Филиал ППП "Патент", r.Óæãîðoä, ул.Проектнаяд, первой группы выходов дешифратора и, пройдя через элеменVbl ИЛИ 15 и 16, с выхода 28 блока 5.1 поступает на управляющий вход коммутато5 ра 2.2, разрешая прохождение информации с выхода 23.1(23.I ) регистра 1.1(!. ) на вход регистра 1.2 (1 ° < +1). Информация записывается в регистр 1,1(1,i ) по очередному им- 10

/ пульсу

Если информация предназчачается функциональным модулем ФМ; — ФИ М (ФМ вЂ” ФМ, ), то управляющий сигнал- формируется на соответствующем 15 выходе второй группы выходов. Уп-. равляющий сигнал с выхода элемента ИЛИ 17 поступает на входы элементов И 9 и 10 ° Если регистр 1. (1,N) оказывается в нулевом состоя- 20 нии, то на вход дешифратора 8 поступает нулевой код с выхода 24.а

1(24.M) адреса выхода 23, — 1(24.М ) регистров 1. — 1(1,11), В результате с выхода дешифратора 8 на вход 25 элемента И 9 поступает единичный сигнал, С выхода 29 элемента И 9 единичный сигнал, поступая на управляющий вход коммутатора 2.1(2.1), разрешает прохождение информации 30 с выхода 23.1(23.() регистра 1.1 (1. 1),на вход регистра 1, (1.1).

Информация с выхода 23.1(23.1) регистра 1 ° 1(1.I.) не проходит через коммутатор 2. i(2. 1), если в регистре 1, i — 1(1.11) оказывается информация. В этом случае.на выходе 2g элемента И 9 присутствует нулевой сигнал, который, поступая на инверсный вход элемента И 10, разрешая прохождение единичного сигнала с выхода элемента И 17 на вход элемента ИЛИ 16. Единичный сигнал с выхода 28 элемента ИЛИ 16, поступая на управляющий вход коммутатора 2.2(2.i+1), разрешает прохождение информации с выхода 23,1(23. ) регистра 1.1(1.p) на вход регистра 1. 2 (1. б+1) .

Таким образом, блоки 5.1 и 5.2 анализа осуществляют управление движением информации по вращающейся шине, повышая скорость обмена данными между модулями системы в зависимости от кода адреса ФМ и занятости соответствующих регистров..

При выдаче информации модулям системы на выходах 22. 1 — 22. 11 устройства по очередным тактовым импульсам „ формируются сигналы, по которым модули принимают данные с выходов 21,! — 21.й устройства.

По очередным тактовым импульсам формируются соответственно управляющие сигналы на выходах элементов И 1.1.1, 11.2, 12.1-12. (М-4), 14.1 и 14,2, которые осуществляют установку в исходное (нулевое) состояние соответственно регистров 1.1 — 1,N.

Работа устройства прекращается с приходом на вход 19 устройства сигнала останова.