Запоминающее устройство

Иллюстрации

Показать всеРеферат

I.ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, первые и вторые входы и выходы которых являются соответственно первым и вторым входами и первым выходом устройства , адресные блоки, выходы которых соединены с третьими входами соответствующих блоков памяти, о тличающее . с,я тем, что, с целью повышения емкости устройства, в ,него введен формирователь адресных сигналов, вход которого подключен к выходам блоков памяти, первый и второй выходы соединены с первыми и вторыми входами блоков памяти и адресных блоков, третий и четвертый выходы формирователя ад ресных .сигналов и третий и четверть1й входы адресных блоков являются соответственно третьим и четвертым входами устройства, Четвертые входы блоков памяти, пятые входы адресных блоков и пятый выход формирователя адресных сигналов являются вторым выходом устройства, шестой выход формирователя адресных сигналов соединен с шестыми входами адресных блоков. . 2. Устройство по п.1, о т л ичающееся тем, что каждый адресный блок содержит элементы И с первого по третий, первый элемент . НЕ, блоки сравнения, первый регистр, генераторы импульсов, первьгй коммутатор и дешифратор, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с выходом первого блока сравнения, а выход подключен к входу первого элемента НЕ и первому входу первого элемента И, выход первого генератора импульсов соединен с первыми входами первых блока сравнения и регистра, второй и третий входы которого подключены g соответственно к выходам второго генератора импульсов и Первого элеСП мента И, а выход соединен с первым входом второго блока сравнения, вьгход которого подключен к первому входу третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, а выход - с первым входом первого коммутатора, со выход которого является выходом фор05 мирователя, входами которого являют-, OD ся соответственно второй в.хОд пер вого коммутатора и вход nepjjoro со дешифратора, второй вход первого блока сравнения, четвертыйвход первого регистра, второй вход вто рого блока сравнения и третий вход первого блока сравнения, третий вход второго блока сравнения, второй вход второго элемента И, 3. Устройство по П.1, о т л ичающее с я тем, что формирователь адресных сигналов содержит элементы И с четвертого по двенадцатый , элемент НЛП, второй элемент

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 G 11 11/00 (1 °

ОПИСАНИЕ ИЗОБРЕТЕНИЯ. И ABT0PCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3706134/24-24 (22) 01.03.84 (46} 07.12.85. Бюл. М 45 (72) В.Г.Романьков (53) 681.327(088.8) (56) Авторское свидетельство СССР

М 1016832, кл. 0 Il С Il/00, 1982.

Каган Б.M. Электронные вычислительные машины и системы. — М., Энергия, 1979, с. 454-457. (54)(57) I.ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, первые и вторые входы и выходы которых являются соответственно первым и вто" рым входами и первым выходом устрой. ства, адресные блоки, выходы которых соединены с третьими входами соответствующих блоков памяти, о тл и ч а ю щ е е. с я тем, что, с целью повышения емкости устройства, в,него введен формирователь адресных сигналов, вход которого подключен к выходам блоков памяти, первый и второй выходы. соединены с первыми и вторыми входами блоков памяти и адресных блоков, третий и четвертый выходы формирователя адресных .сигналов и третий и четвертый входы адресных блоков являются соответственно третьим и четвертым входами устройства, четвертые входы блоков памяти, пятые входы. адресных блоков и пятый выход формирователя адресных сигналов являются вторым выходом устройства, шестой выход формирователя адресных сигналов соединен с шестыми входами адресных блоков.

2. Устройство по п.l, о т л ич а ю щ е е с я тем, что каждый

„„SU„„1196949 A адресный блок содержит элементы И с первого по третий, первый элемент .

НЕ, блоки сравнения, первый регистр, генераторы импульсов, первый коммутатор и дешифратор, выход которого подключен к первому входу втсрого элемента И, второй вход которого соединен с выходом первого блока сравнения, а выход подключен к входу первого элемента НЕ и первому входу первого элемента И, выход первого генератора импульсов соединен с первыми входами первых блока сравнения и регистра, второй и третий входы которого подключены соответственно к выходам второго генератора импульсов и первого элемента И, а выход соединен с первым входом второго блока сравнения, вы" ход которого подключен к первому входу третьего элемента И, второй вход которого соединен с выходом первого элемента НЕ, а выход — с первым входом первого коммутатора, выход которого является выходом формирователя, входами которого являют-. ся соответственно второй вход первого коммутатора и вход первого дешифратора, второй вход первого блока сравнения, четвертый вход первого регистра, второй вход второго блока сравнения и третий вход первого блока сравнения, третий вход второго блока сравнения, второй вход второго элемента И.

3. Устройство .по п.l о т л ич а ю щ е е с я тем, что формирователь адресных сигналов содержит элементы И с четвертого по двенадцатый, элемент ИЛИ, второй элемент

1196949

НГ, КЯ-триггеры.с первого по четвертьп», D-триггер, формирователи сигнанов с первого по восьмой, регистры с второго по четвертый, первый и второй регистры сдвига, счетчик, коммутаторы со второго по четвертый, группы усилителей, третий блок сравнения, второй дешифратор, элемент задержки и третий генератор импульсов, выход которого подключен к первым. входам элементов И с четвертого по седьмой и через второй элемент НŠ— к С-входам D-триггера, первого регистра сдвига и к входу элемента задержки, .С-выходы вто-рого и третьего регистров соединены соответственно с выходами четвертого и пятого элементов И, выход шестого элемента И соединен с первым R-входом первого RS-триггера, выход которого соединен с D-входом

D-триггера, выход седьмого элемента

И соединен с С-входами четвертого регистра, счетчика и с S-входами первого RS-триггера и второго регистра сдвига, С-вход которого соединен с выходом aoCbMoro элемента

И, первый выход первого регистра сдвига соединен с первым входом второ.о дешифратора,.выход которого соединен с первым входом третьего блока сравнения, второй выход первого регистра сдвига соединен . с первыми входами седьмого формирователя и второго коммутатора, выход которого соединен с D-входом четвертого регистра, третий выход первого регистра сдвига соединен со вторым входом-второго коммутатора, четвертый выход первого регистра сдвига соединен с третьим входом второго коммутатора и с первым входом девятого элемента И, выход которого соединен со счетным входом счетчика, пятый выход первого регистра сдвйга соединен с D-входом первого .регистра сдвига, с вторыми входами четвертого и пятого элементов И, с первыми входами восьмого и десятого элементов И, с

R-sxopoM второго RS-триггера и с четвертым входом второго коммутатора, входы с пятого по восьмой которого . соединены соответственно с выходами четвертого регйстра и формирователей сигналов с первого по третий, первый выход второго регистра сдвига соединен с вторым входом седьмого формирователя сигналов, перный выход которого соединен с is i)Bbl ми ".õoäàìè усилителей второй группы, второго коммутатора, с Я-входами второго и третьего RS-триггеров, второй выход второго регистра сдвига соединен с третьими входами четвертого элемента И и седьмого формирователя сигналов, второй выход которого соединен с вторыми входами усилителей второй группы, третьего коммутатора, с первыми входами четвертого коммутатора и одиннадцатого элемента И, третий выход второго регистра сдвига соединен с D-входом второго регистра сдвига, с третьим входом пятого элемента И и с четвертым входом седьмого формирователя сигналов, третий выход которого соединен с третьими входами усилителей второй группы, третьего коммутатора, с вторыми входами четвертого коммутатора, шестого элемента И, с

В-входом .четвертого RS-триггера и через пятый формирователь сигналов — .с первым входом элемента ИЛИ, выход одиннадцатого элемента И соединен с В-входом третьего RS-триггера и 8-входом четвертого RS-триггера, выход которого соединен с вторым входом десятого элемента И, выход которого соединен с R-входом второго регистра сдвига, выходы второго и третьего RS-триггеров соединены соответственно с вторыми входами девятого и восьмого элементов И,выход второго регистра соединен с четвертым входом третьего .коммутатора, выход которого соединен с входами усилителей третьей группы, первый и второй выходы третьего регистра соединены соответственно с вторым входом один,надцатого элемента И и с третьим входом четвертого коммутатора, выход которого соединен с первыми входами усилителей первой группы, первый выход .D-триггера соединен с вторым входом седьмого элемента

И,третин вход которого соединен с первым входом двенадцатого элемента

И и с выходом третьего блока сравнения, второй, выход D-триггера соединен с пятым входом седьмого формирователя сигналов и с вторым входом двенадцатого элемента И, выход которого через шестой формирователь сигналов соединен с вторым Вхо11 дом элемента ИЛИ, выход котор "o соединен с вторыми входами усилителей,первой группы, выход четвертого формирователя сигналов соединен с вторым входом третьего блока сравнения и с пятым входом третьего коммутатора, шестой вход которого.соединен с четвертым входом четвертого коммутатора и с выходом счетчика, первые выходы усилителей третьей группы соединены с третьим входом третьего блока сравнения, выходы усилителей третьей группы соединены с четвертым входом третьего блока сравнения, выход восьмого фор96949 мирователя сш налов соединен с вторым

R-входом первого RS-триггера, с

R-входом D-триггера и с Б-входом первого регистра сдвига, причем

D-входы второго и третьего регистров являются входом блока, выходами которого являются выход элемента задержки,. выход второго коммутатора, третий выход первого регистра сдвига, выходы усилителей первой группы, пятый вьгход первого регистра сдвига, первые и втоpble- выходы усилителей третьей группы, выходы, усилителей второй группы.

Изобретение относится к вычисли.ельной технике и может быть использовано при построении мультипроцессорных вычислительных систем

Цель изобретения — повышение емкости устройства.

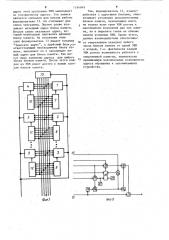

На фиг.1 изображена структурная схема запоминающего устройства; на фиг.2 — структурная схема адресного блока;. на фиг.3 — структурная схема формирователя адресных сигналов.

Запоминающее устройство (фиг.l) содержит блоки 1-6 памяти, адресные.блоки 7-12 и формирователь 13 адресных сигналов.

Каждый из адресных блоков 1-6 содержит (фиг.2) элементы И 14 -14

5 с первого по третий, входные шины 15, первый элемент НЕ 16, первый 17 и второй 18 блоки сравнения, первый дешифратор 19, первый регистр 20, первый генератор 21 импульсов, второй генератор 22 импульсов и первый коммутатор 23.

Формирователь 13 адресных сигналов (фиг. 3) содержит элементы

И 24-32 с третьего по двенадцатый, элемент ИЛИ 33, второй элемент НЕ 34

С

У

R -триггеры 35-38 с первого по четвертый, D-триггер 39, формирователи

40-47 с первого по восьмой, второй

48, третий 49 и четвертый 50 регистры, первый 51 и второй 52 регистры сдвига, счетчик 53, второй 54, третий 55 и четвертый 56 коммутаторы, первую 57, вторую 58 и третью 59 группы усилителей, третий блок 60 сравнения, второй дешифратор 61, элемент 62 задержки и третий генератор 63 импульсов.

Устройство работает следующим об5 разом.

С устройством связано несколько ЭВМ (не показаны). Каждая ЭВМ обращается к запоминающему устройству в строго отведенное для нее

10 время. Выданный ЭВМ адрес дополняется формирователем 13 адресом ЭВМ, который вместе со старшей частью

1 адреса от ЭВМ поступает во все адресные блоки 7-12. Здесь они сравни15 ваются с хранимым адресом блоков

1-6 памяти. Адре ный блок, определивший равенство-полученного сос- тавного адреса с хранимым, передает полученную команду в соответствую20 щий ему блок памяти, который выполняет ее. Так как формирователь 13 для каждой ЭВМ выдает разные адреса ЭВИ, то каждой из ЭВМ доступны свои группы блоков памяти и не

25 доступны блоки памяти других ЭВМ, о существовании которых они могут не знать. Такой режим работы ЭВИ, . подключенпых к данному запоминающему устройству, соответствует режиму работы трех независимых одна от другой ЭВИ. Обмен информацией между ЭВИ осуществляет, формирователь

13 по программе, написанной для него одной из ЭВИ и помещенной в один из блоков памяти. Начальный

1196949 рие 2 адрес этой программы.ЭВИ. записывает по условленному адресу. Эта запись является сигналом для начала работы формирователя 13. Он считывает два слова программы. Первое слово указывает исходный адрес блока памяти.

Второе слово указывает адрес, который необходимо присвоить данному блоку памяти. На основании этих слов формирователь 13 выдает команду

"Записать адрес, а адресный блок,соответствующий необходимому блоку памяти, выполняет ее и запоминает новый адрес для блока памяти. Так могут быть заменены адреса для любого числа блоков. памяти. После этого каждая из 3ВМ имеет доступ к новым группам блоков памяти.

Так, формирователь 13, взаимодействуя с адресными блоками, обеспечивает установку дополнительных блоков памяти, позволяющих иметь не только всем трем ЭВИ доступ к максимально возможной для нее памяти, но и выделять такие же объемы памяти условным ЭВИ. Кроме этого, данное взаимодействие обеспечиваI

10 ет оперативную передачу любого числа блоков памяти от одной ЭВИ к второй, т.е. фактически каждой

ЭВИ давать возможность работать с оперативной памятью, значительно

t5 превышающую максимальные возможности адреса обращения к запоминающему устройству.

1196949

Составитель В. Рудаков

Редактор О.Головач Техред М.Гергель Корректор Х.Демчик

Заказ 7570/52 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная. 4