Трансформаторное постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИН (!9) (11) (58 4 (» 11 С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

13, ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3711940/24-24 (22) 13.03.84 (46) 07.12.85. Бюл.. № 45 (72) А.Ф.Богачев, .Ю.P.Ëåìçàëü, Ю.Х.Клейман и Ю.Х.Криворуцкий (53).681.327.66(088.8) (56) Марино, Сирота. Быстродействую— щее и недорогое жгутовое ПЗУ трансформаторного типа. — Электроника, ¹ 19, 1967.

Дроздов Е.А, Комарницкий В.А.

Пятибратов А.П. Электронные вычислительные машины единой системы.—

N. Машиностроение, 1976, с. 203. (54 ) (57 ) ТРАНСФОРМАТОРНОЕ ПОСТОЯННОЕ

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, состоящий из кодовых трансформаторов, концы входньгх обмоток которых подключены к выходам адресного дешифратора, входы первой и второй групп которого являются соответственно входами первой и второй групп устройства, выходные обмотки кодовых трансформаторов подключены к одним входам блока считывания, другие входы, которого являются входами устройства, вьгходы блока считывания являются выходами устройства, ограничительный элемент, выполненный на первом резисторе, один вывод которого подключен к шине питания, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введен управляющий элемент, состоящий из транзистора и второго и третьего резисторов, одни из выводов которых подключены к базе транзистора, коллектор которого соединен с. другим выводом первого резистора, эмиттер транзистора соединен с началами входных обмоток кодовых трансформаторов, а другие выводы второго и третьего резисторов подключены к соответствующим шинам питания.

I

Изобретение относится к запоминающим устройствам.

Цель изобретения — повышение надежности устройства.

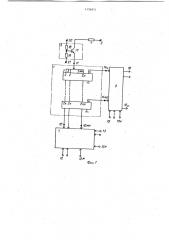

На фиг.1 изображена структурная схема предлагаемого устройства; на Фиг.2 — осциллограммы считанных из накопителя сигналов "l" (U,) и помехи (U ) (cIIJIoIIIHoH линией показаГ ны сигналы без управляющего элемента, пунктирной линией — после его введения).

Устройство содержит накопитель

1, состоящий из к групп кодовых трансформаторов 2 по р трансформаторов в кажцой группе, имеющих

MXh IIIIO EIbIX O| HO IIII 3 H KXP BblXOPHblX обмоток 4, адресный дешифратор 5, блок 6 считывания, органичительный резистор 7, подключенный к источнику:8 электропитания и управляющий элемент 9, включенный между ограни чительным резистором 7 и объединенными началами 10 входных обмоток кодовых трансформаторов. Концы входных обмоток кодовых трансформаторов соединены с соответствующими выходами 11 адресного дешифратора, входы 12 и 13 которого, в свою очередь, являются входами первой и второй групп (адресных) устройства.

Выходные обмотки кодовых трансформаторов 2 подключены к первым входам 14 блока считывания, вторые входы 15 которого являются входами третьей адресной группы устройства, а вы оды 16 — выходами устройства. Управляющий элемент состоит из транзистора

17 и двух резисторов (делителя напряжения) 1 8 и 19, соединенных одним концом с базой транзисторов 17, а другими концами — с соответствующими шинами 20 и;21 питания. Коллектор транзистора 17 соединен с ограничительным резистором 7,а эмиттер, являющийся выходом управляющего элемента, соединен с началами входных обмоток кодовых трансформаторов.

Устройство работает следующим образом.

l96951 2

В исхОДИОм cocòоянии постОяннОго запоминающего устройства через ограничительный резистор 7 и управляющий элемент 9 на начала входных обмоток 3 кодовых трансформаторов 2 подается только часть напряжения от источника 8 электропитания, величина которого определяется делителем напряжения в цели управляющеro элемен1О та 9. Паразитные емкости накопителя

1, существующие эа счет емкостных связей между обмотками кодовых тран .— форматоров 2, заряжаются до величины этого напряжения. В этот момент времени состояние устройства таково, что выборка информации из накопителя 1 не происходит. При возбужде-., нии адресных входов 12 и 13 адресного дешифратора 5 через резистор 7 и управляющий элемент 9 по цепи, выбранной адресным дешифратором 5 входной обмотки кодовых трансформаторов 2, течет ток опроса и в вы1 ходных обмотках 4 одной из K групп

25 кодовых трансформаторов 2, определя\ емой состоянием входов 15 блока 8 считывания, наведется ЭДС считанного сигнала и!и в том случае, если в и Il этих трансформаторах прошита 1

В невыбванных входных обмотках кодовых трансформаторов 2 протекает ток помехи, возникающий в результате раэряда паразитных емкостей существующих между обмотками кодовых трансформаторов 2, который искажа35 ет считанныи сигнал 1 или навои и дит ложную и!и при считывании иОи в выбранной 1 -группе кодовых трансформаторов 2. Ввиду того, что с

40 введением управляющего элемента 9 в цепь возбуждения входных обмоток 3 кодовых трансформаторов 2 напряжение заряда паразитных емкостей уменьшается, уменьшаются паразитные

45 токи в накопителе 1 и сигналы номехи, считанные из накопителя 1, что позволяет значительно расширить диапазон устойчивой работы устройства и повысить .его наДежность, ым !

1196951

Составитель Ю.Клейман

Техред А.Кикемезей Корректор F,.Ñèðoêìàí

Редактор O.Ãîëîíà÷

Филиал ППП "Патент", г.ужгород, ул. Проектная, 4 Заказ 7570/52 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5