Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11) А 1) q G 11 С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ гю е

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. (21) 3763993!24-24 (22) 28.06.84 (46) 07.12.85, Бюл. 9 45 (72) В.Б.Буй и А.Г.Солод (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

У 841047s кл. G 11 С 17/ОО, 1981.

РСТ 9 81/03571, кл. 6 11 С 17/02, опублик. 10.12.81. (54) (57) ПОСТОЯННОЕ ЗАПОМИНА10ЩЕЕ

УСТР )ЙСТВО, содержащее матрицу транзисторов связи, затворы которых подключены к горизонтальным шинам матрицы, стоки и истоки — соответственно к нечетным и четным вертикальным шинам матрицы, ключевые транзисторы,, стоки которых соединены с четными вертикальными шинами матрицы, истоки — с шиной нулевого потенциала, а затворы являются соответствующими входами выборки устройства, о т л и ч а ю щ е е .с я тем, что, с целью повышения быстродействия и упрощения, оно содержит транзисторы развязки, истоки которых подключены к нечетным вертикальным шинам матрицы, стоки нечетных и четных транзисторов развязки являются соответственно первым и вторым выходами устройства, первый и второй зарядные транзисторы и группу зарядных тран-. зисторов, затворы которых являются управляющим входом устройства, а затворы транзисторов развязки соединены с шиной питания, истоки первого и второго зарядных транзисторов соединены соответственно со стоками не-. четных и четных транзисторов развязки, а истоки зарядных транзисторов группы — с соответствующими вертикальными шинами матрицы.

1 11

Изобретение относится к вычислительной технике и может быть ис- пользовано при проектировании постоянных запоминающих устройств (ПЗУ).

Цель изобретения — повышение быстродействия и упрощение устройства.

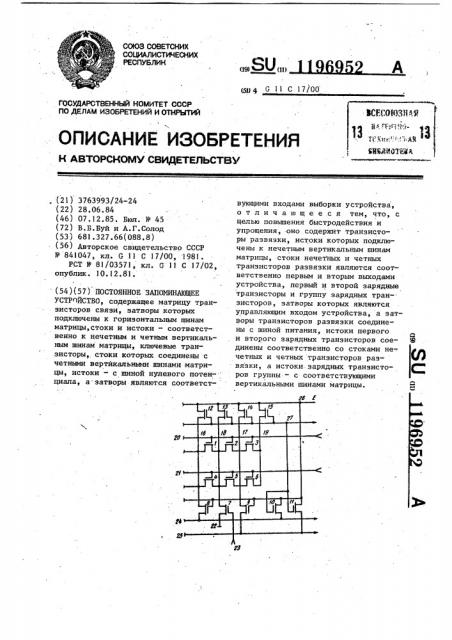

На чертеже представлена схема предлагаемого устройства (часть устройства, соответствующая одному входу выборки).

Устройство содержит матрицу транзисторов 1-6 связи, ключевой транзистор 7, транзисторы 8 и 9 развязки, первьп 10 и второй ll зарядные транзисторы и группу зарядных транзисторов 12-15 матрицы. Сток и исток каждого транзистора 1-6 .связи соединены с нечетными 16 и 17 и четными 18 и 19 вертикальными шинами.

Затворы транзисторов 1-3 и 4-6 связи соединены с горизонтальными шинами 20 и 21. Исток ключевого транзистора 7 подключен к шине 22 нулевого потенциала, а затворы — к входу 23 выборки. Транзисторы 8 и 9 развязки подключены истоками к нечетным вертикальным шинам 16 и 17.соответственно, а стоки являются. соответственно первым 24 и вторым 25 выходами устройства. Стоки всех зарядных транзисторов 10-15 и затворы проходных транзисторов 8 и 9 соеди нены с шиной 26 питания, затворы первого 10 и второго 11 зарядных транзисторов и затворы зарядных тран-. зисторов 12 — 15 соединены с управляющим входом 27 устройства.

Устройство работает следующим образом.

В исходном состоянии сигнал на управляющем входе 27 имеет уровень логической "1", а сигналы на горизонтальных шинах 20 и 21 и на входе

23,выборки — уровень логического "О".

Для простоты рассмотрения процессов в матрице примем, что уровень логического "О" ниже уровня порогового напряжения всех транзисторов с индуцированным каналом, уровень логической "1 близок к уровню питающего напряжения, пороговые напряжения всех транзисторов с индуцированным каналом (все транзисторы рассматриваемого устройства, кроме транзисторов 10 и ll, которые имеют встроенный канал), за исключением транзистора 5, одинаковы. Предполага96952 1

f0 тор связи.

50

40 ется, что пороговое напряжение транзистора 5 связи соответствует хранению кода.0, а пороговые напряжения транзисторов 1-4 и 6 связи— кода 1.

Рассмотрим уровни напряжений в узлах устройства. На всех вертикальных шинах 16-19 устанавливается уровень напряжения, равный напряжению питания минус пороговое напряжение транзисторов. На выходах 24 и

25 за счет наличия транзисторов сс встроенными каналами 10 и 11 напряжение равно напряжению питания. Токи через все транзисторы отсутствуют.

Управляющий сигнал изменяется с уровня логической "1" до уровня логического "О", а сигналы на одной иэ горизонтальных шин (на шине 21) и на входе 23 выборки изменяются от уровня логического "О" до уровня логической "1".

С момента времени, когда сигнал на входе 23 превышает уровень поро-.

Ъ гового напряжения, начинается разряд четной вертикальной шины 18 через.

l ключевой транзистор 7. Поскольку транзистор 4 имеет пороговое напряжение, равное пороговому напряжению всех транзисторов, а транзистор 5 имеет пороговое напряжение больше напряжения питания, то через транзистор 4.по мере разрядл шины 18 начинает происходить разряд шины 16, потенциал шины 17 остается неизменным, так как транзистор 5 закрыт.

Разряд шин 16 и 18 происходит от уровня, равного напряжению питания минус пороговое напряжение транзисторов. Скорость разряда шины 18 существенно выше, чем скорость разряда шины 16, так как последняя разряжается на шину 18 через транэис В момент, предшествующий считыва нию, на истоках транзисторов 8 и 9 уровень напряжения равен напряжению питания минус пороговое напряжение транзистора, на стоке и затворе этих транзисторов напряжение равно напряжению питания. Очевидно, что при достаточной крутизне характеристики транзистора, кото.— рая определяется длиной и шириной канала транзистора, изменение потенциала на первом выходе 24 начина.ет происходить одновременно с измеСоставитель А Дерюгин.Редактор О.Головач Техред А.Кикемезей Корректор М.Демчик

Заказ 7570/52 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

3 нением потенциала на шине !6. Следовательно, изменение потенциала шины 16 практически без задержки

1196952 4 передается на первый выход 24, что и обеспечивает высокое быстродействие устройства.