Переключаемый делитель частоты

Иллюстрации

Показать всеРеферат

ПЕРЕКЛЮЧАЕМЫЙ ДЕЛИТЕЛЬ.ЧАСТОТЫ , содержащий блок деления частоты , выход которого соединен с вьгходНой шиной, элемент ШШ, первый, второй и третий D-триггеры, шину управления и шину делимой частоты, которая соединена с тактовыми входами второго и третьего D-триггеров, отличающийся тем, что, с целью повышения быстродействия и увеличения числа ступеней коэффициента деления, в него введены первая и вторая дополнительные шины управления и три элемента И, инверсный вход первого из которых соединен с выходной шиной и с тактовым входом первого D-триггера, информациоаный вход которого соединен с шиной управления , инверсный выход - с прямьм входом первого элемента И, выход которого соединен с информационным Входом второго D-триггера, инверсный (ВЫХОД которого соединей с информационным входом третьего D-триггера и с прямым входом второго элемента И, инверсный вход которого соединен с шиной делимой частоты и с инверсным входом третьего элемента И, I прямой вход которого соединен с версным выходом третьего D-триггера, выход - с первым входом элемента. ИЛИ, второй вход которого соединен . с выходом второго элемента И, выход со счетным входом блока деления частоты , первый и второй входы изменения модуля коэффициента пересчетг которого соединены соответстве первой и второй дополнительным шинами управления.

СО)ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 Н 03 К 23/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

13

ИВЯНАЯ "." е

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

21) 3763021/24-21

22) 29.06.84 (46) 07.12.85. Бюл. И 45 (72) А.С. Сидоров, А.В. Амирханов и В.Г. Куленкамп (53) 621.374.4(088.8) (56) Авторское свидетельство СССР

Ф 769745, кл. Н 03 К 23/04,25.08.79.

IEEE Transactions on Consumer

Electronics< v. СЕ-29, No. 3, Auqust.

1983: Oida et.al. Asingle Chip PLL

With 150MHz Dual Modulus Prescaler, р. 262, Fig. 6. (54)(57) ПЕРЕКЛЮЧАЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий блок деления частоты, выход которого соединен с выходной шиной, элемент ИЛИ, первый, вто-рой и третий D-триггеры, шину управления и шину делимой .частоты, которая соединена с тактовыми входами второго и третьего D-триггеров, отличающийся тем, что, с целью повышения быстродействия и увеличения числа ступеней коэффициента деления, в него введены первая и вторая дополнительные шины управления и три элемента И, инверсный вход первого иэ которых соединен с выходной шиной и с тактовым входом .первого D-триггера, информационный вход которого соединен с шиной управления, инверсный выход — с прямым входом первого элемента И, выход которого соединен с информационным входом второго D-триггера, инверсный выход которого соединен с информационным входом третьего D-триггера и с прямым входом второго элемента

И, инверсный вход которого соединен с шиной делимой частоты и с инверсным входом третьего элемента И, прямой вход которого соединен с инверсным выходом третьего D-триггера, выход — с первым входом элемента .

ИЛИ, второй вход которого соединен . с выходом второго элемента И, выходсо счетным входом блока деления частоты, первый и второй входы изменения модуля коэффициента пересчет которого соедйнены соответства первой и второй дополнительным шинами управления., 1 1197

Изобретение относится к импульс- t ной технике и может быть использовано в цифровых синтезаторах частот.

Цель изобретения — повышение быстродействия и увеличение числа ступеней коэффициента деления.

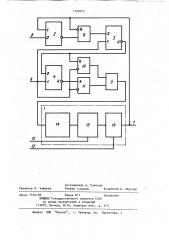

На чертеже приведена электрическая функциональная схема переключаемого делителя частоты.

Устройство содержит блок 1 деле- 10 ния частоты, первый, второй и третий

D-триггеры 2 — 4, элемент ИЛИ 5,. шину 6 делимой частоты, выходную шину 7, шину 8 управления, первый, второй и третий элементы И 9 — 11 и первую и вторую дополнительные шины 12 и 13 управления, при этом шина 6 делимой частоты соединена с тактовыми входами второго и третьего D-vpzrrepqs 3 и 4 и с инверсными входами второго и третьего элементов

И 10 и 11, выход третьего элемента

И 11 соединен с первым входом элемента ИЛИ 5, второй вход которого соединен с выходом второго элемента

И 10, выход которого соединен со счетным входом блока 1 деления частоты, выход которого соединен с выходной шиной 7, с инверсным входом первого элемента И 9 и с тактовым вхо- 30 дом первого D-триггера 2, информационный вход которого соединен с шиной 8 управления, инверсный выход— с прямым входом первого элемента И 9, выход которого соединен с информационным входом второго D-триггера 3, инверсный выход которого соединен с прямым входом второго элемента И 10 и с информационным входом третьего

D-триггера 4, инверсный выход кото- 40 рого соединен с прямым входом треть его элемента И 11. Блок 1 деления частоты состоит из последовательно соединенных каскадов 14 — 16 деления частоты, входы выключения второго и 45 третьего из которых соединены соответственно с первой и второй дополнительными шинами 12 и 13 управления.

Переключаемый делитель. частоты работает следующим образом. 50

На шину 6 подаются импульсы входной делимой частоты, с шины 7 снимаются импульсы выходной поделенной частоты. При подаче на шину 8 высокого логического уровня устройство 55 делит входную частоту на коэффициент равный 2", где и — число задействованных (двоичных) каскадов деления

072 г частоты блока 1. При подаче на шину

8 низкого логического уровня устройство делит входную частоту на коэффициент, равный 2 +1, при подаче ,h на шины 12 и 13 низкого логического уровня каскады 15 и 16 понижают частоту импульсов, поступающих на их входы, соответственно в четыре и в два раза. При подаче на шины 12 и 13 высокого логического уровня каскады 15 и 16 передают импульсы„поступающие на их входы, без изменения по частоте.

В зависимости от соотношения логических уровней на шинах 12„ 13 и 8 переключаемый делитель частоты реализует набор следующих коэффици-! ентов деления: 8 и 9, 16 и 17; 32 и

33; 64 и 65.

Рассмотрим работу устройства в реп жиме деления частоты на 2 и на

2 +1.

В начальном состоянии на шине 8 присутствует высокий логический уровень. При этом на выходе (ниже имеются ввиду только инверсные выходы

D-триггеров 2 — 4) D-триггера 2 и на выходе D-триггера 3 будет присутствовать сигнал с уровнем логического нуля. На выходе D-триггера 3 будет присутствовать сигнал с уровнем логической единицы, а íà выход D-триггера 4 — сигнал с уровнем логического нуля, при этом элемент 10 открыт, а элемент 11 закрыт.

Импульсы входной (делимой) частоты будут поступать с шины 6 через открытый элемент 10 и далее через. элемент 5 на счетный вход блока 1. В результате на шине 7 будет формироваться последовательность импульсов с частотой в 2 раз более низкой, чем частота импульсов на шине.6.

При подаче на шину 6 низкого логического уровня по заднему фронту ближайшего отрицательного выходного импульса устройства на выходе D-триггера 2 формируется сигнал с уровнем логической единицы, при этом элемент

9 открывается.

В следующем полном цикле деления входной частоты отрицательный выходной импульс устройства поступает на инверсный вход элемента 9 и далее с его выхода на информационный вход

D-триггера 3 уже в виде сигнала с уровнем логической единицы.

1197072

По заднему фронту первого отрицательного входного импульса рассматриваемого цикла деления на выходе

D-триггера 3 будет сформирован сигнал с уровнем логического нуля, при этом элемент 10 закрывается. В ре. зультате следующий второй входной импульс не пройдет на, счетный вход блока 1.

Одновременно по заднему фронту второго отрицательного входного импуЛьса на выходе D-триггера 4 будет сформирован сигнал с уровнем логической единицы. При этом элемент 11 откроется. Все последующие.отрицательные входные импульсы, начиная с третьего, начнут вновь. поступать с шины 6, но теперь уже через эле- .. мент 11 и далее. в виде положительных импульсов. через элемент 5 на счетный вход блока 1.

После окончания отрицательного выходного импульса в рассматриваемом цикле деления входной частоты на информационном входе D-триггера 3 устанавливается сигнал с уровнем логического нуля, а по заднему фронту ближайшего отрицательного входного импульса на выходе D-триггера 3 ,вновь. будет сформирован сигнал с уровнем логической единицы, при этом. элемент 10 откроется, Все после-. дующие отрицательные входные импульсы будут поступать через элемент 10 и далее в виде положитель- ных импульсов через элемент 5 на счетный вход блока 1. С задержкой на один такт входной частоты на выходе D-триггера 4 будет сформирован сигнал с уровнем логического нуля и элемент 11 закроется. г

Таким образом, в рассмотренном цикле деления частоты на счетный вход блока 1 поступает число импульсов на единицу меньше, чем число импульсов, поступивших на шину 6.

Очевидно, что до тех пор, пока на шину .8 воздействует .низкий логический уровень, в каждом полном цикле деления входной частоты каждый второй входной импульс (считая с момента поступления выходного импульса на информационный вход D-триггера 3) не достигнет счетного входа блока 1.

Исключение одного счетного импульса в каждом цикле деления входной частоты приведет к увеличению длительности положительного полупериода выходной частоты устройства на величину одного периода входной частоты и равносильно увеличению.на единицу коэффициента деления переключаемого делителя частоты.

Таким образом, при наличии на шине 8 сигнала низкого логического уровня на шине 7 будет формироваться последовательность импульсов с

t5 частотой 2 +1 раз более низкой, . ем частота импульсов на шине 6.

После подачи на шину 8 высокого логического уровня по заднему фронту

20. ближайшего отрицательного импульса .выходной частоты на выходе D-триггера 2 вновь будет сформирован сигнал с уровнем логического нуля, запрешающий прохождение. через элемент

25 9 на информационный вход D-триггера

3 всех последующих импульсов выходной частоты. Одновременно на выходе

D-триггера по заднему фронту ближайшего отрицательного импульса входной частоты будет сформирован сигнал с уровнем логической единицы, а по заднему фронту следующего отрицательного импульса входной частоты сигнал с уровнем логического нуля будет сформирован на выходе D-триггера 4, при этом элемент 10 открывается, а элемент 11 с задержкой на один период входной частоты закрывается. Все без исключения импульсы

40 входной частоты будут поступать с шины 6 через открытый элемент 10 и далее через элемент 5 на счетный вход блока 1. В результате переключаемый делитель частоты в этом ре45 жиме имеет коэффициент деления, равный 2".

Задержка. прохождения импульсов входной частоты через идентичные по структуре и параметрам элементы

10 и ll, а также через элемент 5 не влияет на максимальную рабочую частоту переключаемого. делителя частоты, которая в этом случае будет определяться только быстродействием ис-. пользуемых триггерных каскадов.

1197072

Составитель А. Соколов

Техред З.Палий Корректор А. Обручар

Редактор Л. Зайцева

Подписное г. Ужгород, ул. Проектная, 4

Филиал ППП "Патент", Заказ 7576/58 Тираж 871

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5