Устройство для автоматического измерения характеристик дискретного канала связи

Иллюстрации

Показать всеРеферат

Изобретение повышает достоверность определения вероятности ошибок при нарушении синхронизма. При синфазной работе и отсутствии искажений во входной испытательной последовательности (ВИЛ) на эыходе 2-го сумматора (С) 2 по модулю два формируется сигнал с уровнем логического О. При нарушении синхронизма или наличии ошибок формируется сигнал с урон нем логической. 1. При нарушении синхронизма и отсутствии ошибки в процессе проверки ВИП на рекуррентность на оба входа злемента И 8 поступают сигналы с уровнем логической 1. Коррекция фазы 2-го рекург рентного регистра 4 производится сигналом с выхода злемента И 8. Так как сигнал, разрешающий работу элемента И 8, поступает со счетчика 7 нулей после окончания приема без ошибочного.интервала во входной последовательности , вероятность ложного включения цикла фазирования близка к нулю. 1 ил. СО СО

СОЮЗ СОВЕТСКИХ

С0ЦЮЛИСТИЧЕСНИХ

РЕСПУБЛИН

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Г1О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3795427/24-09 (22) 25.09.84 (46) 07.12 ° 85. Бюл. У 45 (72) О. В. Бузовский, Н, М. Павлишин

В. М. Саух и С. С, Шевченко (53) 621.396.664(088.8) (56) Авторское свидетельство СССР . У 660276, кл. Н 04 В 3/46, )973, Авторское свидетельство СССР

У 780210, кл. Н 04 В 3/46, 1975. (54) УСТРОЙСТВО ДЛЯ. АВТОМАТИЧЕСКОГО

ИЗИЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО

КАНАЛА СВЯЗИ (57) Изобретение повышает достоверность определения вероятности ошибок при нарушении синхронизма. При синфазной работе и отсутствии искажений во входной испытательной последовательности (ВИП) на выходе 2-ro сум(59 4 Н 04 В 3/46 //Н 04 L 11/08

I матора (С) 2 по модулю два формируется сигнал с уровнем логического "0".

При нарушении синхронизма или наличии ошибок формируется сигнал с уров нем логической. "1". При нарушении синхронизма и отсутствии ошибки в процессе проверки ВИП на рекуррентность на оба входа элемента И 8 поступают сигналы с уровнем логичесl I I t кои 1 . Коррекция фазы 2-го рекург рентного регистра 4 производится сигналом с выхода элемента И 8. Так как сигнал, разрешающий работу элемента И 8, поступает со счетчика 7 нулей после окончания приема без а ошибочного интервала во входной поЮ следовательности, вероятность ложного включения цикла фазирования близка к нулю. 1 ил. С:

1197103

Изобретение относится к электро-! связи и может использоваться для иэ мерения статистических характеристиь дискретного канала связи (ДКС).

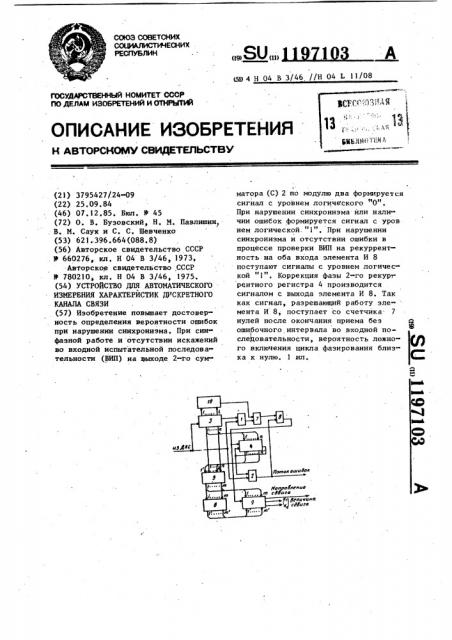

Цель изобретения — повышение достоверности определения вероятности ошибок в принимаемой информации при нарушении синхронизма, На чертеже изображена структурная электрическая схема устройства. 16

Устройство для автоматического измерения характеристик дискретного канала связи содержит первый и второй умматоры 1 и 2 по модулю два, первый второй рекуррентные регистры 3 и 15 постоянный запоминающий блок 1ПЗБ)

5, регистр 6 памяти, счетчик 7 нулей, элемент И 8, блок 9 вычитания, дешифратор 10 нулевого состояния.

Устройство работает следующим об- 20 разом.

Исходное состояние устройства мо жет быть произвольным и на процесс работы не влияет. Принимаемая испыта3 тельная последовательность с входа 25 устройства поступает на вторые входы первого и второго сумматоров 1 и

2 по модулю два, а также на вход первого рекуррентного регистра 3, сигнал с выхода которого поступает на пер- 30 вый вход первого сумматора 1 па модулю два. В первом сумматоре 1 по модулю два испытательная последовательность проверяется на рекуррентность.

Результат проверки с выхода первого сумматора 1 по модулю два поступает на счетчик 7 нулей.

При соответствии испытательной последовательности рекуррентной последовательности на выходе первого сумматора 1 по модулю два образуется нулевая последовательность, которая приводит к переполнению счетчика 7 нулей, сигнал с выхода которого раз45 решает работу элемента И 8. При несоответствии испытательной последовательности рекуррентной последовательности на выходе первого сумматора по модулю два формируется сигнал, устанавливающий счетчик 7 нулей в нулевое состояние.

Счетчик 7 нулей может быть устам ° новлен в нулевое состояние также сигналом с выхода дешифратара 10 нулевого состояния в том случае, если на его входы поступит нулевая комбинация, Во втором сумматоре 2 по модулю два испытательная последовательность

1 сравнивается с эталонной, поступающей со второго рекуррентного регистра

4, и результат. этого сравнения, представляющий собой поток ошибок, поступает на выход устройства и на первый вход элемента И 8. При приеме каждого бита испытательный последовательности первый и второй рекуррентные регистры 3 и 4 поочередно подключаются к входам ПЗБ 5. В каждый данный момент времени на выходе ПЗБ появляется кодовая комбинация, определяющая номер такта, поступившего на вход первого или второго рекуррентных регистров 3 и 4. Кодовая комбинация, определяющая номер такта, эквивалентного состоянию входной испытательной последовательности, записывается в регистр 6 памяти, с выходов которого она поступает на входы блока 9 вычитания.

При синфазной работе и отсутствии искажений во, входной испытательной последовательности на выходе второго сумматора 2 по модулю два формируется сигнал с уровнем логического "0".

При нарушении синхронизма или наличии ошибок во входной испытательной последовательности на выходе второго сумматора 2 по модулю два формируется сигнал с уровнем логической "1".

При нарушении синхронизма и от- сутствии ошибки в процессе проверки входной испытательной последовательности на рекуррентность, на оба входа элемента И 8 поступают сигналы с уровнем логической "1". На выходе элемента И 8 формирует< я сигнал вклю- чения цикла фазирования в процессе которого определяется величина и на правление расфазирования и корректи- руется фаза второго рекуррентного регистра 4.

Величина и направление расфазирования определяются блоком 9 вычитания. Вычитание производится в двоичном коде. На первом выходе блока

9 вычитания формируется сигнал, указывающий на направление сдвига, на остальных выходах — сигналы, определяющие величину сдвига. Выходы блока 9 вычитания являются выходами устройства.

Коррекция фазы второго рекуррентного регистра 4 производится сигналом с выхода элемента И 8 путем переза1197

"р тч .рр 1

Формула из обре тения

Составитель А. СеселкинРедактор П. Коссей Техред M.Íàäü Корректор С„ Черни

Заказ 7631/59 Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж»35, Раушская наб,, д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 писи входной испытательной последовательности с выхода первого рекуррентного регистра 3 во второй рекуррентный регистр 4. Так как сигнал, разрешающий работу элемента И 8. поступает со счетчика 7 нулей после окон» чания приема безошибочного интервала во входной последовательности, вероятность ложного включения цикла фаэирования близка к нулю. 10

Описанная схема позволяет определить наличие расфазирования за время где Т вЂ” период тактовой частоты; тц

N — количество р аз рядо 1. р екурPP рентного регистра которое меньше времени, затрачиваемого на определение состояния расфазирования в известном устройстве на величину

Ьсp = 2Ттч . Ырр-2Ттч N pp Ттц Npp

Вхождение в. синхрониэм производит- 25 ся в течение текущего такта в момент включения цикла фаэирования, т. е. за время Т ч . Таким образом, уменьшение времени вхождения в синхрониэм со1 ставляет величину 30 д = Тт„(M+i)-T Tu = Ттч t(M+i)-1) где М - число бит принимаемой инфор- мации; — число вставленных нли выпавших бит..

Устройство для автоматического

40 измерения характеристик дискретного

103 4 канала связи, содержащее последовательно соединенные первый рекуррентный регистр, дешифратор нулевого состояния и счетчик нулей, регистр памяти, первый сумматор по модулю два, первый вход которого соединен с сигнальным выходом первого рекур.рентного регистра, второй рекуррент,ный регистр,-сигнальный выход и первый вход которого подключены к первому входу сумматора по модулю два, выход котарого подключен к первому входу элемента И, о т л и ч а ю— щ е е с я тем, что, с целью повышения достоверности определения вероятности ошибок в принимаемой информации при нарушении синхронизма в не го введены последовательно соединен» ные постоянный запоминающий блок и блок вычитания, другая группа входов которого соединена с выходами постоянного запоминающего блока через регистр памяти, при этом выход счетчи- . ка нулей подключен к второму входу элемента И, выход которого подключен к второму входу второго рекуррентного регистра и к управляющему входу блока вычитания, вторан группа выходов первого рекуррентного регистра подключена к группе входов второго рекуррентного регистра и к первой группе входов постоянного запоминающего блока, вторая группа входов которого соединена с группой выходов второго рекуррентного регистра, сигнальный вход первого рекуррентного регистра соединен . с вторыми входами первого и второго сумматоров по модулю два, выход первого сумматора по модулю два подключен к второму, выходу счетчика нулей.