Детектор сигналов относительной фазовой манипуляции

Иллюстрации

Показать всеРеферат

ДЕТЕКТОР СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ, содержа1ций последовательно соединенные квадратор, фильтр, делитель частоты, фазовый детектор, блок задержки и перемножитель, другой вход которого соединен с выходом фазового детектора , о тличающийся тем, что, с целью повышения достоверности принимаемой информации, в него введены последовательно соединенные амплитудный ограничитель, дополниДгтельный блок задержки и первый вычитатель , фазовращатель, второй, третий и четвертый вычитатели, два амплитудных детектора и переключатель , причем выход амплитудного ограничителя соединен с входом квадратора , выход делителя частоты соединен с первым входом второго вычитателя и через фазовращатель с первым входом третьего вычитателя, второй вход которого и второй вход второго вычитателя соединены с выходом амплитудного ограничителя, выходы второго и третьего вычитателей соединены с первым и вторым входами переключателя , а также через соответствуюп(ие амплитудные детекторы - с соответстсл вующими входами четвертого вычитателя , выход которого соединен с третьим входом переключателя, выход которого соединен с вторым входом первого вычитателя, выход которого соединен с вторым входом фазового детектора.

СО1ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (И) kg) g Н 04 L 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

КЕСОЮЗй 4"..

К АВТОРСКОМ .Ф СВ ТЕЛЬСТБУ

ЬИ Ь.Ч ИВTN.:

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 3767568!24-09 (22) 19.07.84 (46) 07.12.85. Бюл. В 45 (71) Всесоюзный заочный-электротехнический институт связи (72) Н.Т. Петрович (53) 621.396.62(088.8) (56) Зюко А.Г. и др. Теория передачи сигналов. М.: Связь, 1980, с. 142-143. (54) (57) ДЕТЕКТОР СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ, содержащий последовательно соединенные квадратор, фильтр, делитель частоты, фазовый детектор, блок задержки и перемножитель, другой вход которого соединен с выходом фазового детек- . тора, отличающийся тем, что, с целью повышения достоверности принимаемой информации, в него введены последовательно соединенные амплитудный ограничитель, дополнительный блок задержки и первый вычитатель, фазовращатель, второй, . третий и четвертый вычитатели, два амплитудных детектора и переключа1 тель, причем выход амплитудного ограничителя соединен с входом квадратора, выход делителя частоты соединен с первым входом второго вычитателя и через фазовращатель с первым входом третьего вычитателя, второй вход которого и второй вход второго вычитателя соединены с выходом амплитудного ограничителя, выходы второго и третьего вычитателей соединены с первым и вторым входами переключатеO ля, а также через соответствующие В амплитудные детекторы — с соответствующими входами четвертого вычитателя, выход которого соединен с третьим входом переключателя, выход которого соединен с вторым входом первого Я вычитателя, выход которого соединен с вторым входом фазового детектора.!

Составитель Н. Лазарева

Редактор А. Ворович Техред А.Кикемезей Корректор С. Шекмар

Заказ 7633/61 Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

1 11

Изобретение относится к электросвязи-, а именно к системам передачи информации.

Цель изобретения — повышение,достоверности принимаемой информации.

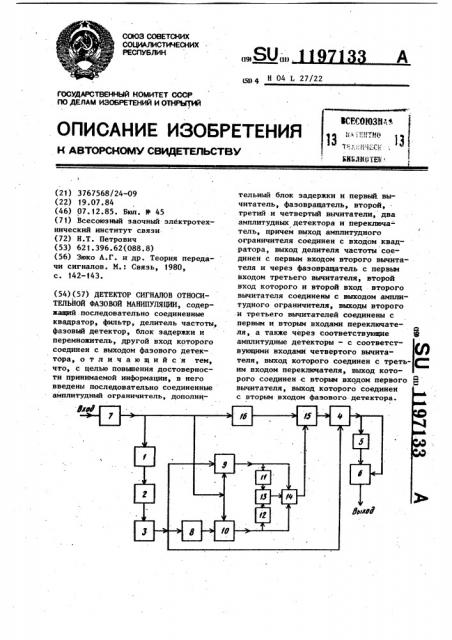

На чертеже изображена структурная электрическая схема предлагаемого детектора.

Детектор сигналов относительной фазовой манипуляции содержит квадратор 1, фильтр 2, делитель 3 частоты, фазовый детектор 4, блок 5 задержки, перемножитель 6, амплитудный ограничитель 7, фазовращатель 8, вычитатели 9 и 10, амплитудные детекторы 11 и 12, вычитатель 13, пере-, ключатель 14, вычитатель 15 и допол-, нительный блок 16 задержки.

Детектор работает следующим обра-:. зом.

Входной сигнал поступает на амплитудный ограничитель 7, обеспечивающий постоянство амплитуды сигнала на своем выходе, необходимое для осуществления компенсации помех. Квадратор 1, фильтр 2 и делитель 3 частоты формируют опорное напряжение, очищенное от помех. Фаэовращатель 8 создает напряжение, сдвинутое по от-. ношению к напряжению на выходе дели- . о .теля 3 частоты на 180 . Затем эти два опорных напряжения вычитаются из входного сигнала, создавая тем самым напряжение помехи, очищенное

97133

2 . от сигнала, но возникающее то на выходе вычитателя 9, то на выходе вычитателя 10. Случайное их чередование определяется фазами несущего колебания входного сигнала, т.е. последовательностью передаваемых двоичных сигналов. Далее вычитатель 13 образует разность напряжений с выходов амплитудных детекторов 11 и 12. Эта разность напряжений может быть положительной или отрицательной и управляет переключателем 14 так, что на

его выход проходят только помехи, очищенные от сигнала, т.е. переключатель 14 сводит помехи, очищенные от сигнала и возникающие то на выходе вычитателя 9, то на выходе вычитателя 10, в одну цепь.

Отделенные от сигнала и сведенные в одну цепь помехи вычитаются из смеси (сигнал+помеха) с помощью вычитателя 15 и тем самым существенно снижается уровень помех на выходе фазового детектора 4. При этом, в д связи с некоторой задержкой напряжения на выходах амплитудных детекторов 11 и 12, необходимо на это время задержать сигнал„поступающий . на вычитатель .15. Это осуществляет блок 16 задержки. Время задержки и постоянная времени нагрузки амплитудных детекторов 11 и 12 выбирается порядка 1О-15Х от длительности элементарной посылки оо.