Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией

Иллюстрации

Показать всеРеферат

АВТОКОРРЕЛЯЦИОННЫЙ ПРИЕМНИК СИГНАЛОВ С ДВУКРАТНОЙ ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ, содержащий (ций блок, выход которого соединен с первыми входами перемножителей функции, выходы которых соединены с входами соответствующих интеграторов, фазовращатель, выход которого соединен с вторым входом первого перемножителя функций, второй вход второго перемножителя функций и вход фазовращателя объединены и являются входом приемника, отличающийся тем. что, с целью повышения помехоустойчивости путем компенсации воздействия нестабильности частоты несущей , в него введены регулируемый фазовращатель, два компаратора, элемент И, два .ключа, два накопителя и дифференциальный усилитель, при.чем вход регулируемого фазовращателя является входом приемника, а выход соединен с входом запоминающего блока, выходы интеграторов являются выходами приемника и соединены с первыми входами соответств5тощих ключей и входами соответствукмцих компараторов, выходы которых соединены с входами элемента И, выход которого соединен с вторыми сл входами ключей, выходы которых через соответствзпощие накопители соединены с входами .дифференциального усилителя, выход которого -соединен . с управляющим входом регулируемого Фазовращателя.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (51) У Н 04 L 2j/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOIVIY СВИДЕТЕЛЬСТВУ и.I

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3778767/24-09 (22) 06.08.84 (46) 07.12.85. Бюл. Ф 45 (72) В.Э. Черный, Э.А. Вайс и С.С. Тарасов (53) 621.396.62 (088.8) (56) Заездный А.M. и др. Фазоразностная модуляция. М.: Связь, 1967, с. 27-28. (54)(57) АВТОКОРРЕЛЯЦИОННЫЙ ПРИЕМНИК СИГНАЛОВ С ДВУКРАТНОЙ ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ, содержащий запоминающий блок, выход которого соединен с первыми входами перемножителей функции, выходы которых соединены с входами соответствующих интеграторов, фазовращатель, выход которого соединен с вторым входом первого перемножителя функций, второй вход второго перемножителя функций и вход фазовращателя объединены и являются входом приемника, отличающийся тем, что, с целью повышения помехоустойчивости путем компенсации воздействия нестабильности частоты несущей, в него введены регулируемый фазовращатель, .два компаратора, элемент И, два ключа, два накопителя и дифференциальный усилитель, при.-. чем вход регулируемого фазовращателя является входом приемника, а выход соединен с входом запоминающего .блока, выходы интеграторов являются выходами приемника и соединены с первыми входами соответствующих ключей и входами соответствующих.компараторов, выходы которых соединены с входами элемента И, выход которого соединен с вторыми входами ключей, выходы которых через соответствующие накопители соединены с входами, дифференциального усилителя, выход которого .соединен . с управляющим входом регулируемого

»1)азовращателя.

Составитель Н. Лазарева

Редактор А. Ворович Техред А.Бабинец Корректор Л. Пилипенко

Заказ 7633/6 1 Тираж 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная,4

4 1

Изобретение относится к радиосвязи и может использоваться при разработке цифровых радиосредств с фазоразностной модуляцией.

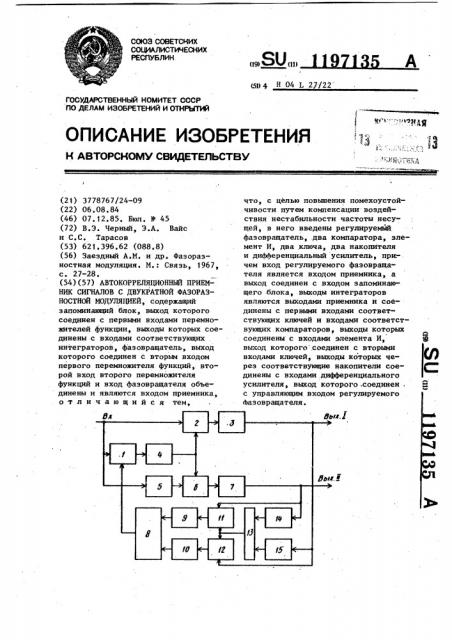

Цель изобретения — повышение помехоустойчивости путем компенсации воздействия нестабильности частоты несущей. ф На чертеже изображена структур,а . ная электрическая схема предлагаемого автокорреляционного приемника.

Автокорреляционный приемник с двукратной фазоразностной модуляцией содержит регулируемый фазовращатель 1, перемножитель 2 функций, ! интегратор 3, запоминающий блок 4, фазовращатель 5, перемножитель 6 функций, интегратор 7, дифференциальный усилитель 8, накопители

9 и 10 ° ключи 11 и 12, элемент И 13 и компараторы 14 и 15.

Автокорреляционный приемник сигналов с двукратной фазоразностной модуляцией работает следующим образом.

Сигнал с входа приемника поступает непосредственно на «черемножитель

2 функций и через фаэовращатель .

5, обеспечивающий сдвиг фаз П/2 на перемножитель 6. На другие входы перемножителей 2 и 6 входной сигнал поступает через регулируемый фазовращатель 1 и запоминающий блок 4, хранящий информацию о предыдущей

197135 2 посыпке. Регулируемый фазовращатель

1 обеспечивает постоянную величину сдвига фазы сигнала на выходе запоминающего блока 4 по отношению к входному сигналу на П/4.

После перемножения и интегрирования на выходах интеграт оров 3 и 7 формируют переданные в каналах двоичные сигналы.

10 Выходы интеграторов 3 и 7 подключены к входам компараторов 14 и 15 и входам ключей 11 и 12. Ключи 11 и 12 открываются под действием управляющего сигнала, вырабатываемого

15 элементом И 13, на входы которого поступают сигналы логической единицы только тогда, когда напряжение на входах компараторов 14 и 15 имеет положительный знак.

zp Выходы ключей 11 и 12 соединены с входами накопителей 9 и 10, которые усредняют величину сигнала с выходов интеграторов . Выходы накопителей 9 и 10 подключены к входам

25 дифференциального усилителя 8, на выходе которого формируется сигнал ошибки, управпяющий работой регулируемого фазовращателя 1, компенсирующего сдвиг .фаэ, возникающего щ между поступающими на перемножители функций напряжениями и, тем самым, исключающего уменьшение помехоустойчивости вследствие воздействия нестабильности несущей.