Двухполярный стабилизатор с быстродействующей защитой

Иллюстрации

Показать всеРеферат

ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР С БЫСТРОДЕЙСТВУЮЩЕЙ ЗАЩИТОЙ, содержащий первый регулирующий транзистор , подключенный коллектором к плюсовой входной клемме, первый измерительный резистор, включенный между эмиттером первого регулирующего транзистора и выходной плюсовой клеммой, первые - дополнительный и защитный транзисторы, имеющие одинаковый с первым регулирующим транзистором тип проводимости, причем база первого дополнительного транзистора подключена к эмиттеру первого регулирующего транзистора, а эмиттер - к базе первого защитного транзистора, коллектор которого подключен к базе первого регулирующего транзистора, а эмиттер - к плюсовой выходной клемме, второй регулирующий транзистор другого типа проводимости, чем первый регулирующий транзистор, подключенный коллектором к плюсовой входной клемме, второй измерительный резистор, включенный между эмиттером второго регулирующего транзистора и выходной минусовой клеммой, вторые - дополнительный и защитный транзисторы, имеющие одинаковый с вторым регулирующим транзистором тип проводимости , причем база второго дополнительного транзистора подключена к эмиттеру второго регулирующего транзистора , а эмиттер - к базе второго защитного транзистора, коллектор которого подключен к базе второго регулирующего транзистора,а эмиттер к минусовой выходной клемме, первый и второй управляющие транзисторы , эмиттеры которых соответственно подключены к коллекторам первого и второго регулирующих транзисторов, базы соответственно - к коллекторам первого и второго дополнительных транзисторов, а коллектор второго управляющего транзистора под (О ключен к базе первого управляющего транзистора, причем тип проводимости управляющего транзистора противоположен типу проводимости регулирующего транзистора, блоки управления плюсового и минусового каналов, узел синхронизации, состоящий из делителя напряжения, операционного СО СХ) усилителя, первого и второго управляющих транзисторов узла синхрони со зации и электронного ключа, причем делитель напряжения включен между САЭ плюсовыми и минусовыми выходными клеммами, неинвертирующий вход операционного усилителя подключен к общей шине, а инвертирующий - к средней точке делителя, управляющие резисторы узла синхронизации имеют разные типы проводимости, базы объединены и имеют точкой подключения выход операционного усилителя, а эмиттеры - общую шину, управляющий вход электронного ключа подключен к коллектору первого управляющего

СОЮЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (21) 3750263/24-07 (22) 07.06.84 (46) 15.12,85. Бюл. Р 46 (72) N.È. Кукушкин (53) 621.316.722,1 (088.8) (56) Авторское свидетельство СССР

В 828187, кл. G 05 F 1/58, 1981.

Авторское свидетельство СССР

У 721810, кл. С 05 F 1/58. 1977. (54)(57) ДВУХПОЛЯРНЫЙ СТАБИЛИЗАТОР

С БЫСТРОДЕЙСТВМОЩЕЙ ЗАЩИТОЙ, содержащий первый регулирующий транзистор, подключенный коллектором к плюсовой входной клемме, первый измерительный резистор, включенный между эмиттером первого регулирующего транзистора и выходной плюсовой клеммой, первые — дополнительный и защитный транзисторы, имеющие одинаковый с первым регулирующим транзистором тип проводимости, причем база первого дополнительного транзистора подключена к эмиттеру первого регулирующего транзистора, а эмиттер — к базе первого защитного транзистора, коллектор которого подключен к базе первого регулирующего транзистора, а эмиттер — к плюсовой выходной клемме, второй регулирующий транзистор другого типа проводимости, чем первый регулирующий транзистор, подключенный коллектором к плюсовой входной клемме, второй измерительный резистор, включенный между эмиттером второго регулирующего транзистора и выходной минусовой клеммой, вторые - дополнительный и защитный транзисторы, имеющие одинаковый с вторым регулирующим транзистором тип проводимос(51) 4 G 05 F 1/569 // С.05 F 1/585 ти, причем база второго дополнительного транзистора подключена к эмиттеру второго регулирующего транзистора, а эмиттер — к базе второго защитного транзистора, коллектор которого подключен к базе второго регулирующего транзистора,а эмиттер— к минусовой выходной клемме, первый и второй управляющие транзисторы,эмиттеры которых соответственно подключены к коллекторам первого и второго регулирующих транзисторов, базы соответственно — к коллекторам первого и второго дополнительных транзисторов, а коллектор второго управляющего транзистора подключен к базе первого управляющего транзистора, причем тип проводимости управляющего транзистора противоположен типу проводимости регулирующего транзистора, блоки управления плюсового и минусового каналов, узел синхронизации, состоящий из делителя напряжения, операционного усилителя, первого и второго управляющих транзисторов узла синхронизации и электронного ключа, причем делитель напряжения включен между плюсовыми и минусовыми выходными клеммами, неинвертирующий вход операционного усилителя подключен к общей шине, а инвертирующий — к средней точке делителя, управляющие резисторы узла синхронизации имеютразные типы проводимости, базы объединены и имеют точкой подключения выход операционного усилителя, а эмиттеры — общую шину, управляющий вход электронного ключа .подключен к коллектору первого управляющего

11 транзистора, о т л и ч а ю щ и йс я тем, что, с целью повьппения эффективности работы стабилизатора путем увеличения скорости отслеживания напряжений в режиме работы с перегрузкой по току одного из каналов и повышения точности отслеживания напряженйй вплоть до нуля, в, I узел синхронизации введены первый и второй дополнительные регулирующие транзисторы разного тира проводимости, эмиттеры которых соединены соответственно с коллекторами первого и второго регулирующих транзисторов, причем тип проводимости дополнительного регулирующего транзистора противоположен типу проводимости pery98493 лирующего транзистора, коллектор первого дополнительного регулирующего транзистора подключен к минусовой выходной клемме, а коллектор второго дополнительного регулирующего транзистора к плюсовой выходной клемме, база первого дополнительного регулирующего транзистора подключена к коллектору первого управляющего транзистора узла синхронизации, база второго дополнительного регулирующего транзистора— к коллектору второго управляющего транзистора узла синхронизации, а электронный управляемый ключ включен между выходом операционного усилителя и его инвертирующим входом.

Изобретение относится к электротехнике и может быть использовано при построении источников питания постоянного напряжения.

Цель изобретения — .повышение 5 эффективности работы стабилизатора путем увеличения скорости отслеживания напряжений в режиме работы с перегрузкой по току одного из каналов и повышения точности отслеживания напряжений вплоть до нуля.

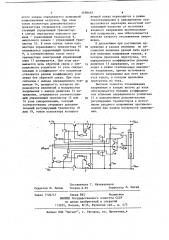

На чертеже представлена электрическая схема двухполярного стабилизатора с быстродействующей защитой .

Стабилизатор содержит первый регулирующий транзистор 1, первый узел защиты, состоящий из первого измерительного резистора 2, первых дополнительного и защитного транзисторов .3 и 4, второй регулирующий транзистор 5, второй узел защиты, состоящий из второго измерительного резистора

6 и вторых дополнительного и защитного транзисторов 7 и 8, узел управления, состоящий из первого и второго управляющих транзисторов

9 и 10, схем унравления плюсового и минусового каналов 11 и 12, узел синхронизации, состоящий из делителя 13 напряжения операционного ЗО

У усилителя 14, первого и второго управляющих транзисторов 15 и 16 узла синхронизации, электронного

2 управляемого ключа l7 первый и второй дополнительные регулирующие транзисторы 18 и 19. Дополнительный источник питания для операционного усилителя 14 на чертеже не показан.

Стабилизатор работает следующим образом.

До момента срабатывания одного иэ ограничителей тока стабилизатор работает в режиме стабилизации выходного напряжения, определяемом работой схем управления каналов 11 и 12. При этом электронный управляемый ключ 17 замкнут и коэффициент передачи операционного усилителя

14 близок к О, как и напряжение на его выходе. Управляющие транзисторы 15 и 16 узла синхронизации заперты, соответственно как заперты и дополнительные регулирующие транзисторы 18 и 19. В целом узел син хронизации не оказывает влияния на работу стабилизатора. При превышении тока нагрузки порога срабатывания токоограничителя любого из каналов открываются соответственно дополнительный и защитный транзис-, торы. При этом защитный транзистор начинает шунтировать база-эмиттерный переход соответствующего регулМруюцего транзистора, переводя этот канал в режим работы стабилизатора тока. Величина напряжения на выходе

11984

+ Ма

Ящи

Составитель Г. Мачавариани

Редактор М. Дылын Техред А.Ач Корректор о Л. Патай

Тираж 862 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 7720/47

Филиал ППП "Патент", г. Ужгород, ул. Проектная,4 этого канала определяется величиной сопротивления нагрузки. При этом током коллектора дополнительного транзистора открывается соответствующий управляющий транзистор: в случае перегрузки плюсового канала — управляющий транзистор 9, минусового канала — управляющий транзистор 10. В этом случае током коллектора управляющего транзистора 10 tp открывается управляющий транзистор

9, а соответственно током этого транзистора электронный управляемый ключ 17 размыкается. При этом размыкается цепь обратной связи с операционного усилителя 14 узла синхронизации и коэффициент его усилителя становится равным коэффициенту усиления без обратной связи. При этом сигналом с выхода операционного уси- 2о лителя 14, полярность которого оп ределяется величиной и полярностью напряжения с выхода делителя 13 напряжения, открывается соответствующий управляющий транзистор 15 или д

16 узла синхронизации, который соответственно открывает дополнительный регулирующий транзистор 18

:mm 19, током коллектора которого

93 4 второи канал переводится в режим токоограничения и одновременно осуществляется перезаряд емкостной составляющей нагрузки от источника входного напряжения противоположной полярности, чем обеспечивается высокая скорость отслеживания напряжения.

В дальнейшем при достижении напряжения в канале величины по абсолютной величине равной либо крат.ной величине напряжения канала, в котором произошла перегрузка, что определяется коэффициентом деления делителя 13 .напряжения, он переходит в режим стабилизации выходного напряжения, причем источником опорного напряжения для него является канал, в котором произошла перегрузка по току.

Высокая точность отслеживания напряжения в канале вплоть до нуля обеспечивается большим коэффициентом усиления операционного усилителя

14 и подключением дополнительных регулирующих транзисторов к источникам входного напряжения противоположной для канала полярности напряжения.