Устройство для адресации блоков памяти

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ БЛОКОВ ПАМЯТИ, содержащее переключатели , первую группу элементов И, регистр адреса, выход которого подключен к входу дешифратора адреса, причем выходы переключателей соединены с первыми входами элементов И группы, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены матрица последовательно соединенных элементов И и триггеров, группы элементов ИЛИ с первой по третью, элементы задержки, группы элементов И с второй по четвертую, элементы НЕ, входы которых, соединены с выходами переключателей,а выходы - с первыми входами элементов И четвертой группы, вторые входы которых являются тактовым входом устройства, третий вход каждого элемента И четвертой группы , кроме первого, соединен с выходом предыдущего элемента задержки , выход каждого элемента И четвертой группы, кроме первого,подключен к первому входу одноименного элемента ИЛИ третьей группы, второйвход которого соединен с выходом одноименного элемента И третьей группы, первьй вход каждого элемента И третьей группы подключен к выходу одноименного элемента НЕ, а второй вход - к выходу предьиущего элемента ИЛИ третьей группы и первому входу одноименного элемента И второй групчы, второй вход которого соединен с выходом одноименного переключателя, а выход - с первым входом одноименного элемента ИЛИ второй группы, второй вход которого подключен к S выходу одноименного элемента И первой группы, второй вход которого (Л соединен с тактовым входом устройства , а третий вход подключен к выходу предьщущего элемента задержки , выход каждого элемента ИЛИ второй группы соединен с первыми входами элементов И одноименной строки матрицы, вторые.входы элементов И со 00 ел каждого столбца матрицы подключены к соответствующему выходу дешифратора адреса, выходы элементов И каждой строки матрицы подключены к О) ел соответствующему входу одноименного . элемента ИЛИ первой группы, инверсный выход каждого триггера соединен с соответствующими входами элементов И одноименных строки и столбца матрицы, кроме одноименного элемента И матрицы, выходы элементов ИЛИ первой группы соединены с входами соответствующих элементов задержки и являются выходами устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2I) 3756861/24-24 (22) 18.06.84 (46) 15.12.85. Бюл. № 46 (72) В.П.Невский, В.Н.Горшков и В.И.Агибалов (53) 681.327(088,8) (56) Авторское свидетельство СССР № 764518, кл; 0 06 Р 13/00, 1980.

Авторское свидетельство СССР

¹ 1024926, кл. (: 06 F 13/00, 1983, (54)(57) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ

БЛОКОВ ПАМЯТИ, содержащее переключатели, первую группу элементов И, регистр адреса, выход которого подключен к входу дешифратора адреса, причем выходы переключателей соединены с первыми входами элементов

И группы, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены матрица последовательно соединенных элементов И и триггеров, группы элементов ИЛИ с первой по третью, элементы задержки, группы элементов И с второй по четвертую, элементы HE входы которых. соединены с выходами переключателей; а выходы — с первыми входами элементов И четвертой группы, вторые входы которых являются тактовым входом устройства, третий вход каждого элемента И четвертой группы, кроме первого, соединен с выходом предыдущего элемента задержки, выход каждого элемента И четвертой группы, кроме первого,подключен к первому входу одноименно„„SU„„ I 198565 A

СЯ)W G 11 С 8/00 го элемента ИЛИ третьей группы, второй вход которого соединен с выходом одноименного элемента И третьей группы, первый вход каждого элемента И третьей группы подключен к выходу одноименного элемента НЕ, а второй вход — к выходу предыдущего элемента ИЛИ третьей группы и первому входу одноименного элемента И вгорой групчы, второй вход которого соединен с выходом одноименного переключателя, а выход — с первым входом одноименного элемента ИЛИ второй группы, второй вход которого подключен к выходу одноименного элемента И первой группы, второй вход которого соединен с тактовым входом устройства, а третий вход подключен к выходу предыдущего элемента задержки, выход каждого элемента ИЛИ второй группы соединен с первыми входами элементов И одноименной строки матрицы, вторые. входы элементов И каждого столбца матрицы подключены к соответствующему выходу дешиф- . ратора адреса, выходы элементов И каждой строки матрицы подключены к соответствующему входу одноименного, элемента ИЛИ первой группы, инверсный выход каждого триггера соединен с соответствующими входами элементов И одноименных строки и столбца матрицы, кроме одноименного элемента И матрицы, выходы элементов ИЛИ первой группы соединены с входами соответствующих элементов задержки и являются выходами устройства.

119856э

Изобретение относится к вычислительной технике, в частности к уст: ройствам управления основной памятью.

Целью изобретения является повышение быстродействия устройства.

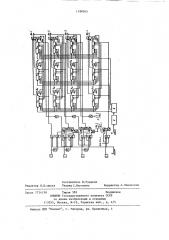

На чертеже приведена функциональная схема предложенного устройства.

Устройство для адресации блоков памяти содержит переключатели 1, служащие для отключения блоков памяти, регистр 2 адреса, первую груп" пу элементов И 3, адресный 4 и тактовый 5 входы, дешифратор 6 адреса, матрицу последовательно соединенных лементов И 711» и» 1п»

2 » 22» .. » zn» ., »7п »7ор » nn u триггеров 81„,81 » ...81,8 1 82

8„

2и ,...,8„„,8„,...,8„, первую групп пй п пу элементов KIH 91,92 "9„ эле менты HE 10, элементы 11„,11

1 1д1 задержки вторую группу И 12

1 29»... 1 2 „, вторую группу элементов ИЛИ 13 » 13 » ..,,13„, третью группу элементов И 14,145,...,14„„ третью группу элементов ЙЛИ 15

15> » 15> 1, четвертую группу элементов Й 16„,16 ...,,16, где

n — - число блоков памяти.

Принцип работы устройства заключается в предоставлении поступившей заявке первого неотключенного и незанятого блока памяти.

Устройство работает следующим образом.

Совокупность блоков памяти, подлежащих распределению, задается путем установки в соответствующее положение переключателей 1 ("О"— блок отключен, "1" — блок включен ), Начало очередного сеанса распределения памяти определяется сигналом

"Сброс", который устанавливает в нулевое состояние триггеры 8.

Сигналы низкого уровня с выходов элементов ИЛИ 9 через элементы 11 задержки (элемент задержки обеспечивает задержку на один такт ) поступают на соответствующие входы всех, кроме первьп., элементов И 3 и 16, запрещая формирование на их выходах сигналов высокого уровня .

Таким образом, с приходом тактового сигнала, сопровождающего адрес, принимаемый в регистр 2 сигнал высокого уровня может быть сформирован только на выходе эле!

О

55 мента И 3, соединенного;с переключателем 1 отключения первого блока, если данный переключатель находится в единичном состоянии (блок включен), Этот сигнал высокого уровня поступает на входы всех элементов

И 7 первой строки матрицы (7 -7 ).

11 1п црес обращения к памяти с регистра 2 поступает на вход дешифратора адреса 6, на j-ом выходе которого

r (соответствующем номеру блока, указанному в составе адреса ) формируется сигнал высокого уровня. Сигнал высокого уровня с 1-го выхода дешифратора 6 поступает иа входы всех элементов И 7 j-ro столбца. На первом входе элемента И 7 ) присутствует сигнал высокого уровня, поступающий с выхода первого элемента И 3, на втором входе — сигнал высокого уровня, поступающий с 1-го выхода дешифратора 6, а на остальных входах — сигналы высокого уровня, поступающие с инверсных выходов соответствующих триггеров 8, определяющих занятость блока памяти.

Таким образом, только на выходе элемента И 7 в данном такте присут11 ствует сигнал высокого уровня. Сигнал высокого уровня с выхода элемента И 71 поступает на прямой

1j вход триггера 8 и переводит его в

1j единичное состояние, что соответствует занятости первого блока памяти. Этот же сигнал поступает на > -й вход элемента ИЛИ 9, с выхода которого сигнал передается в адресную систему первого блока, разрешая его возбуждение. Сигнал низкого уров.ня с инверсного выхода триггера 8 . поступает на соответствующие входй

1j всех, кроме 11-ro» элементов И 7 первой строки и 1-го столбца, запрещая адресу с 1-ым блоком обращаться куда-либо, кроме первого блока памяти, а также адресам с другими номерами блоков обращаться к первому блоку памяти. Сигнал высокого уровня с выхода элеме .та ИЛИ 9„ поступает на вход элемента 11 задержки, а с, его выхода в следующем такте поступает на входы вторых элементов

И 3 и 16, разрешая тем самым формирование сигнала высокого уровня на выходе второго элемента И 3, если второй блок памяти не отключен.

Во втором такте сигналы высокого уровня формируются на выходах пер198565 4 . адресов к первому блоку памяти.

Сигнал низкого уровня с первого переключателя 1 ноступает на вход первого элемента НЕ 10. Сигнал высо5 кого уровня с выхода первого элемента НЕ 10 поступает на вход элемента И 16„ При поступлении тактового сигнала на вход элемента И 162 на его выходе присутствует сигнал

® высокого уровня, который поступает на вход элемента И 1-22 и элемента

И 142 . Если второй блок памяти включен, то на выходе элемента И 12 присутствует сигнал высокого уровня, который поступает на вход элемента ИЛИ 132, а с его выхода— на входы всех элементов И 7 второй строки. Если и второй блок оказывается отключенным, то сигнал низкого уровня с переключателя 1 поступает на вход второго элемента

НЕ 10, Сигнал высокого уровня с выхода второго элемента НЕ 10 поступает на вход элемента И 142 . Сигнал

25 высокого уровня с выхода элемента

И 14> поступает на вход элемента

ИЛИ 15» с выхода которого сигнал высокого уровкя поступает на входы элементов И 12> и 145. Таким об30 разом, обеспечивается обход отключенных блоков памяти. Первому из поступивших в регистр 2 адресов предоставляется первый из неотключенных и незанятых блоков памяти, и это соответствие жестко фиксируЗ5 ется соответствующим триггером 8.

45

50 заняты.

3,1 вого и второго элементов И 3. Сигнал высокого уровня с выхода второго элемента И 3 поступает на вход элемента ИЛИ 132, а с его выхода - на . входы всех элементов И 7 второй строки. Если и во втором такте в регистр 2 поступает адрес с прежним номером блока, то совпадение сигналов высокого уровня на всех входах происходит только на элементе И 7„ и возбуждается вновь первый

11 блок памяти. Так происходит до тех пор, пока в регистр 2 не поступит адрес, содержащий другой номер блока (допустим и-й ), В этом случае сигнал высокого уровня формируется на и-ом выходе дешифратора 6. Сигнал высокого уровня с и-ro выхода де" шифратора 6 поступает на входы всех элементов И 7 и-го столбца. На всех входах элемента И 7 происходит сов2 падение сигналов высокого уровня.

Сигнал высокого уровня с выхода элемента И 7 „ поступает на прямой вход триггера 82„ и переводит его в единичное состояние. Далее этот сигнал поступает Hà и-й вход элемента

ИЛИ 9, а с его выхода передается в адресную систему второго блока памяти. Сигнал низкого уровня с инверсного выхода триггера 8 поступа2п ет на соответствующие входы всех, кроме 2п-го, элементов И 7 второй строки и n-ro столбца, запрещая адресу с и-ым блоком обращаться кудалибо, кроме второго блока памяти, а также адресам с другими номерами блоков обращаться к второму блоку памяти. Сигнал высокого уровня с выхода элемента ИЛИ 92 поступает на вход элемента II> задержки, а с его выхода в следующем такте поступает на входы третьих элементов И 3 и 16 разрешая тем самым формирование сигнала высокого уровня на выходе третьего элемента И 3, если третий блок памяти не отключен, и так далее.

Если первый блок памяти оказывается отключенным, то сигнал низкого уровня с выхода первого элемента

И 3 поступает на первые входы всех элементов И 7 первой строки и тем самым запрещает обращение любого из

Если -й блок памяти отключен в процессе работы, то сразу оказывается невозможным наличие сигнала высокого уровня на выходе элемента

ИЛИ 13;. Сигнал низкого уровня с выхода элемента ИЛИ 13., поступая на входы всех элементов И 7,, запрещает обращение к -му блоку памяти любому из поступающих в регистр

2 адреса.

При необходимости осуществить перераспределение памяти формируется сигнал "Сброс", означающий начало нового сеанса. Сигналом "Сброс" все триггеры 8 устанавливаются в нулевое состояние — блоки памяти не

Составитель В, Рудаков

Редактор Н,Шаыдкая Техред С.Мигунова Корректор A.Зимокосов

Заказ 7724/50 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий !

13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4