Устройство для ввода информации

Иллюстрации

Показать всеРеферат

1. УСТРОЙСТВО ДЛЯ ВВОДА :ИНФОРМАЦИИ, содержащее коммутатор, аналого-цифровой преобразователь, ;блок управления, регистр номера канала , регистр адреса и элемент ИШШ , первый вход коммутатора является первым входом устройства, первые входы элемента И-ИЛИ и регистров номера канала и адреса являются вторым входом устройства, вторые входы регистров номера канала и адреса являются третьим входом устройства, выход регистра адреса соединен с вторым входом элемента И-ИЛИ, выход которого соединен с вторым входом коммутатора , выход которого соединен с первым входом аналого-цифрового преобразователя , первый выход которого соединен с первым входом блока управления , второй является первым выходом устройства, первый выход блока управления соединен с вторым входом аналого-цифрового преобразователя, а второй выход является вторым выходом устройства, отличающееся тем, что, с целью увеличения быстродействия , в него введены блоки фиксации адреса, первый и второй дешифраторы , три группы элементов И, группа элементов задержки и три элемента И, первые входы блоков фиксации адреса соединены с выходом регистра номера канала, вторые выходы соединены с входами элементов задержки группы, третьи выходы соединены с вторыми входам , элементов И первой группы, выходы элементов задержки соединены с первыми входами элементов И первой группы, выходы которых соединены с вторыми входами блоков фиксации адреса, первый выход первого блока фиксации адреса о «б соединен с первыми входами вого и второго дешифраторов,первый и четвертый выходы последнего блока фиксации адреса соединены с вторь№Ш и первым входами первого элемента И соответственно, первые выходы промежуточных блоков фиксации адреса соединены с вторыми входами элементов И второй группы и с соответствующим входом второго дешифратора,вторые выходы соединены с вторыми входами элементов И третьей группы, а четвертые - с первыми входами элементов И второй и третьей групп, выходы элементов И второй группы соединены с соответствующими входами первого дешифратора, а выходы элементов И третьей группы соединены с четвертыми входами последующих блоков фиксации адреса, выход первого элемента И соединен с последним входом первого дешифратора , а первый выход последнего бло . ка фиксации адреса соединен с последним входом второго дешифрато

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 151) 4 G 06 F 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3753783/24-24 (22) 20.06.84 (46) 23.12.85. Бюл. N 47 (7 1) Опытно-конструкторское производство Института физиологии им.

А.А.Богомольца (72) В.В. Абросимов, Б.Ç.Грушевский и Н.И.Филякин (53) 681.14(088.8) (56) Авторское свидетельство СССР

11 798776, кл. С 06 F 3/00, 1979.

Авторское свицетельство СССР

)1 1012230, кл. С 06 F 3/00, 1983. (54)(57) 1. УСТРОЙСТВО ДЛЯ ВВОДА

ИНФОРМАЦИИ, содержащее коммутатор, аналого-цифровой преобразователь, ;блок управления, регистр номера канала, регистр адреса и элемент ИИЛИ, первый вход коммутатора является первым входом устройства, первые входы элемента И-ИЛИ и регистров номера канала и адреса являются вторым входом устройства, вторые входы регистров номера канала и адреса являются третьим входом устройства, выход регистра адреса соединен с вторым входом элемента И-ИЛИ, выход которого соединен с вторым входом коммутатора, выход которого соединен с первым входом аналого-цифрового преобразователя, первый выход которого соединен с первым входом блока управления, второй является первым выходом устройства, первый выход блока управления соединен с вторым входом аналого-цифрового преобразователя, а второй выход является вторым выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в него введены блоки фиксации адреса, первый и второй дешифраторы, три группы элементов И, группа элементов задержки и три эле. мента И, первые входыблоков фиксации адреса соединены с выходомрегистра номера канала, вторые выходы соединены с входами элементов задержки группы, третьи выходы соединены с вторыми входам . элементов И первой группы, выходы элементов задержки соединены с первыми входами элементов И первой группы, выходы которых соединены с вторыми входами блоков фиксации адреса, первый .выход первого блока фиксации адреса соединен с первыми входами первого и второго дешифраторов,первый и четвертый выходы последнего блока фиксации адреса соединены с вторыми и первым входами первого элемента

И соответственно, первые выходы промежуточных блоков фиксации адреса соединены с вторыми входами элементов И второй группы и с соответствующим входом второго дешифратора,вторые выходы соединены с вторыми входами элементов И третьей группы, а четвертые — с первыми входами элементов И второй и третьей групп, выходы элементов И второй группы соединены с соответствующими входами первого дешифратора, а выходы элементов И третьей группы соединены с четвертыми входами последующих блоков фиксации адреса, выход первого элемента И соединен с последним входом первого дешифратора, а первый выход последнего бло.ка фиксации адреса соединен с последним входом второго дешифратора, первый и второй выходы второго дешифратора соединены с вторыми входами второго и третьего элементов И соответственно, выход второго элемента И соединен с вторыми входами блоков фиксации адреса, а выход третьего элемента И соединен с третьим входом первого блока фиксации адреса, второй выход которого соединен с четвертым входом второго блока фиксации адреса, третий выход блока управления соединен с первыми входами второго и третьего элементов И.

2. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что блок управления содержит генератор, четвертый элемент И, элемент задержки, мультивибратор, выход генератора соединен с вторым входом четвертого элемента И, первый вход которого и вход мультивибратора являются

200272 первым входом блока, выход мультивибратора является вторым выходом блока, выход четвертого элемента И соединен с-входом элемента задержки и является третьим выходом блока, выход элемента задержки является первым выходом блока.

3. Устройство по п..1, о т л и— ч а ю щ е е с я тем, что каждый блок фиксации адреса содержит триггер и пятый элемент И, первый и второй входы пятого элемента И являются первым и вторым входами блока, четвертый вход блока соединен с четвертым выходом блока, .выход пятого элемента И соединен с входом сброса триггера, третий вход .блока соединен с входом установки тригге. ра и третьим выходом блока, прямой и инверсный выходы триггера являются первым и вторым выходами блока соответственно.

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сбора и обработки .аналоговой информации в реальном масштабе времени от нескольких датчиков, а также в системах комплексного обучения и тренажа.

Цель изобретения — увеличение быстродействия устройства за счет организации режима избирательного опроса, а также расширение функциональных возможностей.

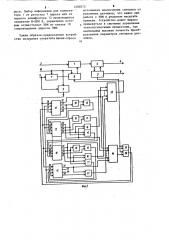

На фиг.1 представлены структурная схема устройства для ввода информации; на фиг. 2 — схема блока управления, входящего в состав устройства; на фиг. 3 — принципиальная схема блока фиксации.

Устройство содержит коммутатор 1, аналого-цифровой преобразователь (АЦП)2, каналы 3 аналогового входа устройства, выходной канал 4 цифровой информации, блок 5 управления, канал 6 сопровождения выходной информации, регистр 7 адреса, элемент

И-ИЛИ 8, регистр 9 номера канала,. канал 10 сопровождения адресов 3ВМ, цифровой вход 11 адресов ЭВМ, блоки 12 фиксации адреса, первый 13

2 и второй 14 дешифраторы, первую группу, элементов И 15, вторую группу.элементов И 16, третью группу элементов И 17, элементы 18 задерж5 ки, три элемента И 19-21. Блок 5 управления содержит генератор 22, четвертый элемент И 23, элемент 24 задержки и мультивибратор 25.

10 Каждый блок 12 фиксации адреса содержит триггер 26 и пятый элемент И 27, соединенные между собой, первый 28, второй 29, третий 30 и четвертый 31 входы, первый 32,вто15 рой 33, третий 34, четвертый 35 выходы.

Устройство работает следующим образом.

В начале цикла в регистр 9 ноЮ мера канала записывается ff -разрядный код. Порядковый номер разряда регистра соответствует номеру коммутируемого канала. Логическая .единица, записанная на любой раз25 ряд регистра, вызывает в дальнейшем коммутацию соответствующего канала. В начальный момент все триг геры 26 блоков 12 фиксации адреса находятся в нулевом состоянии, на тацня канала с учетом всех переходных процессов. Получив сигнал преобразования из АЦП 2, блок 5 управления вырабатывает новый тактовый импульс, поступающий на вторые входы первого 19 и второго 20 элементов И. Так как на входах дешифратора 14 появляются .логические "1", на инвентирующем

1О выходе дешифратора также появляется логическая единица, разрешающая прохождение тактового импульса через второй элемент И.20. Попадая далее на второй вход 29 первого блока фик15 сации, тактовый импульс сбрасывавт триггер 26 этого блока в нулевое состояние. На первом выходе 32 первого блока фиксации появляется ,логическая "1" размещающая появ2О ление "1" на первом выходе 32 второго блока фиксации. Если триггер 26 второго блока фиксации не установлен в единичное состояние, то разрешение от первого блока 12 Аиксации

25 проходит через третью группу элементов И 17 на ближайший взведенный блок фиксации, который выставляет и и

1 на первом выходе 32. Отработав один такт, этот блок дает разрешение следующему взведенному блоку.

Далее цикл повторяется.

Если триггер 26 первого блока 12 фиксации не взведен, то тактовый импульс появляется на третьем выходе 34

35 первого блока фиксации проходит чеФ рез его первую группу элементов И 15 и, проходя последовательно через блоки фиксации, сбрасывает первый ближайший триггер 26 взведенного блока, следующий тактовый импульс сбрасывает следующий взведенный блок фиксации.

После отработки всех взведенных блоков фиксации на всех входах дешифратора 14 состояния триггеров устанавливается "О, что вызывает появII lt ление 1 на неинвентирующем выходе дешифратора. Следующий тактовый импульс, пройдя через первый элемент И 19, попадает на первые входы

28 всех блоков фиксации и переписывает в триггеры 26 состояние разрядов регистра 9 номера канала, затем цикл повторяется.

Этот импульс синхронизирует пере- пись выходной информации АЦП 2 в ,приемное устройство. При этом на 4о

:второй вход элемента И 23 блока управления поступает сигнал от генератора 22 тактовых импульсов. При совпадении сигнала окончания преоб- . разования АЦП 2 и тактового импуль- 45 са генератора 22 на выходе элемента

И 23 появляется импульс управления, поступающий на вход первого 19 и второго 20 элементов И и вход элемента 24 задержки блока 5 управления .50

С выхода элемента 24 задержки импульс управления поступает на вход АЦП 2 и дает разрешение на очередное преобразование сигнала АЦП 2. Величина задержки выбрана таким об- 55 разом, что к моменту . появления задержанного импульса управления заканчивается очередная коммуJ 1 втором выходе 29 первого и последнего блоков фиксации и на третьем входе 30 второго и третьего блоков фиксации — логический "0", при этом на неинвентирующем выходе первого дешифратора 13 состояния триггеров появляется логическая "1". Тактовый импульс от блока 5 управления, проходя через первый элемент И 19, переписывает в триггеры 26 блоков фиксации состояние соответствующих разрядов регистра 9 номера канала.

При этом триггеры коммутируемых каналов принимают единичное значение.

На первом входе 28 блока фиксации, соответствующем младшему из .коммутируемых каналов, появляется логическая "1", поступающая на вход первого дешифратора 13, который на выходе вырабатывает код, соответствущщий номеру коммутируемого канала. Данный код поступает на вход коммутатора 1, который производит коммутацию соответствующего канала.

После этого из блока 5 управления поступает сигнал начала преобразования на АЦП 2, происходит аналогоцифровое преобразование. После окончания преобразования АЦП 2 выдает сигнал окончания преобразования, который поступает на блок 5 управления на первый вход элемента И 23 и вход ждущего мультивибратора 25.Последний вырабатывает импульс сопровождения, поступающий в канал 6 сопровождения выходной информации.

В устройстве предусмотрена возможность непосредственной адресации от ЭВМ в коммутатор 1. При этом про1изводится запись адреса коммутируемого канала от ЭВМ в регистр 7 алТаким образом, предлагаемое устройство позволяет сократить время опроса

5 реса. Выбор информации для коммутатора 1 от регистра 7 адреса или от первого дешифратора 13 производится элементом И-ИЛИ 8, управление кото. рым осуществляет ЭВМ по каналу 10 сопровождения адресов ЭВМ.

1200272 4 источников аналогичных сигналов от различных датчиков, что важно при работе с ЭВМ в реальном масштабе времени. Устройство может широко применяться в системах управления технологическими процессами, где необходима высокая точность преобразования параметров сигналов дат.чиков

1200272

ФигЗ

Составитель В.Абросимов

Техред M.Ãåðãåëü

Корректор Л.Патай

Редактор С.Саенко

Тираж 709

ВНИИПИ Государственного, комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 7868/54

Подписное

Филиал ППП "Патент", г.ужгород, ул. Проектная, 4