Арифметическое устройство

Иллюстрации

Показать всеРеферат

АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, содержащее два сумматора-вычитателя, квадратор, сдвиговый регистр, причем первый и второй информационные входы устройства соединены соответственно с первым и вторым информационными входами первого сумматоравычитателя , выход которого соединен с входом квадратора,выход которого . соединен с первым входом второго сумматора-вычитателя , а выход сдвигового регистра является выходом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит коммутатор, распределитель импульсов, триггер, элемент задержки , три элемента И, три элемента ИЛИ, два элемента НЕ, причем выходы первого и второго сумматорО з-вычитателей соединены с соответствующими ин- , формационными входами коммутатора, выход которого соединен с информационным входом сдвигового регистра, выход которого соединен с вторым входом второго сумматора-вычитате-- , С(щ:г 13 - . ,; .ля, вход пуска устройства соединен с входом распределителя импульсов, первый выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с входом элемента задержки и входом записи сдвигового регистра, второй выход распределителя 11мпульсов соединен с вторым входом первого элемента ИЛИ и с первым входом первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, третий выход распределителя импульсов соединен с первым входом второго 8 элемента И, выход которого соединен с входом сдвига сдвигового регистра, (Л первый разряд входа кода операции устройства соединен с вторыми входами первого и второго элементов И, с первыми входами третьих элементов И и ИЛИ и через первый элемент НЕ с управляющим входом коммутатора, второй разряд входа кода операции устройства соединен с вторым входом третьего элемента ИЛИ и входом второго элемента НЕ, выходы которых соединены соответственно с единичHbw и нулевым входами триггера, выход которого соединен с управляющими входами первого и второго сумматороввычитателей , вход элемента задержки соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом триггера.

COIO3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (!9) (11)

m!4 С 06 F 7/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3777304/24-24 (22) 30.07.84 (46) 23.12.85. Бюл. ¹ 47 (72) К.M.Ñàãäååâ, H.È.×åðâÿêoâ и

Н.И.Швецов (53) 681.3(088,8) (56) Авторское свидетельство СССР № 1100619, кл. G 06 F 7/49, 1982.

ТИИЭР, 1980, т.б8, № 4, с.114

116, рис, 3. (54)(57) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО, содержащее два сумматора-вычитателя, квадратор, сдвиговый регистр, причем первый и второй информационные входы устройства соединены соответственно с первым и вторым информационными входами первого сумматоравычитателя, выход которого соединен с входом квадратора,выход которого соединен с первым входом второго сумматора-нычитателя, а выход сдвигов ого регистра является выходом устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит коммутатор, распределитель импульсов, триггер, элемент задержки, три элемента И, трн элемента ИЛИ, два элемента НЕ, причем выходы первого и второго сумматоров-вычитателей соединены с соответствующими информационными входами коммутатора, выход которого соединен с информационным входом сднигового регистра, выход которого соединен с вторым входом второго сумматора-вычитате.ля, вход пуска устройства соединен с входом распределителя импульсов, перный выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены соответственно с входом элемента задержки и входом записи сднигового регистра, второй выход распределителя импульсов соединен с вторым входом первого элемента

ИЛИ и с первым входом первого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ, третий выход распределителя импульсов соединен с первым входом второго элемента И, ныход которого соединен с входом сдвига сдвигового регистра, первый разряд входа кода операции устройства соединен с вторыми входами первого и второго элементов И, с первыми входами третьих элементов

И и ИЛИ и через первый элемент НЕ с управляющим входом коммутатора, второй разряд входа кода операции устройства соединен с вторым входом третьего элемента ИЛИ и входом второго элемента НЕ, выходы которых соединены соответственно с единичным и нулевым входами триггера, ныход которого соединен с управляющими входами первого и второго сумматороввычитателей, вход элемента задержки соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом триггера.

1200278

45

Изобретение относится .к вычислительной технике и может быть использовано для построения арифметических устройств ВЦМ.

Цель изобретения — сокращение количества оборудования.

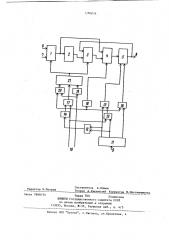

На чертеже представлена структурная схема арифметического устройства.

Арифметическое) устройство содержит сумматор-вычитатель 1, квадратор 2, сумматор-вычитатель 3, коммутатор 4, сдвиговый регистр 5, информационные входы 6 и 7, выход 8, вход 9 пуска, вход 10 кода операции, распределитель

11 импульсов, элемент ИЛИ 12, элемент

И 13, элемент 14 задержки, элемент

ИЛИ 15, элемент И 16 и 17, элемент

НЕ 18 и 19, элемент ИЛИ 20, триггер 21.

Устройство работает следующим образом.

Арифметическое устройство выполняет операции сложения, вычитания и умножения при кодах на входе 10 кода операции, соответственно "01", . "ОО" и "11".

При операции сложения сумматорывычитатели 1 и 3 установлены в режим суммирования кодом входа 10 через элемент ИЛИ 20 и единичный вход триггера 21. Коммутатор 4 обеспечивает передачу данных на выход с первого сумматора-вычитателя 1, так как на его управляющий вход поступает единица с входа 10 через элемент НЕ

18. Операнды, поступающие на входы 6 и 7 суммируются в. сумматоре-вычитателе 1 и через коммутатор 4 сумма записывается в первом такте в сдвиговый регистр 5, на вход записи которого поступает первый тактовый импульс с первого выхода распределения

11 импульсов через элемент ИЛИ 15, результат поступает на выход 8 устройства .

При выполнении операции вычитания устройство работает аналогично за исключением того, что сумматорывычитатели устанавливаются в режим вычитания кодомвхода 10через элемент

НЕ 19и нулевой вход триггера 21.

Прн операции умножения произведение вычисляется по формуле (а Ъ)—

-(О-Ь) /4, Исходное состояние аналогично рассмотренным ранее. С поступлением импульса по входу 9 на выходах распределителя 11 импульсов последовательно по времени появляются тактовые импульсы. Первый тактовый импульс проходит через элемент ИЛИ 15 и поступает на вход управления записи сдвигового регистра 5, а также проходит через элемент ИЛИ 12, элемент

14 задержки и элемент И 17, поскольку на втором входе элемента И 17 будет присутствовать потенциал логической единицы с выхода 10. Данный сигнал с выхода элемента И 17 поступает на счетный вход триггера 21 и переводит его в противоположное нулевое состояние.

Таким образом, первоначально сумматоры-вычитатели работают в режиме слежения. Полученная сумма. (а+Ь) через квадратор 2, сумматорвычитатель 3 и коммутатор 4 поступает на сдвиговый регистр 5, где записывается промежуточный результат (а+Ь) . После чего, так как триггер

21 приведен в нулевое состояние, сумматор-вычитатель 1 формирует значение (а-Ь), которое проходит через квадратор 2 на вход сумматора-вычитателя 3, где вычитается иэ величины, записанной в сдвиговом регистре 5, и по второму тактовому импульсу, поступающему через элемент ИЛИ 15 на вход записи сдвигового регистра 5 результат (а+Ь) (а-Ь) записывается в данный регистр. Второй тактовый импульс также переводит сумматоры-вычитатели

1 и 3 в режим сложения, пройдя по цепи: элемент ИЛИ 12, элемент 14 задержки, элемент И 17 и счетный вход триггера 21.

По третьему тактовому импульсу, поступающему с третьего выхода распределителя 11 импульсов через эле- . мент И 16 на вход сдвига сдвигового регистра 5, производится сдвиг на два разряда вправо значения, записанного в сдвиговам регистре 5, что соответствует делению на четыре, и полученное произведение поступает на выход 8 устройства.

Редактор В.Петраш

Заказ 7868/54

Составитель А.Клюев

Техред А.Кикемезей Корректор М.Максимишинец

Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

t13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4