Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК р 1 G 06 F 9/22

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21 ) 3754528/24-24 (22) 13.06.84 (46) 23.12.85. Бюл, Р 47 (72) В.А.Торгашев, А.Б.Кириллов, А.В.Мыскин, А.П.Чугунов и В.И.Шкиртиль (53) 681,32(088.8 ) (56) Авторское свидетельство СССР

У 746517., кл. G 06 F 9/16, 19?7.

Авторское свидетельство СССР, Ф 842815, кл. 6 06 F 9/22, 1979. (54)(57 ) МИКРОПРОГРАММНОЕ УСТРОЙСТВО

УПРАВЛЕНИЯ, содержащее блок памяти, регистр иикрокоманд, мультиплексор.. условий, дешифратор, счетчик адре- са, выход которого соединен с адресныи входои блока памяти, выход кото« рого подключен к информационному входу регистра микроко" манд, синхровход которого соединен с входом первого тактового им. пульса устройства, а выход - с выходом устройства, информационный вход мультиплексора условий соединен с входом условий устройства, синхровход счетчика адреса соединен с входои второго тактового импульса устройства, выход кода формата команды регистра микрокоманд соединен с входои дешифратора, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, оно содержит регистр

„„SU„„1200289 A

; расширения микрокоманди, сумматор и элемент И, причем первый и второй информационные входы регистра расширения микрокоманды соединены соответственно с выходом кода признака перехода регистра иикрокоманд и информационным входом устройства, выходы кода адреса перехода, кода условий и кода вида перехода регистра расширения микрокоманды подключены соответственно к первому информационному входу сумматора, управляю- . щему входу мультиплексора условий и управляющему входу сумматора, второй информационный вход которого подключен к выходу счетчика адреса, вход счета записи которого соединен с выходом элемента И, первый, второй и третий входы которого соединены со- С ответственно с выходом мультиплекФ сора условий, первым выходом дешифратора и выходом кода признака перехода регистра иикрокоманд, выход сумматора подключен к информационному входу счетчика адреса, второй выход дешифратора подключен к входу paspeшения записи регистра расширения иикрокоманды, синхровход и вход направ» ления записи которого соединены соответственно с третьим тактовйм входом устройства и выходом кода признака перехода регистра микрокоианд.

3 12

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных системах.

Цель изобретения — повышение быстродействия устройства микропрограммного управления.

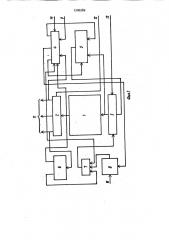

На фиг.l представлена функциональная схема устройства микропрограммного управления„ на фиг.2 — алгоритм работы устройства; на фиг. 3 - тактовые импульсы, поступающие на синхровходы блоков устройства.

Устройство содержит блок 1 памяти, регистр 2 микрокоманд, счетчик 3 адреса, регистр 4 расширения микрокоманды, сумматор 5, дешифратор 6, элемент И 7, мультиплексор

8 условий, информационный вход 9, вход 10 условий, информационный выход

1l, входы 12-14 тактовых импульсов.

На фиг.3 обозначены период Т тактовых импульсов или цикл работы устройства, тактовые импульсы 15, поступающие на вход 12 устройства, тактовые импульсы 16, поступающие на вход 13 устройства, тактовые импульсы 17, поступающие на вход 14 устройства.

Устройство предназначено для работы с типовым набором микрокоманд.

Пусть например, микрокоманда содержит 16 разрядов, которые нумеруются. с 0-го по 15-й начиная с младшего.

Старшие 2 разряда, 15 и 14-й, определяют формат микрокоманды, причем код 00, содержащийся в данных разрядах, определяет 1-й формат, код 01

2-й формат, код 10 - 3-й формат, код 11 - 4-й формат.-Положим, что формат 1 соответствует,арифметическим, формат 2 - логическим операциям, формат 3 - операциям загрузки регистра расширения микрокоманды, формат 4 - операциям пересылок, Пусть в 3-м формате разряды микрокоманды распределены следующим образом: 15-14 - формат микрокоманды, 13 — направление загрузки регистра расширения микрокоманды; 12 - вид

L перехода (относительный, абсолютный ), 11-9 - вид условия перехода (по переполнению, концу работы блока ввода-вывода и т.д.); 8-0 - адрес А (либо абсолютный адрес перехода, либо приращение к текущему значению счетчика 3 адреса ).

Пусть в первом формате совмеще ны операция перехода и арифметичес00289 1

I5

40 кая, т.е. например 13-й разряд микрокоманды указывает на наличие перехода, а остальные определяют арифметическую операцию. Логично для увеличения эффективности системы микрокоманд подобное совмещение реализовать и в микрокомандах тех форма тов, в которых есть по крайней мере один свободный разряд, что повлечет изменение схемы дешифратора 6.

Первый выход регистра 2 микрокоманд, подключенный к первому информационному входу регистра 4 расширения микрокоманды, соответствует (:!2О)-м разрядам микрокоманды, второй вь.ход, подключенный к первому управляющему входу регистра 4 и к третьему входу элемента И 7, — 13-му разряду микрокоманды и в 3-м формате оп. ределяет загрузку регистра 4 либо с регистра 2, либо с информационного входа 9 устройства, а в первом формате определяет наличие перехода, третий выход, подключенный к входу дешифратора 6, - (15-14)-м разрядам микрокоманды и определяет ее формат.

В регистр 4 расширения микрокоманды загружается признак перехода: вид перехода, вид условия перехода и адрес А, т.е. разряды (12-0) регистра 2 микрокоманд, Первый выход регистра 4 подключен к первому информационному входу сумматора 5 и 1 представляет код либо приращения относительного адреса перехода, либо абсолютного адреса перехода, второй выход подключен к управляющему входу селектора 8 и представляет код вида условия перехода, третий выход под= ключен к управляющему входу сумматора 5 и представляет код вида перехода (абсолютный или относитель-. ный ).

На сумматоре 5 получается либо относительный адрес перехода суммированием базового адреса, поступающего ю I с второго информационного входа,подключенного к выходу счетчика 3 адреса, и приращения адреса, поступающего по первому. информационному входу, либо абсолютный, .поступающий по первому информационному входу.

Счетчик 3 адреса, в зависимости от значения сигнала на управляющем входе "Счет/запись", подкдоченном к выходу элемента И 7, работает либо в режиме счета, либо в режиме занесения адреса перехода с информацион« 3 I ного входа, подключенного к выходу сумматора 5.

Первый выход дешифратора 6, подключенный к второму входу элемента И 7, соответствует первому формату микрокоманды перехода, второй выход, подключенный к второму управляющему входу регистра 4, соответству» ет третьему формату микрокоманды и определяет разрешение загрузки . регистра 4.

Устройство работает следующим образом.

С приходом. тактового сигнала на вход 12 устройства из блока I памяти микрокоманд в регистр 2 заносится микрокоманда загрузки регистра 4 и в соответствии со значением кода первог управляющего входа регистра 4 ои загружается, с приходом тактового сигнала на вход 14 устройства, либо непосредственно с регистра 2, либо с информационного входа 9 устройства, при этом на второй управляющий вход регистра 4 поступает сигнал разрешения записи с второго выхода дешифратора.6.

После загрузки регистра 4 начинается выполнение цикла . микрокоманды цикла, начиная с первой, выбираются последовательно из блока 1 памяти до появления команды перехода, при этом на втором выходе дешифратора 6 отсут. ствует сигнал, разрешающий запись в регистр 4, а на входе "Счет/запись" счетчика Э адреса действует сигнал, поступающий с выхода элемента И 7

200289 4 и обуславлнвающий режим счета, так как на второй вход элемента И 7 с первого выхода дешифратора 6 сигнал не поступает. Счетчик 3 увеличивает свое содержимое на единицу с прикорм каждого тактового импульса на вход

13 устройства.

С появлением на .регистре 2 микрокоманды перехода.на втором выходе

10 регистра 2 и первом выходе дешифратора 6 появляются сигналы, поступающие соответственно на третий и второй входы элементы И 7. Если к этому моменту пришел сигнал условия

15 перехода на вход 10 устройства, то .на выходе мультиплексора 8 появляется сигнал условия перехода, опредео ляемый кодом сигнала вида условия перехода, поступающего с второго вы2О хода регистра 4, На выходе элемента И 7 появляется сигнал, обеспечивающий занесение в счетчик 3 адре са с выхода сумматора 5 кода адреса первой мнкрокоманды цикла, и про25 цесс повторяется до окончания цикла.

С окончанием цикла условие перехода не вырабатывается, сигнал условия перехода отсутствует на входе 10

ЗО устройства, и с появлением микрокоманды перехода на регистре 2 на выходе мультиплексора 8 и, следовательно, на выходе элемента И 7 сигнал от» сутствует, счетчик 3 адреса остается в режиме счета и из блока 1 памяти выбирается микрокоманда, следующая за командой перехода.

12002S9

1200289 из длока 1аибюти ю регистр Г

Регистр 0

Суммаиюр Х иота Ю фАЩ

1200289

Составитель. А.Чугунов

Редактор В.Петраш Техред Т.Дубинчак Корректор Г.Решетник

Заказ 7869/55 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, М-35, Рввюскяя вяя., д. 4/5

Филиал ППП "Патент", r.Óæãîðîä, ул.Проектная,4