Многостабильный элемент памяти

Иллюстрации

Показать всеРеферат

МНОГОСТАБИПЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ, содержащий первый и-р-п-транзистор , коллектор которого соединен с базой первогор -п-р-транзистора, а база первого л-f-П-транзистора соединена с коллектором первого р -п-ртранзистора , второй -р-Я-транзистор, коллектор которого соединен с базой второгор -п-р-транзистора, а база второго П -р-п-транзистора соединена с коллектором второго р -П-р-транзистора , адресные и разрядную шины, отличающийся тем, что, с целью снижения потреблйемой мощности, и упрощения элемента памяти, змиттер первого п-р-

, СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (1!) yg y б 11 С 11/40

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ЬО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ. 1 иФ;:.;., :, . 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг.7. К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ (21) 3652379/24-24 (22) 11. 10.83 (46) 23.12.85. Бюл. g 47, (71) Московский ордена Трудового

Красного Знамени инженерно-физический институт (72) А.С. Березин, С.А. Королев и Е.М. Онищенко

:,(53) 681.327.66(088.8)

;(56) Авторское свидетельство СССР

)f 767839, кл. С 11 С 11/40, 1978.

Авторское свидетельство СССР

В 366497, кл. 6 11 С 11/34, 1973. (54)(57) МНОГОСТАБИЛЬНЫЙ ЭЛЕМЕНТ

ПАМЯТИ, содержащий первый л -р-л-транзистор, коллектор которого соединен с базой первого р -n-p-транзистора, а база первого ff â€,р-fl-транзистора соединена с коллектором первого p -ff""pтранзистора, второй л -p-л-транзистор, коллектор которого соединен с базой. второго р -0-р-транзистора, а база второго л †.p-0-транзистора соедине- . на с коллектором второго Р --f)-Р-тран-. зистора, адресные и разрядную шины, отличающийся тем, что, с целью снижения потребляемой мощности, и упрощения элемента памяти, эмиттер первого и -p-Л-транзистора соединен с эмиттером второго.р -и-Р-транзистора и с первой адресной. шиной, коллектор первого ff--p-0-транзистора соединен с коллектором второго П -P-ffтранзйстора и.с разрядной шиной, эмиттер первого р-П-Р-.òðàíýèñòoðà . Е соединен с базой второго fl--p-ff-тран- g зистора, эмиттер которого подключей к второй адресной шине, С:

200340

С, „

С Вч С4 8) экВ С2 С э2

1 1

Изобретение относится к.вычислительной технике, а точнее к элементам памяти, и наиболее эффективно может быть использовано при создании ин-. тегральных оперативных запоминающих устройств большой емкости.

Целью изобретения является снижение потребляемой мощности и упрощение элемента памяти.

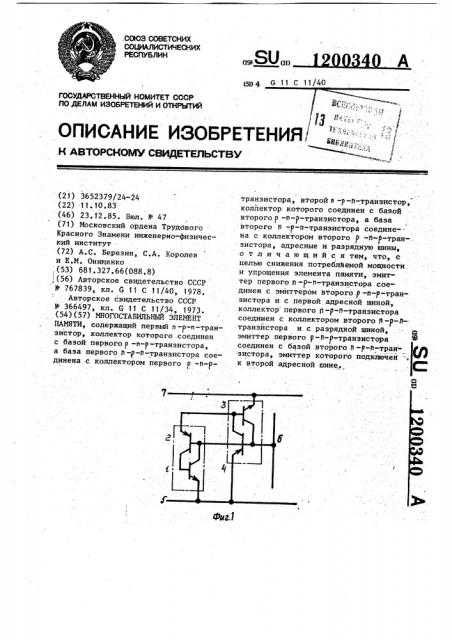

На фиг. 1 изображена схема предI лагаемого элемента памяти; нй фиг.2— временные диаграммы его работы.

Иногостабильный элемент памяти содержит первый n -p-n-транзистор 1, коллектор которого соединен с базой первого р -Р-р-транзистора 2, а база первого 11 р -11-транзистора 1 соединена с коллектором первого р --пр-. транзистора 2, второй 11-р-11-транзистор 3, коллектор которого соединен с базой .второго n - -n-транзистора 4, а база второго и -P-и-транзистора 3 соединена с коллектором второго р-п-р-транзистора 4, эмиттер первого и -Р-и-транзистора 1 соединенс эмиттером второго p --n-p-транзистора 4 и с первой адресной шиной 5, коллектор первого р -p-n-транзистора 1 сое.динен с коллектором второго и -p-итранэистора 3 и с разрядной шиной 6, эмиттер первого ) -и- Р-транзистора 2 соединен с базой второго n -p-n-транзистора 3, эмиттер которого подклю.чен к второй адресной шине 7.

Первые и -р -0- и ) --n-р-транзисто4 ры 1 и 2 образуют первую инжекционную структуру, а вторые n -p- h- u

p-n-p-транзисторы 3 и 4 образуют вторую инжекционную структуру.

Ю

Состояние элемента памяти можно различать следуюппим образом: наличие заряда на барьерной емкости С центрального перехода первой инжекционной структуры и на барьерной емкости С второй инжекционной структуры. соответствует состоянияю "0", С разряжена, С заряжена — соответствует состоянию "1", обе емкости

С и С разряжены — состояние "2".

В режиме хранения на всех шинах 5 поддерживается одинаковый потенциал,,следовательно, ток через элемент памяти не течет, и мощность не потребляется. Для записи "2" потенциал шины разрядной 6 снижается на, где (J - напряжение на открытом

Р-В-переходе. При этом эмиттер вто ,рого и -и-р-транзистора 4 инжектирует дырки в базу второго и -p n-транзистора 3, повьппая ее потенциал и разряжая тем самым барьерную емкость С

Так как база второго n --p-n-транзисто- ра 3 соединена с эмиттером первого

p-n-p-транзистора 4, его потенциал также будет повышаться.до тех пор, пока не превысит на U потенциала

Ф разрядной шины 6. При этом начнется инжекция дырок из эмиттера первого

$-n-Р-транзистора 2 в базу первого и-р-п-транзистора 1, разряжая барьерную емкость С< . После того как обе емкости разрядятся, потенциал разрядной шины 6 восстанавливается до прежнего уровня. Для записи "1" сначала производятся запись "2", а затем на вторую адресную шину 7 подается отрицательный импульс амплитудой 0 . При этом емкость С заряжается до напряжения 0 . По окончании импульса заряд с емкости C частично перераспределится на емкость C эмиттерного перехода второго Р --n-р-транзистора 3. В результате записи "1" емкость С, окажется разряженной, а ем-. кость С заряженной. Для записи "0" отрицательные импульсы амплитудой 0 подаются на обе адресные шины 5 и 7, При этом обе емкости C v C заряжаются. Считывание информации осуществляется с помощью операции записи "О".

При поступлении по адресным шинам 5 и 7 отрицательного импульса амплитудой U. в разрядной шине 6 возника- ет импульс тока, который и фиксируется внешними схемами. При считывании

"1" происходит заряд емкости С, базовым током первого 11-p-n-транзистора

1 и заряд суммарной емкости p --п —переходов второго и --р-п-транзистора 3, т.е. заряжается эквивалентная емкость где б, — коэффициент усиления тока базы первого n -p-и-транзистора 1.

При считывании "2" заряжается экви» валентная емкость, э В Сз 1 81)+("+ 8 ) 1 где 8 — коэффициент усиления тока базы второго n --p-n-транзистора 3.

При считывании "0" заряжается эквивалентная емкость

1200340

С,Сэ, CzCez

С + у

sr.so C,iC„Ñz Ñ„

АШ2

Фиг.2

Составитель С, Королев

Техред Л.Иикешт

Корректор С. Шекмар, Редактор Т. Кугрышева

Тираж 583

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, ?москва, Ж-35, Раушская наб., д. 4/5 И

Подписное

Заказ 801

Филиал IIIIII "Патент", r. Ужгород, ул. Проектная, 4 где С, — барьерная емкость эмиттерного перехода n-)-п-транзистора 1.

В зависимости от величины эквивалентной емкости различаются и амплитуды импульсов тока, поступающих в разрядную шину 5. Регенерация.осуществляется последовательным вйполнейием операций считывание-запись.