Высоковольтный логический элемент

Иллюстрации

Показать всеРеферат

ВЫСОКОВОЛЬТНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ, содержа Щ1Й входную логическую схему, шина питания которой соединена с первой шиной питания элемента , входы - с входами элемента, а выход подключен к базе фазорасщепляющего транзистора первого типа проводимости, коллектор которого соединен с базой первого транзистора первого типа проводимости и через резистор с первой шиной питания элемента , эмиттер первого транзистора через два последовательно включенных диода смещения поключен к базе второго транзистора первого типа проводимости , которая через токозадакмций резистор соединена с общей шиной,, эмиттер второго транзистора соединен с общей шиной, а коллектор подключен к базе первого транзистора, коллектор которого соединен с базой третьего транзистора второго типа проводимости и через резистор с второй шиной питания элемента, эмиттер третьего транзистора соединен с второй шиной питания элемента, а коллектор подклю-чен к базе первого составного транзистора сложного инвертора, коллектор которого подключен к второй шине питания элемента, эмиттер - к выходу элемента и через развязывающий диод к коллектору третьего транзистора и коллектору второго составного транзистора сложного инвертора, эмиттер которого соединен с общей шиной, а база подключена к эмиттеру фазорасщепляющего транзистора, отличающийся тем, что, с целью повышения быстродействия логического элемента, в него введен четвертый транзистор первого типа проводимости, база которого через первый дополнительный резистор соединена с его эмиртером и общей шиной и через второй дополнительный резистор с эмиттером фазорасщепляющего транзистора, а коллектор - с базой второго транзистора.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 Н 03 К 19/00

ОПИСАНИЕ ИЗОБРЕТ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАЬ ИЭОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3717272/24-21 (22) 29,03.84 (46) 23.12.85. Бюл. К 47 (72) Б, А, Гарбуз, С. А. Коновалов и В. И. Громов (53) 621.374(088.8) (56) Авторское свидетельство СССР

11 8644571, кл, Н 03 К 19/00, 1979.

Микросхема К1109KН4, схема электрическая принципиальная 1ОФЗ

3.438.008.ЭЗ. (54)(57) ВЫСОКОВОЛЬтНЬУ Л0ГИЧКСКИй

ЭЛЕМЕНТ, содержащий входную логическую схему, шина питания которой соединена с первой шиной питания элемента, входы - с входами элемента, а выход подключен к базе фазорас- щепляющего транзистора первого типа проводимости, коллектор которого соединен с базой первого транзистора первого типа проводимости и через резистор с первой шиной питания элемента, эмиттер первого транзистора через два последовательно включенных диода смещения поключен к базе второго транзистора первого типа проводимости, которая через токазадающий резистор соединена с общей шиной, эмиттер второго транзистора соединен с общей шиной, а коллектор подключен к базе первого транзистора, коллектор которого соединен с базой третьего транзистора второго типа проводимости и через резистор с второй шиной питания элемента, эмиттер третьего транзистора соединен с второй шиной питания элемента, а коллектор подключен к базе первого составного транзистора сложного инвертора, коллектор которого подключен к второй шине питания элемента, эмиттер — к выходу элемента и через развязывающий диод к коллектору третьего транзистора и коллектору второго составного транзистора сложного инвертора, эмиттер которого соединен с общей шиной, а база подключена к эмиттеру фазорасщепляющего транзистора, о т л и— ч а ю шийся тем, что, с целью повышения быстродействия логического элемента, в него введен четвертый транзистор первого типа проводимости, база которого через первый дополнительный резистор соединена с его эмит тером и общей шиной и через второй дополнительный резистор с эмиттером фазорасщепляющего транзистора, а коллектор — с базой второго транзистора.

1200412

Из обре тени е отно сит ся к импуль сной технике, в частности к высоко- вольтным логическим элементам для управления газоразрядными индикаторными панелями переменного и постоянного тока.

Цель изобретения — повышение быст родействия путем увеличения базовых токов выходных" транзисторов во время переходного.проце ба.

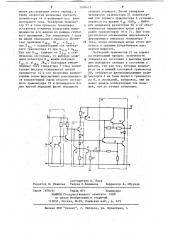

На чертеже приведена принципиальная электрическая схема предлагаемого логического iýëåìåíòà, Высоковольтный логический элемент содержит входную логическую схему 1, шина питания которой соединена с первой шиной 2 питания, входы — с входами 3 элемента, а выход подключен к базе фазорасщепляющего транзистора

4 первого типа проводимости, коллектор которого через резистор 5 соединен с первой шиной 2 питания и с базой первого транзистора 6 первого типа проводимости генератора 7 тока, эмиттер первого транзистора 6 через два последовательно включенных диода

8 и .9 смещения соединены с базой второго транзистора 10 генератора 7 тока и через токозадающий резистор 11 с общей шиной, эмиттер второго транзистора 10 соединен с общей шиной, а коллектор - с базой первого транзистора 6, коллектор которого через резистор 12 соединен с второй шиной

13 питания элемента и базой третьего транзистора 14 второго типа проводимо сти, эмиттер которого соединен с второй шиной 13 питания, а коллектор - c базой первого составного транзистора 15 сложного инвертора 16, коллектор которого соединен с второй шиной 13 питания, а эмиттер - с выходом 17 элемента и через раэвязывающий диод 18 — с коллектором второго составного транзистора 19, эми1 тер которого соединен с общей шиной, а база - с эмиттером фазорасщепляющего транзистора 4 и через первый дополнительный резистор 20 с базой четвертого транзистора 21 первого типа проводимости, эмиттер которого соединен с общей шиной и через второй дополнительный резистор 22 с его базой, а коллектор подключен к базе второго транзистора 10.

Логический элемент работает следующим образом, 5

Время переходного процесса переключения элемента из состояния с низким уровнем в состояние с высоким уровнем выходного сигнала зависит от времени выключения второго составного транзистора 19, работающего в режиме глубокого насьпцення, а это

55,время определяет ся количе ством накопленного заряда в базе второгО нижнего составного транзистора 19, вреВ статическом состоянии, когда на все входы 3 входной логической схемы 1 подан высокий уровень напряжения, на ее выходе — высокий уровень напряжения и, следовательно, открыты и насыщены фазорасщепляющий транзистор 4, нижний второй составной транзистор 19 и четвертый транзистор 21.

Ток, протекающий по резистору 5, перехватывается из базы первого транзистора 6 в коллектор фазорасщепляющего транзистора 4, на котором устанавливается уровень напряжения

U 4 = 2U + U 1,6-1,8 В, меньшии отпирающего потенциала базы первого транзистора 6, равного U +

+ 2 П см = 1ь9 2 ° 1 В, Первый транзистор 6 и последовательно включенные третий транзистор

14 и первый составной транзистор 15 закрыты. На выходе элемента 17— низкий уровень выходного сигнала

Пкэм 9 + П щ = 1»6 1ь8 В. В этом состоянии отсутствует потребление оч высоковольтной второй шины 13 питания.

Когда на один или несколько входов 3 входной логической схемы 1 по-, дан низкий уровень напряжения, то в статическом режиме фазорасщепляющий транзистор 4 и последовательно соединенные с ним второй составной транзистор 19 и четвертый транзистор

21 заперты, На базе первого транзис- тора 6 устанавливается потенциал

Б пп + 2 U „+ Бз8ц,, и генератор 7 тока обеспечивает в базу третьего транзистора 14 стабилизированный ток, равный U,, jR «, уровень которого выбирается из условий насыщения третьего транзистора 14 и минимума потребляемой и рассеиваемой мощности. На выходе элемента сформирован высокий уровень напряжения (Е-

2 0 - U „, ), где Š— напряжение на второй шине питания.

1200412

Составитель А. Янов

Редактор В. Иванова Техред О.Ващишина Корректор А. Обручар

Заказ 7878/61 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, -35 Раушская наб., д, 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 менем рассасывания этого заряда, а также скоростью включения третьего транзистора 14 и величиной его коллекторного тока, Четвертый транзистор 21 в этом процессе продолжает .5 оставаться открытым вследствие инерционности его выхода из режима глубо-. кого насыщения, Ток генератора 7 тока на время переходного процесса достигает величины U g, /Rи,+ Х„, 1О о где „ — коллекторный ток четверk2q того тра зистора 21 при и1э2! = ЦБэ10

Так как Л, зависит от Х „в статическом состоянии, то выбором номиНапа pesHcTopa R можно rroayuHzr 15 Х„, » U >> >/К„, Благодаря увеличенному току генератора 7 тока значительно быстрее открывается третий транзистор 14 и его возросшим коллек» торным током форсировано рассасывает- 20 ся коллекторный заряд второго состав :ного транзистора 19 и формируется бо лее крутой передний фронт выходного сигнала элемента. После запирания четвертого транзистора 21 коллекторный ток первого транзистора 6 устанавливается на уровне U 10/R«, Выбором номиналов резисторов 20 и 22 обес- печивается одинаковое время запирания транзисторов 19 и 21. При этом достигается оптимальная длительность форсирующего импульса генератора 7 тока, когда минимален вклад этого импульса в среднюю потребляемую элементом мощность.

Четвертый транзистор:21 не влияет на переxoдный процесс .логического элемента из состояния с высоким уровнем выходного сигнала в состояние с низким, так как ток, которым включается он и нижний составной транзистор

19, отбирается фазорасщепляющим тран-. зистором 4 из базы первого транзистора 6, и последний, запираясь, уже не может выдать коллекторный ток больший, чем до начала запирания,