Цифроаналоговый преобразователь

Иллюстрации

Показать всеРеферат

I . ЦИФРОАНАЛОГОВЬБТ ПРЕОБРАЗОВАТЕЛЬ , содержащий блок управления , первые выходы которого подключены к первым входам первого блока развертки кода, а второй выход к первому входу регистра, и преобразователь код-аналог, выход которогр является выходной шиной цифроаналогового преобразователя,о т л и ч а ю - с; и и с я тем,что,с целью повышения точности ,в него введены блок элементов И, постоянное запоминающее устройство, блок определения знака кода, второй . блок развертки кода, первые входы которого подключены к третьим выходам блока управления, вторые входы объединены с соответствуюгщми первыми входами блока управления, соответствующими вторыми входами первого : блока развертки кода и подключены к соответствующим выходам блока элементов И, первые входы которого объединены с соответствующими третьими входами второго блока развертки кода и подключены к соответствующим выходам первого блока развертки кода. третьи входы которого являются входными шинами цифроаналогового преобразователя , четверты - входы объединены с соответствзпощими вторыми входами блока элементов И, соответ ствуюшими входами блока определения знака кода и подключены к соответствующим выходам второго блока развертки кода, четвертые входы которого подключены к соответствующим выходам постоянного запоминающего устройства , вход которого подключен к четвертому выходу блока управления, второй вход которого объединен с вторым входом регистра и подключен к § выходу блока определения знака кода, третий вход является шиной Запуск, СО при этом выходы регистра подключены к соответствующим входам преобразова-. теля код-аналог. 2. Преобразователь по п.1, о т .личающийся тем, что блок управления выполненна первом и втором счетчиках, .первом и втором регистрах , генераторе тактовых импульсов , постоянном запоминающем устройстве , первый вход.которого подключен к выходу первого счетчика, входы с второго по

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 4 А (51) 4 Н 03 М 1/66 (21) 3706544/24-24 (22) 04,01 Я4 (46) 23,12,85, Бюл. Ф 47 (72) А.П. Стахов, А.Д, Азаров, В.Я. Стейскал и В.В. Лысюк (53) 681.325(088.8), (56) Авторское свидетельство СССР .

Р 947955, кл. Н 03 К !3/02, 1982

Авторское свидетельство СССР

Р 864548, кл. Н 03 К 13/02, 1979; (54)(57) 1. ЦИФРОАНАЛОГОВЬП1 ПРЕОБРАЗОВАТЕЛЬ, содержащий блок управления, первые выходы которого подключены к первым входам первого блока развертки кода, а второй выход— к первому входу регистра, и преобразователь код-аналог, выход которого является выходной шиной цифроаналогового преобразователя,о т л и ч а юшийся тем,что, с целью. повышения точности,в него введены блок элементов И, постоянное запоминающее устройство, блок определения знака кода, второй блок развертки кода, первые входы которого подключены к третьим выходам блока управления, вторые входы объединены с соответствуюг1ими первыми входами блока управления, соотI ветствующими вторыми входами первого блока развертки кода и подключены к соответствующим выходам блока элементов И, первые входы которого объединены с соответствующими третьими входами второго блока развертки кода и подключены к соответствующим выходам первого блока развертки кода, третьи входы которого являются входными шинами цифроаналогового преобразователя, четвертые входы объединены с соответствующими вторыми входами блока элементов И, соответствующими входами блока определения знака кода и подключены к соответствующим выходам второго блока развертки кода, четвертые входы которого подключены к соответствующим выходам постоянного запоминающего устройства, вход которого подключен к четвертому выходу блока управления, второй вход которого объединен с вторым входом регистра и подключен к выходу блока определения знака кода, третий вход является шиной "Запуск", при этом выходы регистра подключены к соответствующим входам преобразова-. теля код-аналог.

2. Преобразователь по п,l, о тл и ч а ю шийся тем, что блок управления выполнен на первом и втором счетчиках,,первом и втором регистрах, генераторе тактовых импульсов, постоянном запоминающем устрой-. ! стве, первый вход которого подключен: к выходу первого счетчика, входы с второго по ())+1)-й, где )) — число разрядов преобразуемого кода, являются первыми входами блока управления, (n+2)-й вход подключен к выходу второго счетчика, ())+3)-й вход является вторым входом блока управления, входы с ())+4)-го по ()1+8)-й подключены к соответствующим выходам первого регистра, выходы с первого по двенадцатый подключены к соответствующим информационным входам второго регистра, выходы с три1200422 надцатого по семнадцатый подключены к соответствующим информационным входам первого регистра, первый управляющий вход которого является третьим входом блока управления, второй управляющий вход подключен к инверсному выходу генератора тактовых импульсов, прямой выход которого подключен,,к" :управляющему входу втоФ. рого регистра, вЫходы с первого по третий которого являются первыми выходамй блока управления, выходы с

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования цифровых величин в аналоговые.

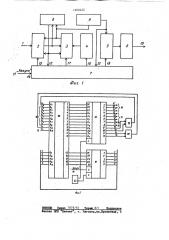

Цель изобретения — повьппение точности цифроаналогового преобразователя, На фиг.l приведена структурная схема цифроаналогового преобразователя; на фиг.2 - функциональная схема блока управления.

Цифроаналоговый преобразователь содержит входные шины 1, первый блок 2 развертки кода, второй блок 3 развертки кода, постоянное запоминающее устройство 4, регистр 5, преобразователь 6 код-аналог, блок 7 управления, блок 8 элементов И, блок

9 определения знака кода, выходную шину 10, шину ll "Запуск". Блок 7 управления имеет первые, второй и третий входы. 12 — 14 и первые, второй, третьи и четвертый выходы 15—

18. Блок 7 управления (фиг.2) выполнен на первом и втором счетчиках 19 и 20, первом и втором регистрах 21 и 22, генераторе 23 тактовых импуль сов, постоянном запоминающем устройстве 24. Блок 9 определения знака кода может быть выполнен на элементе

ИЛИ, имеющем входов, где II --число разрядов преобразуемого када.

Преобразователь 6 код-аналог должен быть выполнен на основе избыточного измерительного кода. В этом случае наличие в определенных пределах отчетвертого по шестой являются третьими выходами блока управления, седь- мой выход является четвертым выходом блока управления, восьмой выход является вторым выходом блока управления, девятый и десятый выходы подключены соответственно к первому и второму входам первого счетчика, а одиннадцатый и двенадцатый выходы подключены соответственно к первому и второму входам второго счетчика.

1 клонений весов разрядов от требуемых значений не приведет к разрывам.выходной характеристики. К избыточным измерительным кодам относятся P-коды

5 Фибоначчи, коды "золотой" пропорции, коды Люка, Котса и т.д, На окончательном этапе изготовления цифроаналогового преобразователя в постоянное запоминающее устройство записываются коды измеренных значений реальных весов разрядов преобразователя 6 код-аналог.

Работа цифроаналогового преобразователя происходит в режиме преобраIS зования входного избыточного кода, например кода Фибоначчи, в аналоговый эквивалент. Причем, вначале вход ной код К преобразуется в рабочий код К, представляющий код реальных

20 значений весов разрядов преобразователя 6 код-аналог. После формирования К з этот код с выхода регистра 5 поступает на вход преобразователя 6 . код"аналог, в результате чего на выходе 10 устройства появляется анало Tовая величина, соответствующая входному коду К. Преобразование кода К в код K при помощи блоков 2 — 9 осуР ществляется следующим образом.

На первом такте входной код К, i.íoñòóïàþùèé на вход 1 по сигналу блока 7 управления, записывается в первый блок 2 развертки кода, который

35 . функционирует в данном случае как ре- гистр. Во второй блок 3 развертки кода переписывается кодовый эквивалент Н я 1 реального значения веса

1200422 (n-1)-ro (старшего) разряда, хранящийся в постоянном запоминающем устройстве 4, Над содержимым блоков 2 и 3 развертки кодов выполняются операции вычитания. В формировании разности кодовых комбинаций участвуют первый блок 2 развертки кода, второй блок 3 развертки кода, блок 8 элементов И и блок 7 управления, Выполнение операции вычитания производится путем развертки кодовых комбинаций в первом блоке 2 развертки кода и во втором блоке 3 развертки кода и установки в нулевое состояние совпадающих значащих разрядов кода, причем установка в нулевое состояние совпадающих разрядов производится после полной развертки кода,, Указанный процесс происходит до появления нулевой кодовой комбинации хотя бы в одном из блоков развертки кода. Признаком появления нулевой кодовой комбинации является отсутствие сигналов совпадения значащих разрядов кода, поступающих с выхода блока 8 элементов И. Опреде-. ление знака кода разности произво-. дится анализом состояния второго блока,3 развертки кода блоком 9 определения знака кода, причем выходной сигнал Х; блока 9 равен нулю, если содержимое блока 3 нулевое, и 1; равен единице, если содержимое блока 3 ненулевое. . При. этом1 если на первом такте после выполйения операции вычитание

1;=О, то это свидетельствует о том, что код 11д 1 меньше входного кода

К. При этом (n-I)-й разряд кода Кр, формируемого в регистре 5, установится в единичное состояние, à в блоке 2 развертки кодов будет находиться код равный разности кодов (К вЂ” Nq, ), Причем, на следующем такте сравнение кода !!>., вызываемого из постоянного запоминающего устройства 4, будет происходить с кодом (К вЂ” N „ ). Если Y =!, то это свидетельствует о том, что код М д-1 больше кода К. При этом (n-!)-й разряд кода К установится в нулевое состояние, а во втором блоке 3 развертки кодов будет находиться код, равный разности кодов (N „, — К). А так как в этом случае дальнейшее

5 сравнение кода N „ 2 должно проис ходить с входным кодом К, необходимо восстановить значение. кода К в.первом блоке 2 развертки кода.

Для этого код (N, — К) перепи-!

0 сывается в блок 2. При этом в блок 3 вторично записывается код 1 из постоянного запоминающего устройства

4. В результате проведения операции вычитания над содержимым этих блоков в блоке 3 развертки кода сформируется входной код К, который переписывается в блок 2

На втором такте по сигналу с блока 7 управления из постоянного запоминающего устройства 4 во второй блок 3 развертки кода записывается кодовый эквивалент N реального

n-z значения (n-2)-ro разряда. Над содержимым этих блоков производится операция вычитания. При этом, если

Y = О, то (n-2)-й разряд кода К установится в единичное состоянйе, а если Y = 1, то (п-2)-й разряд кода К установится в нулевое состояние и в блоке 2 будет восстановлен

30 код, находящийся в этом блоке до выполнения операции вычитания.

Работа устройства на любом 1 -м такте происходит аналогично. В регистре 5 формируется 1 -й разряд ко35 да К, в первом блоке 2 развертки кода формируется код, зависящий от входного кода К и выходных сигналов

У, полученных в 1 -м и предыдущих тактах, 40

Формирование кода К р заканчивается на и -м такте, При этом в регистре 5 находится код реальных значений весов разрядов или рабочий код Кр.

45 После формирования рабочего кода

К р и поступления его на вход преобразователя 6 код-аналог на выходе

10 устройства появится аналоговая величина, значение которой соответствует входному коду К

На этом цифроаналоговое преобразование входного кода заканчивается, )200422

ЗНИИПИ Заказ 7878/61 Ти ж 871 йо свое

Фидиал GDO Патеат, г. Уагород,ул.Проекткаа, 4