Преобразователь биимпульсного двоичного сигнала в бинарный сигнал

Иллюстрации

Показать всеРеферат

I. ПРЕОБРАЗОВАТЕЛЬ БИИМПУЛЬСНОГО ДВОИЧНОГО СИГНАЛА В БИНАРНЫЙ СИГНАЛ, содержащий триггер, . формирователь импульсов запрета, первый детектор .перехода, состоящий из соединенных последовательно первого и второго элементов задержки и инвертора , выход которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к выходу первого . элемента задержки,и второй детектор перехода, состоящий из соединенных последовательно первого инвертора, элемента задержки и второго инвертора , выход которого подключен к первому входу элемента И-НЕ, второй вход которого подключен к выходу первого инвертора, причем вход первого элемента задержки первого детектора перехода объединен с входом первого инвертора второго детектора перехода и соединен с входом преобразователя , выходы элементов И-НЕ первого и второго детекторов перехода соединены с соответствующими входами формирователя импульсов запрета, а выход триггера является выходом преобразователя , отличающийся тем, что, с целью повышения быстродействия , в него введены элемент И-НЕ и элемент задержки, вход которого соединен с входом преобразователя, а выход - с информационным входом триггера, тактовый вход которого соединен с выходом элемента И-НЕ, первый и второй входы которого сое (Л динены соответственно с выходами элементов И-НЕ первого и второго детекторов перехода, а выход формирователя импульсов запрета соединен с третьими входами элементов И-НЕ первого и второго детекторов перехода. 2. Преобразователь по п. 1, о т - личающийся тем, что формиfo рователь импульсов запрета содержит о последовательно соединенные элемент И-НЕ, элемент задержки и инвертор, 4 о выход которого соединен с выходом формирователя импульсов запрета, 3 первый и второй входы которого соединены соответственно с первым и вторым входами элемента И-НЕ.

СОЮЗ СОВЕТСНИХ .

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (50 4 Н 03 M 5/12

ОПИСАНИЕ ИЗОБРЕТЕ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

° ф

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3659867/24-24 (22) 27.09.83 (46) 23.12.85. Бюл. 9 47 (72) В.А. Обоев, В.И. Журба, Т.Б. Карашев, А.П. Мищенко и В.А. Якимов (53) 621.374.373(088.8) (56) Патент США 1(- 4307381, кл. С 06 F 5/04, 22.12.81.

Патент США У 3979746, кл. 340/347 ДД, 07.09.76. (54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ БЩЩПУЛЬСНОГО ДВОИЧНОГО СИГНАЛА В БИНАРНЫИ СИГНАЛ, содержащий триггер, формирователь импульсов запрета, первый детектор перехода, состоящий из соединенных последовательно первого и второго элементов задержки и инвертора, выход которого соединен с первым входом элемента И-НЕ, второй вход которого подключен к выходу первого . элемента задержки,и второй детектор перехода, состоящий из соединенных последовательно первого инвертора, элемента задержки и второго инвертора, выход которого подключен к первому входу элемента И-НЕ, второй вход которого подключен к выходу первого инвертора, причем вход первого элемента задержки первого детектора перехода обьединен с входом первого инвертора второго детектора перехода и соединен с входом преобразователя, выходы элементов И-НЕ первого и второго детекторов перехода соединены с соответствующими входами формирователя импульсов запрета, а выход триггера является выходом преобразователя, отличающийся тем, что, с целью повышения быстродействия, в него введены элемент И-НЕ и элемент задержки, вход которого соединен с входом преобразователя, а выход — с информационным входом триггера, тактовый вход которого соединен с выходом элемента И-НЕ,, первый и второй .входы которого соединены соответственно с выходами элементов И-НЕ первого и второго детекторов перехода, а выход формирователя импульсов запрета соединен с третьими входами элементов И-НЕ первого и второго детекторов перехода.

2. Преобразователь по и. I о т л и ч а ю шийся тем, что формирователь импульсов запрета содержит последовательно соединенные элемент

И-НЕ, элемент задержки и инвертор, выход которого соединен с выходом формирователя импульсов запрета, первый и второй входы которого соединены соответственно с первым и вторым входами элемента И-НЕ.

1200426

Изобретение относится к автоматике и вычислительной технике и предназначено для преобразования сигналов в устройствах высокоскоростных цифровых линий связи, в частности в волоконно-оптических ли.НИЯХ СВЯЗИ, Целью изобретения является повышение быстродействия.

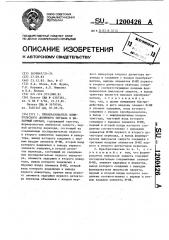

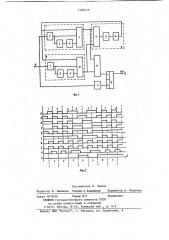

На фиг. 1 представлена блок-схема преобразователя бинмпульсного .двоичного сигнала в.бинарный сигнал; на фиг. 2 — временная диаграмма работы устройства.

Устройство содержит первый детектор 1 перехода, состоящий из перво- го элемента 2 задержки, второго элемента 3 задержки, инвертора 4 и элемента И-НЕ 5, второй детектор 6 перехода, состоящий иэ первого инвертора 7, элемента 8 задержки, второго инвертора 9 и элемента И-НЕ 10; формирователь 11 импульсов запрета,. состоящий из элемента И-НЕ 12, элемента задержки и: инвертора 14, элемент И-.НЕ 15, элемент 16 задержки, триггер 17, вход 18 и выход 1 9 ..

Принцип действия устройства основан на свойстве биимпульсного (манчестерского) сигнала, которое заключается в том, что каждый временной интервал, соответствующий одному биту передаваемой информации, делится на две равные части, одна из которых имеет значение логической единицы, а другая — значение логического нуля, Изменение сигнала в середине разрядного временного интервала происходит всегда, независимо от значения передаваемых сигналов, что позволяет выделить из сигнала импульсы тактовой частоты. Это положение иллюстрируется сигналами, сформированными на выходах элемента 1 задержки и инвертора 7 (фиг. 2а и 23)

Входной сигнал через элемент 2 задержки, служащий для компенсации задержки сигнала в инверторе 7, поступает на первый вход элемента .

И-НЕ 5 и через элемент 3 задержки и инвертор 4 — на его второй вход.

Сигнал на выходе инвертора 4 представлен на фиг. 2 6 . В этом слу:чае, если сигнал на третьем входе

5 элемента И-НЕ 5 соответствует логической единице, при изменении Входного сигнала от "0" к "1" на его выходе формируется импульс логического нуля, длительность которого равна времени задержки элемента 3 (фиг. 2 ) . Время задержки элемента

3 выбирается равным половине разрядного времени интервала, Детектор

6 перехода работает аналогично и формирует импульс логического нуля при переходе входного сигнала от "1" к "0 (фиг. 2е). На фиг. 2 представлен сигнал, сформированный на выходе инвертора 9.

Импульсы с выходов элементов 5 и 10 поступают на входы формирова. теля 11 импульсов запрета, а также инвертируются элементом И-НЕ 15 и поступают на тактовый вход триггера

l7. На выходе формирователя 11 формируются импульсы логического нуля (фиг. 2Ф), по длительности равные выходным импульсам детекторов 1 и 6

30 перехода, задержанные на половину разрядного временного интервала.

Они запирают элементы И-HE 5 и 10 по третьим входам, запрещая прохож дение импульсов, воэникающих от изменения входного сигнала на краях разрядных временных интервалов.

Таким образом, на тактовый вход триггера 17 проходят только импульсы, возникающие в середине разрядных

40 интервалов (фиг. 2ф). Информационный вход триггера 17 соединен с входом преобразователя через элемент 13 задержки, который обеспечивает необходимое фазовое положе45 ние между сигналами на тактовом и информационном входах триггера (фиг. 2k) .

Таким образом, длительность тактовых импульсов на входе триггера преобразователя увеличивается до длительности импульсов сигнала (фиг. 2л) .

1 200426

ФЬг.l

1 i 1

Заказ 7878/61 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035., Москва, Н-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель Б. Ходов

Редактор В. Иванова Техред О.Ващишина Корректор А. Обручар