Устройство цифрового декодирования информации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ЦИФРОВОГО ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ, содержащее . семь D-триггеров, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ШТИ-НЕ, причем D-Бходы первого и второго D-триггеров объединены, D-вход третьего D-триггера подключен к первому входу устройства, С-входы первого и четвертого D-триггеров объединены и подключены к второму входу устройства , С-входы второго и третьего D-триггеров подключены соответственно к третьему и четвертому входам устройства, прямой выход первого D-триггера соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к D-входу пятого D-триггера, прямой выход второго. D-триггёра соединен с вторым входом первого и первым входом второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход третьего D-триггера соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсный выход четвертого D-триггера подключен к первому входу элемента ИПИ-НЕ, отличающееся тем, что, с целью повьпиения помехоустойчивохгти за счет сужения полосы энергетического спектра сигнала, в него введены восьмой D--тpиггep, третий элемент ИСКЛОЧАЮЩЕЕ ИЛИ, три элемента ИЛИ и элемент И, выход которого соединен с S-входом шестого D-триггера, а входы соединены с выходом элемента Ш1И-НЕ и инверсными выходами пятого и седьмого D-триггеров, D-вход гаестого D-триггера подключен к дополнительному выходу элемента ШШ-НЕ, второй вход которого соединен с прямым вькодом восьмого D-триггера, D-вход которого подключен к выходу первого элеS мента ИЛИ, первый и второй входы СП которого соединены с выходами соответственно первого и третьего элементов ИСКЛЮЧАКНЦЕЕ ИЛИ, входы третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к прямьм выходам соответственно первого и третьего D-триггеров , D-входы которых объединены, R-вход восьмого)-триггера -объединен с первым входом второго элемента ИЛИ и С-входом четвертого D-триггера , R-вход которого объединен с С-входами пятого и восьмого D-триггеров и вторым входом второго элемента ИЛИ и подключен к пятому входу устройства, выход второго элемента ИЛИ соединен с С-входами шестого и седьмого D-триггеров, прямой выход шестого .D-триггера подключен к D-входу седьмого D-триггера и первому входу третьего элемента ИЛИ, второй вход которого соединен с инверсным выходом пятого D-триггера, а выход является выходом устройства.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (11) (5D 4 M 03 М 5/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3693226/24-24 (22) 13..01.84 (46) 23.12..85. .Бюл. .У 47 (72) M.È. Беляков, В.Д. Лиференко, И.А. Лукин, Ю. В. Марков и В. Т.Хрыкин (53) 681. 32 (088. 8) (56) Авторское свидетельство СССР

Ф 855997, кл. Н 03 К 13/24, 19.11.79

Заявка .Великобритании

II - 1578635, кл. Н 03 К 13/00, 19.03.76 (54) (57) УСТРОЙСТВО ЦИФРОВОГО ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ, содержащее семь 0-триггеров, два элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент ИЛИ-НЕ, . причем D-входы первого и второго

D-триггеров объединены, D-вход третьего D-триггера подключен к первому входу устройства, С-входы первого и четвертого D-триггеров объединены и подключены к второму входу устройства, С-входы второго и третьего

D-триггеров подключены соответственно к третьему и четвертому входам устройства, прямой выход первого

D-триггера соединен с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к 0-входу пятого D-триггера, прямой выход второго D-триггера соединен с вторым входом первого и первым входом второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, прямой выход третьего D-триггера соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, инверс" ный выход четвертого D-триггера подключен к первому входу элемента

ИЛИ-НЕ, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости за счет сужения полосы энергетического спектра сигнала, в него введены восьмой 0=триггер, третий элемент ИСКЛIОЧАЮЩЕЕ ИЛИ, три элемента ИЛИ и элемент И, выход которого соединен с S-входом шесто—

ro D-триггера, а входы соединены с выходом элемента ИЛИ-НЕ и инверсными выходами пятого и седьмого

D-триггеров, D-вход шестого D-триггера подключен к дополнительному выходу элемента ИЛИ-НЕ, второй вход которого соединен с прямым выходом восьмого О-триггера, D-вход которого подключен к выходу первого элемента ИЛИ, первый и второй входы которого соединены с выходами соответственно первого и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к прямым выходам соответственно первого и третьего D-тригге— ров, D-входы которых объединены, R-вход восьмогоЮ -триггера объединен с первым входом второго элемента ИЛИ и С-входом четвертого D-триггера, к-вход которого объединен с

С-входами пятого и восьмого D-триггеров и вторым входом второго элемента ИЛИ и подключен к пятому входу устройства, выход второго элемента

ИЛИ соединен с С-входами шестого и седьмого D-триггеров, прямой выход шестого .0-триггера подключен к

D-входу седьмого D-триггера и первому входу третьего элемента ИЛИ, второй вход которого соединен с инверсным выходом пятого D-триггера, а выход является выходом устройства.

l2

Изобретение относится к автоматике и может быть использовано в сис- темах цифровой связи.

Цель изобретения — повышение помехоустойчивости за счет сужения полосы энергетического спектра сигнала.

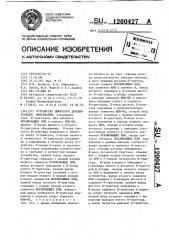

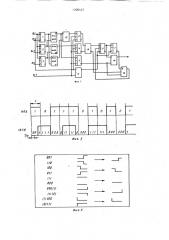

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 — пример преобразования числа из кода NRK (беэ возврата к нулю в код 1ВЗВ; на фиг. 3 и 4 принцип формирования кода 1ВЗВ; на фиг. 5 †. временные диаграммы, иллрстрирующие работу устройства.

Устройство цифрового декодирования информации содержит восемь

D-триггеров 1-8, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9-11, три элемента ИЛИ

12-14, элемент ИЛИ-НЕ 15 и элемент И 16. D-входы первого, второго и третьего D-триггеров 1-3 объединены и подключены к первому входу устройства, а их прямые выходы соединены с первыми входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ 9-11, второй вход каждого из которых объединен с первым входом следующего. Выходы первого и третьего элементов 9 и 1 1 подключены к входам первого элемента ИЛИ 12, а выход второго элемента 10 соединен с D-входом четвертого D-триггера 4, инверсный выход которого подключен к первому входу элемента ИЛИ-НЕ 15.

Выход первого элемента ИСКЛОЧАЮЩЕЕ

ИЛИ 9 подключен также к В-входу пятого D-триггера 5, инверсный выход которого соединен с первым входом элемента И 16, выход которого подключен к $-входу шестого В-триггера 6, прямой выход которого соединен с D-входом седьмого D-триггера

7, инверсный выход которого подключен к второму входу элемента И 16„ третий вход которого соединен с выходом элемента ИПИ-НЕ 15, дополнйтельный выход которого подключен к

D-входу шестого D-триггера 6. Второй вход элемента 15 соединен с прямым выходом восьмого D-триггера 8, 9-вход которого соединен с выходом первого элемента ИЛИ 12, à R-вход объединен с С-входами первого и четвертого

D-триггеров 1 и 4 и первым входом второго элемента ИЛИ 13 и подключен к второму входу устройства. С-входы второго и .третьего D-триггеров 2 и 3 соединены соответственно с третьим

00427 2 и четвертым входами устройства.

Р-вход четвертого D-триггера 4, С-входы пятого и восьмого D-триггеров

5 и 8 и второй вход второго элемента ИЛИ 13 объединены и подключены к пятому входу устройства. Выход элемента 13 соединен с С-входами шестого и седьмого D-триггеров 6 и 7;

Инверсный выход пятого и прямой вы10 ход шестого D-триггеров 5 и 6 подключены соответственно к первому и второму входам третьего элемента

ИЛИ 14, выход которого является выходом устройства. l5 При реализации устройства использован новый цифровой сигнал. Он строится по принципу, аналогичному принципу построения кода Миллера, и заключается в следующем:

20 1. Применяется:блочный сигнал вида nBmB (при коде Миллера n=l

m=2, в новом сигнале n=l m=3)

2. Блоки из m посылок, принадлежащие соседним информационным посыл-, 25 кам, пристыковываются таким образом, чтобы образовать сигнал с не менее, чем (ш+1) посылок одного уровня.

3. Посылки сигнала 1ВЗВ следуют

30 с. интервалами, кратными двум.

Пример записи числа в коде IB38 приведен на фиг. 2.

Для пояснения принципа кодирования изобразим блоки из m посылок эпюрами, причем инверсные блоки бу3$ дем изображать одной эпюрой фиг. 3) .

Обозначение вида 000(1) указывает, что после блока из трех нулей на границе с соседней информационной

40 посылкой имеется переход от одного уровня к противоположному. Тогда допустимые переходы между соседними информационными посылками, отмечен- ные стрелками и отражающие указанные

45 выше ограничения при кодировании, графически выглядят следующим образом (фиг, 4) .

Чтобы цифровой сигнал был -"прозрачен" для передаваемой информации, 1 необходимо от каждого блока иметь два перехода (на фиг. 4 обозначены стрелками), реализующие переходы от информационной посылки "1" к информационной посылке "0" и "1", а

55 также от "0" к "0" и "1". Используя переходы, отмеченные сплошными стрелками, получаем сигнал "непрозрачный" для передаваемой информации, 12004

1О

20 я

30

40 так как возможен только один переход от блока I> в первом варианте (фиг. 4q) и от блока II во втором варианте (фиг. 43) . Чтобы оригинал стал прозрачным", недостающий переход восполняется неиспользованHbIM переходом (участвует пунктирная стрелка), т,е. при кодировании для недостающего ранее перехода используется переход Т? - Т (для первого варианта) и переход I II (для второго варианта). Получаемый новый цифровой сигнал в коде 1ВЗВ обладает более узким энергетическим спектром, чем другие цифровые сигналы той же полярности и на той же скорости передачи.

Устройство цифрового декодирования информации работает следующим образом.

На первый вход устройства подаетс информационный цифровой сигнал в коде 1ВЗВ, подлежащий преобразованию (А). На второй вход устройства подается сигнал тактовой частоты (В)., На третий вход устройства подается сигнал (С) тактовой частоты, сдвинутый относительно сигнала (В) на 2 н/3. На четвертый вход устройства подается сигнал (9) тактовой частоты, сдвинутый относительно сигнала (В) на 4 n/3. На пятый вход устройства подается сигнал (Е) тактовой частоты, сдвинутый относительно сигнала (В) на я .

Информационный цифровой сигнал поступает на D-входы первого, второго и третьего D-триггеров 1-3, на

С-входы которых поступают сигналы тактовой частоты, сдвинутые друг относительно друга на 1/3 периода .

После преобразования получаются сигналы (Р), (G), (Н), которые попарно складываются на трех элементах ИСКЛЮЧАЮЩЕЕ ИЛИ 9-11. В результате получаются сигналы (I), (д), (К). Сигнал (Ь), получаемый пу27 а тем сложения сигналов (Т) и (К) на первом элементе ИЛИ 12, поступает на вход восьмого 1-триггера 8.

На его С-вход поступает тактовый сигнал,F) à íà R-вход .этого

D-триггера поступает тактовый сигнал (В). Сигнал (J) с выхода второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 поступает на D- âõîä четвертого D-триггера 4, а на С-вход и R-вход этого триггера поступают сигналы тактовой частоты соответственно (В) и (Е)

На D-вход пятого D-триггера 5 поступает сигнал (1) с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 9, а на

его С-вход — тактовый сигнал (Е) .

После преобразования на выходах восьмого, четвертого и пятого

D-триггеров 8, 4, 5 получаем сигналы (M), (N), (О) соответственно.

Сигнал (q), поступающий на С-входы шестого и седьмого D-триггеров 6 и

7, которые осуществляют сдвиг сигнала (P), образуется путем сложения на втором элементе ИЛИ 13 двух тактовых сигналов (В) и (Е). Сигнал (Р) образуется на дополнительном прямом выходе элемента ИЛИ-НЕ 15 путем сложения сигналов (М) и (N), поступающих с выходов восьмого и четвертого D-триггеров 8 и 4 соответственно. D-триггеры 6 и 7 охвачены обратной связью, образуемой с помощью элемента И 16, на входы которого поступают сигналы: (О) — с выхода пятого D-триггера 5, сигнал, обратный сигналу (Р) — с выхода (инверсного) элемента ИЛИ-НЕ 15 и сигнал (S) с инверсного выхода седьмого D-триггера 7. Полученный на выходе элемента И 16 сигнал (Т) поступает на -вход шестого D-триггера 6. Выходной сигнал (U) в виде кода NRZ получается путем сложения на третьем элементе ИЛИ 14 сигнала (R) с выхода .

5 шестого 7-триггера 6 и сигнала (0) с выхода пятогоU -триггера 5.

1200427

1200427

r1r >r iрir rrir1у > r p tpiy

4 I

Рий 5

Составитель О. Ревинский

Редактор В. Иванова Техред 0. Вашишина Корректор А. Тяско

Заказ 7878/б1. Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4