Преобразователь кода из системы остаточных классов в позиционный код

Иллюстрации

Показать всеРеферат

ПРЕОБРАЗОВАТЕЛЬ КОДА ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИ- . ЦИОННЬЙ код, содержащий генератор тактовых импульсов, четыре элемента И, три триггера, три модульных счетчика , сумматор, блок элементов И, блок элементов запрета и элемент ИЛИ, причем выход генератора татстовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триг- . гера, единичный вход которого соединен с единичными входами второго и третьего триггеров и входом начальной установки преобразователя, выход которого соединей с выходом сумматора , выход первого элемента И соединен со счетньми входа ми первого и второго модульных счетчиков и с первым входом второго элемента И, выход которого соединен со счетным входом третьего модульного счетчика, выход обнуления которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом обнуления второго модульного счетчика и с первым входом четвертого элемента И, второй вход которого соединен с с выходом обнуления первого модульного счетчика и нулевым входом третьего триггера, нулевой выход которого соединен с входом установки коэффициента пересчета первого модульного счетчика, единичный выход третьего триггера и нулевой выход второго триггера соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выходы третьего и четвертого элементов И соединены соответственно с нулевьми входами первого и второго триггеров , выход обнуления первого модульного счетчика и единичный выход второго триггера соединены соответственно с первым и вторым управляющими входами блока элементов И, выход обнуления второго модульного счетчика и единичный выход второго триггера соединены соответственно с первым и вторым управляющими входами блока элементов запрета, входы первой и второй констант преобразователя соединены соответственно с информационными входами блока элементов И и блока элементов эапрета, выходы которых соединены соответственно с первым и вторым входами сумматора, нулевой выход второго триггера соединен с входом установки коэффициента пересчета второго модульного счетчика, отличающийся тем, что, с целью сокращения оборудования, нулевой выход второго триггера соединен с третьим входом третьего элемента И, выход обнуления первого модульного счетчика соединен с третьим входом элемента ИЛИ.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А (19) (11) (51) 4 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3750997/24-24 (22) 01,06,84 (46) 23.12.85. Бюл, В 47 (72) П.Л.Прокопьев, В.А.Иванченко, В.А.Брылев и В.Н.Торопов (53) 681.3(088.8) (56) Авторское свидетельство СССР

1(- 991410, кл. G 06 F 5/02, 1981.

Авторское свидетельство СССР

Ф 928339, кл. G 06 F 5/02, 1980. (54 )(5 7 ) ПРЕОБРАЗОВАТЕЛЬ КОДА ИЗ

СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД, содержащий генератор тактовых импульсов, четыре элемента

И, три триггера, три модульных счетчика, сумматор, блок элементов И, блок элементов запрета и элемент ИЛИ, причем выход генератора тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триг-, гера, единичный вход которого соединен с единичными входами второго и третьего триггеров и входом начальной установки преобразователя, выход которого соединен с выходом сумматора, выход первого элемента И соединен со счетными входами первого и второго модульных счетчиков и с первым входом второго элемента И, выход которого соединен со счетным входом третьего модульного счетчика, выход обнуления которого соединен с первым входом третьего элемента И, второй вход которого соединен с выходом обнуления второго модульного счетчика и с первым входом четвертого элемента И, второй вход которого соединен с с выходом обнуления первого модуль-. ного счетчика и нулевым входом третьего триггера, нулевой выход которого соединен с входом установки коэффициента пересчета первого модульного счетчика, единичный выход третьего триггера и нулевой выход второго триггера соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И, выходы третьего и четвертого элементов И соединены соответственно с нулевыми входами первого и второго триггеров, выход обнуления первого модульного счетчика и единичный выход второго триггера соединены соответственно с первым и вторым управляющими входами блока элементов И, выход обнуления второго модульного счетчика и единичный выход второго триггера соединены соответственно с первым и вторым управляющими входами блока элементов запрета, входы первой и второй констант преобразователя сое° динены соответственно с информационными входами блока элементов И и блока элементов запрета, выходы которых соединены соответственно с первым и вторым входами сумматора, нулевой выход второго триггера соединен с входом установки коэффициента пересчета второго модульного счетчика, отличающийся тем, что, с целью сокращения оборудования, ну-,. левой выход второго триггера соединен с третьим входом третьего эле- мента И, выход обнуления первого модульного счетчика соединен с третьим входом элемента ИЛИ.

1 12

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения вычислительных устройств, функционирующих, в.позиционной системе счисления и системе остаточных классов.

Целью изобретения является сокращение количества оборудования.

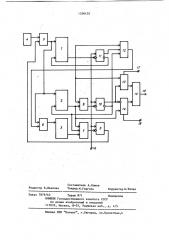

На чертеже представлена схема преобразователя кода из системы остаточных классов в позиционный код.

Преобразователь кода из системы остаточных классов в позиционный код содержит модульные счетчики 1-3, генератор 4 тактовых импульсов, элементы И 5-8, триггеры 9-11, элемент

ИЛИ !2, блок !3 элементов И, блок 14 элементов запрета, сумматор 15, вход

16 начальной установки преобразователя, входы 17 и IS первой и вто- рой констант преобразователя, выход 19 преобразователя.

Преобразователь работает следующим образом для работы преобразователя необходимо модульные счетчики 1-3 расположить. так, чтобы выполнялись следующие условия

/ но на вычитающие входы.счетчиков 1 и 2 и через элемент И 6 — на вычитающий вход модульного счетчика 3 начинают поступать импульсы, под воз-. действием которых модульные счетчи- . ки 1-3 меняют свои состояния. Модульный счетчик 1 переходит в нулевое состояние, на его выходе обнуления формируется сигнал, который опраши10 вает элемент И 8. В случае неравен.ства нулю содержимого модульных счетчиков 2 и 3 триггер 9 остается в единичном состоянии и процесс преобразования продолжается. Сигнал на выходе !

5 обнуления счетчика 1 обнуляет триггер

I! в результате чего меняется коэф фициент пересчета модульного счет чика 1 с величины m, на величину

/ш,/mod< и снимается запрет с бло 2

20 ка 13 элементов И, через .который константа m с выхода 17 поступает для суммирования на сумматор !5. При ненулевом значении содержимого счетчика 1 отсутствие сигнала с его выхо25 да обнуления запрещает через элемент ИЛИ 12 прохождение тактовых импульсов через элемент И 6, ш!> my m m /ш /шой z >

>/m, /mod 3 где m 1 — наибольший модуль.

Модульные счетчики 1-3 являются вычитающими. Сумматор 15 является накапливающим позиционным, Перед началом процесса преобразования в модульные счетчики 1-3 заносятся остатки преобразуемого числа а, à, а, по соответствующим модулям mI, m<> ш>, обРазующим основание СОК. Одновременно число а, заносится в сумматор 15. После этого сигнал "Начальная установка" по.входу 16 устанавливает в единичное состояние триггеры 9-11, в результате чего открывается элемент

И 5, закрываются блок 13 элементов.

И и блок 14 элементов запрета, на. входы 17 и 18 подаются соответственно константы m < и ш„ ° m .

С генератора 4 тактовых импульсов через элемент И 5 непосредствен30

При одновременном обнулении модульных счетчиков 1 и 2 на выходе элемента И 8 формируется сигнал. который обнуляет триггер 10, сигнал с нулевого выхода триггера 10 устанавливает коэффициент пересчета второго мо" дульного счетчика равным /ш, ° т mod< и7 э

Одновременно этот сигнал опрашйвает элемент И 7 и разрешает элемент ИЛИ

12 независимо от состояния модульного счетчика 1, а сигнал с единичного выхода триггера 10 закрывает блок

13 элементов И и открывает блок 14 элементов запрета, через который с входа 13 поступает константа m< m и суммируется с содержимым сумматора

15 Ри одновременном обнулении модульных счетчиков 2 и 3, на выходе элемента И 7 формируется сигнал, триггер 9 обнуляется, и подача импульсов через элемент И 5 прекращается.

Результат преобразования снимается с выхода 19 преобразователя.

)200430

Составитель А. Клюев

Техред М. Гергель

Редактор В.Иванова

Корректор A-Тяско

Филиал ППП "Патент", г.ужгород, ул.Проектная,4

Заказ 7879/62 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1)3035, Москва, Ж-35, Раушская наб., д. 4/5