Преобразователь кода числа из системы остаточных классов в позиционный код

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ . РЕСПУБЛИК (19) (11) (51) 4 Н 03 М 7/18 асад@

° 3lfpq

ОПИСАНИЕ ИЗОБРЕТЕНИ "::;.:,:,, ц ф

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21 )- 3409961/24-24 (22) 16. 05.82 (46) 23.12.85. Бюл. Ф 47 (71) Ленинградский ордена Ленина и ордена Красного Знамени механичес" кий институт (72) В.П.Лукоянов, О.Н.Музыченко, Н.К.Кора и А.В.Ростовский (53) 681.3(088.8) (56) Толстяков В.С. и др. Обнаружение и исправление ошибок в дискретных устройствах. N. Советское радио, 1972, с. 55, рис. 1.6.

Авторское свидетельство СССР

N - 554536, кл. G 06 F 5/02, 1977, (54)(57) ПРЕОБРАЗОВАТЕЛЬ КОДА ЧИСЛА

ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД, содержащий модульные сумматоры, первые входы которых соединены с информационными входами преобразователя по соответствующим основаниям с первого по предпоследний, и позиционный сумматор, соединенный выходами с выходами преобразователя, отличающийся тем, что, с целью повышения быстродействия, он содержит шифраторы в дополнитель- ные коды по данному. основанию кратных остальных оснований, шифратор в код произведения оснований и дешифратор, один вход которого подключен к тактовому входу позиционного сумма. тора и тактовому входу преобразователя, а другие входы соединены с выходами соответствующих модульных сумматоров, вторые входы каждого модульного сумматора подключены к выходам соответствующих шифраторов в дополнительные коды по данному основанию кратных остальных оснований, входы которых соединены с соответствующими выходами дешифратора и с соответствующими входами шифратора в код про произведения оснований, выходы которого подключены к входам разрядов позиционного сумматора, последний выход дешифратора является выходом признака окончания работы преобразователя, информационные входы преобразователя по последнему основанию соединены с входами соответствующих разрядов позиционного сумматора, установочный вход которого подключен к входу признака начала работы преобразователя.

1 12

Изобретение относится к области автоматики и вычислительной техники, а именно к устройствам обработки информации в системе остаточных классов. . Целью изобретения является повышение быстродействия преобразователя.

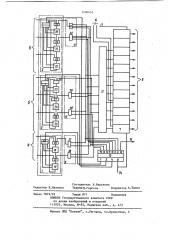

На чертеже представлена функциональчая схема преобразователя для случая перевода числа из системы остаточных классов с основаниями Р! =3, Р =5, Р =7, Р =11 в позиционный двоичный код.

Преобразователь содержит модульные сумматоры 1 - 3, соединенные первыми входами с информационными входами 4 — 6 по соответствующим основаниям (Р„=З, Р =5, Р =7), позиционный, сумматор 7, подключенный выходами к выходам 8, шифраторы 9 — 11 в дополнительные коды по основаниям

Р, =3, Рг 5, Рз =7 крат"ых остальных оснований, шифратор 12 в код произведения оснований и дешифратор 13,.

-первый вход которого подключен к тактовому входу сумматора 7 и тактовому входу 14 преобразователя, а другие входы соединены с выходами сумматоров 1-3, вторые входы которых подключены к выходам соответствующих шифраторов 9-11, входы которых соединены с соответствующими выходами . дешифратора 13 и соответствующими. входами шифратора 12, выходы которого подключены по входам разрядов сумматора 7, последний выход дешифратора 13 является выходом 15 признака окончания работы преобразователя, информационные входы.16 по основанию

Р1=1! соединены с входами соответствующих разрядов сумматора 7, установочный вход которого подключен к входу 17 признака начала работы пре-. образователя.

Сумматор 1 содержит одноразрядные двоичные сумматоры 18 и 19 элементы ИЛИ 20 и 21 и элемент И-ИЛИ 22.

Сумматор 2 содержит одноразрядные двоичные сумматоры .23 -.25, элементы ИЛИ 26-28 и элемент И-ИЛИ 29.

Сумматор 3 содержит одноразрядные двоичные сумматоры 30-32, элементы

ИЛИ 33-35 и элемент И-ИЛИ 36. Шифратор 9 содержит элементы ИЛИ 37 и

38, шифратор 10 — элементы ИЛИ 39

00432

Работа происходит таким образом до обнуления какого-либо очередного модульного сумматора 1-3 (или группы таких сумматоров), после чего появившийся сигнал с выхода этого сумматора вызывает переключение дешифратора 13 и в дальнейшем тактовые импульсы на обнулившийся сумматор, как и на обнулившиеся ранее,не по40 ступают. Одновременно с этим коррек-. тируются код числа, записываемого в позиционный сумматор 7 (добавляются сомножители, равные основаниям обнулившихся сумматоров, и коды по со45 ответствующим основаниям, добавляемые к необнулившимся сумматорам 1-3.

Процесс таким образом повторяется до полного обнуления всех сумматоров 2-3, после чего происходит последнее переключение дешифратора 13 и тактовые импульсы появляются на выходе 15, что является признаком окончания преобразования, при этом в

-позиционном сумматоре 7 записан дво55 ичный код преобразуемого числа, 2 и 40, шифратор ll — элементы ИЛИ 41 и 42.

Устройство работает следующим образом.

5 В исходном состоянии сумматоры 3 и 1 сброшены. Переводимый код в системе остаточных классов подается на входы 4, 5, 6 и 16 и записывается в сумматоры l, 2, 3 и 7 (при этом подается управляющий сигнал на вход

27).

Далее на вход 14 преобразователя подаются импульсы, которые появляются на соответствующем выходе

15 дешифратора 13 и поступают на входы лишь тех шифраторов 9 — 11, которые связаны с входами необнулившихся модульных сумматоров 1-3. Прн этом с каждым тактом к содержимому этих сумматоров прибавляется дополнительный код по основанию соответствующего сумматора для числа, равного произведению модулей всех обнулившихся сумматоров 1-3 с учетом старшего основания системы остаточных классов. Одновременно к содержимому позиционного сумматора 7 в каждом такте прибавляется число, равное произведению модулей всех обнулившихся сумматоров.

1200432

Составитель В.Березкин

Редактор В.Иванова ТехредМ.Гергель Корректор, A.Taczo

Заказ 7879/б2 Тираж 871 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4