Стабилизированный преобразователь напряжения с защитой

Иллюстрации

Показать всеРеферат

СТАБИЛИЗИРОВАННЫЙ НРЕОБРАЗОВАТЕЛБ НАПРЯЖЕНИЯ С ЗАЩИТОЙ по авт. св. № 1141391, отличающийся тем, что, с целью повышения функциональной надежности путем увеличения числа повторных включений преобразователя при незначительном перерыве между следующими одна за другой перегрузками, формирователь импульса перегрузки снабжен дополнительным выходом, который через введенные дополнительный диод и третью интегрирующую цепь подключен к второму входу элемента И дополнительного узла повторного включения, при этом время заряда третьей интегрирующей цепи должно быть меньше времени заряда второй интегрирующей цепи, а время ее разряда должно превышать длительность бестоковой паузы преобразователя.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4

ОПИСАНИЕ ИЗОБРЕТ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1141391 (2! ) 3806004/24-07 (22) 10.10.84 (46) 30.12.85. Бюл. № 48 (71) Научно-производственное объединение космических исследований при АН АЗССР (72) 1. А. Асадов, Э. М. Бекиров, А. А. Багиров, И. Д. Рейфман и С. В. Мкртычев (53) 621.314.58 (088.8) (56) Авторское свидетельство СССР № 114139, кл. G 05 F i/569, 1983. (54) (57) СТАБИЛИЗИРОВАННЫИ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЗАЩИТОЙ по авт. св. № 1141391, отличающийся тем, что, с целью повышения функциоÄÄSUÄÄ 1201821 нальной надежности путем увеличения числа повторных включений преобразователя при незначительном перерыве между следующими одна за другой перегрузками, формирователь импульса перегрузки снабжен дополнительным выходом, который через введенные дополнительный диод и третью интегрирующую цепь подключен к второму входу элемента И дополнительного узла повторного включения, при этом время заряда третьей интегрирующей цепи должно быть меньше времени заряда второй интегрирующей цепи, а время ее разряда должно превышать длительность бестоковой паузы преобразователя.

1201821

Изобретение относится к преобразовательной технике и может быть использовано при разработке источников вторичного электропитания.

Цель изобретения — повышение функциональной надежности путем увеличения числа повторных включений преобразователя при незначительном перерыве между следующими одна за другой перегрузками.

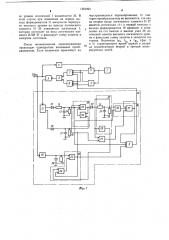

На фиг. 1 приведена структурная схема предлагаемого стабилизированного преобразователя напряжения с защитой; на фиг. 2 и 3 — временные диаграммы работы блока защиты.

Преобразователь содержит генератор I тактовых импульсов, подключенный к входу счетного триггера 2 и входу широтно-импульсного модулятора (ШИМ) 3, второй вход которого через узел 4 обратной связи подключен к выходу выпрямителя с фильтром 5, установленного на выходе усилителя 6 мощности, управляющие входы которого подключены к выходам двух логических элементов И 7 и 8, первые входы которых подключены к выходам счетного триггера 2, вторые объединенные входы — к выходу ШИМ 3, а третьи объединенные входы— к выходу элемента ИЛИ вЂ” HE 9 блока 10 защиты, который содержит формирователь

11 импульсов перегрузки, к первому выходу которого подключена вторая интегрирующая цепочка на диоде 12, конденсаторе 13 и резисторах 14 и 15, а к второму выходу диод 16 и третья интегрирующая цепочка на конденсаторе 17 и резисторе 18. Формирователь 19 импульсов перенапряжения через первую интегрирующую цепь на конденсаторе 20 и резисторе 21 подключен к первому входу элемента ИЛИ 22 основного узла 23 повторного включения, другой вход которого соединен с выходом логического элемента И 24. Выход логического элемента ИЛИ 22 соединен с первым входом элемента ИЛИ вЂ” НЕ 9, с первым входом логического элемента ИЛИ 25 дополнительного узла 26 повторного включения и с первым входом логического элемента И 27. Первый вход элемента И 24 соединен с выходом логического элемента HE 28 узла 29 логической задержки, вход которого через диод 30 и времязадающую интегрирующую цепочку на резисторах 31 и 32 и конденсаторе 33 подключен к выходу элемента ИЛИ 25, второму входу элемента И 27 и первому вхо1 ду логического элемента И 34, другой вход которого подключен через третью интегрирующую цепочку и диод 16 к второму выходу формирователя 11 импульсов перегрузки. Второй вход логического элемента ИЛИ

25 подключен через вторую интегрирующую цепочку к первому выходу формирователя 11 импульсов перегрузки, второму входу элемента ИЛИ-НЕ 9 и первому входу логического элемента И 35 узла 36 логической памяти, 5

1О

25 зо

55 другой вход которого через вторую интегрирующую цепочку соединен с выходом дополнительного узла 26 повторного включения. Выход логического элемента И 35 соединен с первым входом логического элемента ИЛИ 37, второй вход которого подключен к выходу логического элемента И 27, а выход — со своим третьим входом и третьим в ходом элем ента ИЛ И вЂ” Н Е 9.

Устройство работает следующим образом;

При подаче питающего напряжения на входах элемента ИЛИ вЂ” НЕ 9 отсутствуют высокие логические уровни. На его выходе формируется логическая 1, которая дает разрешение на прохождение импульсов с парафазных выходов счетного триггера 2 на первые входы логических элементов И 7 и 8 и с выхода ШИМ 3 на их вторые входы.

Выходное переменное напряжение усилителя 6 мощности преобразуется в постоянное выпрямителем с фильтром 5 и поступает через узел 4 обратной связи на другой вход

ШИМ 3, обеспечивая соответствующее изменение ширины его выходных импульсов.

При возникновении перегрузки на раздельных выходах формирователя 11 импульсов перегрузки появляются высокие логические уровни. При этом параметры второй и третьей интегрирующей цепи выбраны таким образом, что логическая 1 на входе элемента И 34 появляется раньше, чем на входе логического элемента ИЛИ 25, а наличие двух раздельных выходов у формирователя 11 импульсов перегрузки исключает их взаимное влияние. Причем формирователь 11 импульсов перегрузки может быть выполнен, например, на двух однопороговых ком параторах.

На выходе исполнительного элемента

ИЛИ-НЕ 9 формируется логический О. Логические элементы И 7 и 8 запираются. Одновременно с первого выхода формирователя 11 импульсов перегрузки высокий логический уровень поступает на вход логического элемента И 35 узла 36 логической памяти, при этом на другом его входе сохраняется логический О. Если после срабатывания блока 10 защиты и разряда конденсатора !3 через промежуток времени, соответствующий бестоковой паузе, не происходит следующее включение преобразователя, то конденсатор 17 разряжается до уровня логического О и на выходе логического элемента ИЛИ 25 возникает логический О, что обуславливает немедленный разряд конденсатора 33 узла

29 логической задержки. Если же через небольшой промежуток времени вновь возникает перегрузка (фиг. 3), то на выходах формирователя импульсов перегрузки — высокие логические уровни, причем логическая 1 будет сохраняться на выходе элемента И 34 до тех пор, пока происходят повторные переключения преобразователя и не зарядится

1201821 до уровня логической 1 конденсатор 33. В этом случае при появлении на первом выходе формирователя 11 импульсов перегрузки высокого уровня на выходе логического элемента И 35 появляется логическая 1, которая поступает на вход логического элемента ИЛИ 37 и фиксирует схему запрета в запертом состоянии.

После возникновения перенапряжения происходит однократное включение преобразователя. Если включение произойдет на неустранившееся перенапряжение, то повторно преобразователь не включится, так как на втором входе логического элемента И 27 имеется логическая «1» и первый импульс с выхода формирователя 19 приводит к появлению на его выходе и выходе узла 36 логической памяти высокого логического уровня и фиксации схемы защиты в запертом состоянии. Величины ty,, t> и 1р (фиг. 2 и 3) характеризуют время заряда и разряда конденсаторов второй и третьей интегрирующих цепей.

Редактор Ю. Середа

Заказ 8091,49

Соггавитсль 1.!. Никитин

Тс«рс; И. Всрсс Корректор.! 11нлипенкг

Тира и 8t)2 1! одп нс иск

ВНИИПИ Государственного комитета СССР по делам изобрегений и открытий

113035, Москва. Ж вЂ” 35. Раушская наб.. д. 45

Филиал ППП «Патент», г. Ужгород, ул. Проекзнаи, 4