Дифференциальный усилитель

Иллюстрации

Показать всеРеферат

ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий основной дифференциальный каскад,каждое плечо которого выполнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего п-р-п-структуру, включенного по схеме с общим коллектором, и второго транзистора, имеющего р-п-рструктуру и включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов основного дифференциального каскада включен первый источник тока, базы первых транзисторов основного дифференциального каскада подключены к базам первого и второго дополнительных транзисторов, имеющих р-п-р-структуру и включенных по схеме с общим коллектором, в эмиттерных цепях которых включены второй и третий источники тока соответственно , дополнительный дифференциальный каскад, выполненный на транзисторах, имекицих р-п-р-структуру , базы, которых подключены к эмиттерам первого и второго дополнительных транзисторов, коллекторы к ксищектррам или эмиттерам вторь1х транзисторов основного дифференциального каскада, а в общей змиттерной цепи - четвертый источник тока, выполненный на транзисторе, имеющем р-п-р-структуру, элемент компенсации, выполненный на третьем дополнительном транзисторе, имеющем п-р-п-структуру, и четвертом дополнительном транзисторе, имеющем р-п-р-структуру и включенном по схеме с общим коллектором-, эмиттер которого подключен к базе транзистора четвертого источника тока, а эмиттер третьего дополнительного транзистора подключен к объединенным коллекторам первых транзисторов основного дифференциального О) каскада, отличающийся тем, что, с целью повышения стабильности токового режима, в него введен двухколлекторный транзистор, имеющий р-п-р-структуру, при этом второй и третий источники тока выполнены на трехколлекторном транзисторе , имеющем р-п-р-структуру, эмиттер которого подключен к.шине источника питания, первый коллектор и база объединены и через прямосмещенньш диод подключены к эмиттеру четвертого дополнительного транзистора, а второй и третий коллекторы являются выходами соответственно второго и третьего источников тока, эмиттер двухколлекторного транзистора подключен к шине источника питания, первый коллектор и база объединены и подключены к коллектору третьего дополнительного транзистора, а второй коллектор - к эмиттеру транзистора четвертого источника тока.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН ш4 Н 03 F 3/45

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ ф. ад (21) 3719950/24-09 (22) 03,04.84 (46) 30.12.85. Бюл. N - 48 (72) В.В.Матавкин (53) 621.375.024(088.8) (56) Гребен А.Б. Проектирование аналоговых интегральных схем. M.:

Связь, 1976, с. 102.

Авторское свидетельство СССР

У 1117827,кл. Н 03 F 3/45, 1983. (54)(57) ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ, содержащий основной дифференциальный каскад, каждое плечо которого выполнено в виде последовательно соединенных относительно источника питания первого транзистора, имеющего п-р-п-структуру, включенного по схеме с общим коллектором, и второго транзистора, имеющего р-п-рструктуру и включенного по схеме с общей базой, при этом коллекторы первых транзисторов объединены, а в общей цепи без вторых транзисторов основного дифференциального каскада включен первый источник тока, базы первых транзисторов основного дифференциального каскада подключены к базам первого и второго дополнительных транзисторов, имеющих р-п"р -структуру и включенных по схеме с общим коллектором, в эмиттерных цепях которых включены второй и третий источники ток» соответственно, дополнительный дифференциальный каскад, выполненный на транзисторах, имеющих р-п-р-структу-. ру,базы которых подключены »к эмиттерам первого и второго дополнительных транзисторов, коллекторы— к коллекторам или эмиттерам вторых

„Я0„„1202025 А транзисторов основного дифференциального каскада, а в общей эмиттерной цепи — четвертый источник тока, выполненный на транзисторе, имеющем р-п-р-структуру, элемент компенсации, выполненный на третьем дополнительном транзисторе, имеющем п-р-п-структуру, и четвертом дополнительном транзисторе, имеющем р-п-р-структуру и включенном по схеме с общим коллектором., эмиттер которого подключен к базе транзистора четвертого источника тока, а эмиттер третьего дополнительного транзистора подключен к объединенным коллекторам первых транзисто- Е рое оснонного диФФеренциального д1 каскада, отличающийся тем, что, с целью повьппения стабиль- ( ности токового режима, в него введен двухколлекторный транзистор, имею- 1» щий р-п-р-структуру, при этом второй и третий источники тока выполнены на трехколлекторном транзисторе, имеющем р-п-р-структуру, эмиттер которого подключен к шине источника питания, первый коллектор и база объединены и через прямосмещенный фф диод подключены к эмиттеру четвертого дополнительного транзистора, а второй и третий коллекторы являются выходами соответственно второго и третьего источников тока, эмиттер двухколлекторного транзистора под- ) ключен к шине источника питания, первый коллектор и база объединены и подключены к коллектору третьего дополнительного транзистора, а второй коллектор — к эмиттеру транзистора четвертого источника тока.

1 12

Изобретение относится к радиотехнике и может быть использовано. в операционных усилителях.

Цель изобретения — повышение стабильности токового режима.

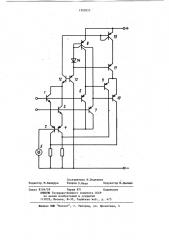

На чертеже представлена принципиальная электрическая схема дифференциального усилителя.

Дифференциальный усилитель содер" жит основной дифференциальный каскад, выполненный на первых транзисторах 1 и 2, имеющих п-р-и-структуру, и вторых транзисторах 3 и 4, имеющих р-п-р-структуру, первом источнике 5 тока, первый и второй дополнительные транзисторы 6 и 7, имеющие р-п-р-структуру, второй и третий источники тока, выполненные на трехколлекторном транзисторе 8, имеющем р-п-р-структуру,дополнительный дифференциальный каскад, выполненный на транзисторах 9 и 10, имеющих р-п-р-структуру, четвертйй источник тока, выполненный на транзисторе 11, имеющем р-ri-p-структуру, элемент компенсации, выполненный на третьем, имеющем п-р-п-структуру, и четвертом, имеющем р-п-р-структуру, дополнительных транзисторах 12, 13, прямосмещенный диод 14, двухколлекорный транзистор 15, имеющий р-п-р-структуру.

Дифференциальный усилитель работает следующим образом.

Величина эмиттерного тока четвертого дополнительного транзистора

13 определяется суммой базовых токов трехколлекторного транзистора 8 и транзистора 11. Выбором величины коэффициента усиления по току трехколлекторного транзистора 8, равного

02025 2

0,5, обеспечивается протекание токов через каждый из коллекторов, соединенных с эмиттерами первого и второго дополнительных транзисторов

5 6 и 7, равных по величине каждый половине базового тока трехколлекторного транзистора 8 ° Величина режимного тока дополнительного дифференциального каскада выбирается, ис10 ходя из требуемых значений по коэффициенту усиления, скорости нарастания выходного напряжения дифференциального усилителя.

Целесообразно определить режим15 ный ток этого каскада равным по величине режимному току основного дифференциального каскада. Это достигается выбором коэффициента усиления по току двухколлекторного тран20 зистора 15, равным 1, Суммирование базовых токов транзисторов 9, 10 с коллекторными токами трехколлекторного транзистора 8 определяет значения эмиттерных и, соответствен25 но, базовых токов первого и второго дополнительных транзисторов 6 и

7, благодаря чему свойство компенсации входных токов дифференциального усилителя сохраняется.

Стабилизация режимного тока до-.. полнительного дифференциального каскада определяется взаимосвязью с токовым режимом основного диф35 ференциального каскада, благодаря равенству или пропорциональности между величиной тока в коллекторах транзистора ll и двухколлекторного транзистора 15 и величиной коллекторного третьего дополнительного транзистора 12, 1202025

Составитель И, Водяхина

Редактор М.Бандура Техред O.Heqe . Корректор М,Демчик

Заказ 8! 041 59 Тираж 871 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035,. Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4