Устройство для исправления ошибок в кодовой комбинации

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШБОК В КОДОВОЙ KOMBHHAUHli, содержащее первьш ключ, последовательно соединенные блок обнаружения ошибок, второй ключ и элемент ilTM, а также первый накопитель, первьп, второй и третий сумматоры по модулю два, отличающееся тем,что, с целью обеспечения исправления ошибок любой кратности, в него введены счетчик адресов, первьй, второй и третий коммутаторы, второй накопитель , дополш1тельные сумматоры по модулю два, дополнительные блоки обнаружения ошибок и дополнительные ключи, выходы которых соединены с соответствующими входами элемента ИЛИ, выход которого является выходом устройства, а также дешифратор служебных слов, дешифратор номера ошибки и регистр сдвига, вход которого является входом устройства, а выходы разрядов соединены с входами дешифратора служебных слов, первьй выход которого соединен с управляющим входом первого ключа, тактовый вход которого объединен с тактовым входом регистра сдвига и является входом тактовой частоты, второй выход дешифратора служебных слов соединен с управляющими входами первого и третьего коммутаторов, третий выход - с первыми входами всех блоков обнаружения ошибок, четвертый выход - с входом счетчика адресов, тактовьп вход которого соединен с выходом первого коммутатора, первый вход которого является входом частоты считываш1я, второй вход первого кoм fyтатopа соединен с выходом первого ключа и информационным входом второго коммутатора, управляющий вход которого соединен с пятым выходом дешифратора служебных слов, первьй и второй выходы второго комi мутатора соединены соответственно с тактовыми входами первого и второСЛ го накопптелей, адресные входы которых объединены и соединены с выходом счетчика адресов, выход последнего разряда регистра сдвига соединен с информационными входами первого и второго накопителей и первым входном N9 третьего коммутатора, второй вход О которого соединен с выходом второго накопителя, выход первого накопителя to соединен с первыми входами первого, о второго, третьего и дополнительных СП сумматоров по модулю два, вторые входы второго, третьего и дополнительных сумматоров по модулю два соединен с выходами дешифратора номера ошибки, первьп4 и второй входы которого соединены соответственно с выходами введенного счетчика ошибок и первого сумматора по модулю два, выход которого соединен также с входом счетчика ошибок, выход второго сумматора по модулю два соединен с вторыми входами второго ключа и блока обнаружения ошибок, выходы

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

1511 1 П 03 Ы 1 3/00

ВСЕСОЮЗЩУ

13,,"..,"... „13

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABT0PCHGMV СВИДЕТЕЛЬСТВУ

БЩ i(9,gg ö

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3750399/24-09 (22) 07.06.84 (46) 30.12.85. Бюл, № 48 (72) 10,Я. lilac, И.Д. Орлевич и В.P. Колосов (53) 621.394.14(088.8) .(56) Авторское свидетельство СССР

¹ 582564, кл. Н 04 Ь 1/10, 1976.

Авторское свидетельство СССР № 944130, кл. Н 04 1 1/10, 1980. (54) (57) УСТР011СТВО ДЛЯ ИСПРАВЛЕШИ

ОШИБОК В КОДОВ011 КОЫБИ11АЦИИ, содержащее первый ключ, последовательно соединенные блок обнаружения ошибок, второй ключ и элемент ИЛИ, а также первый накопитель, первьп, второй и третий сумматоры по модулю два, о т л и ч а ю щ е е с я тел,что, с целью обеспечения исправления ошибок любой кратности, в него введены счетчик адресов, первьп, второй и третий коммутаторы, второй накопитель, дополнительные сумматоры по модулю два, дополнительные блоки обнаружения ошибок и дополнительные ключи, выходы которых соединены с соответствующими входами элемента

ИЛИ, выход которого является выходом устройства, а также дешифратор служебных слов, дешифратор номера ошибки и регистр сдвига, вход которого является входом устройства, а выходы разрядов соединены с входами дешифратора служебных слов, первый выход которого соединен с управляющим входом первого ключа, тактовый вход которого объединен с тактовым входом регистра сдвига и является входом тактовой частоты, второй выход дешифратора служебных слов

„„ЯО„„1202057 A соединен с управляющими входами первого и третьего коммутаторов, третий выход — с первыми входами всех блоков обнаружения ошибок, четвертый выход — с входом счетчика адресов, тактовьпl вход которого соединен с выходом первого коммутатора, первый вход которого является входом частоты считывания, второй вход первого коммутатора соединен с выходом первого ключа и информационным входом второго коммутатора, управляющий вход которого соединен с пятым выходом дешифратора служебных слов, первьп и второй выходы второго коммутатора соединены соответственно

Pg с тактовыми входами первого и второго накопителей, адресные входы которых объединены и соединены с выходом С счетчика адресов, выход последнего разряда регистра сдвига соединен с информационными входами первого и второго накопителей и первым входом третьего коммутатора, второй вход (Я которого соединен с выходом второго накопителя, выход первого накопителя соединен с первыми входами первого, второго, третьего и дополнительных сумматоров по модулю два, вторые

Сл входы второго, третьего и дополни- «3 тельных сулпчаторов по модулю два соединены с выходами дешифратора номера ошибки, первьп и второй входы которого соединены соответственно с выходами введенного счетчика ошибок и первого сумматора по модулю два, выход которого соединен также с входом счетчика ошибок, выход второго сумматора по модулю два соединен с вторыми входами второго ключа и блока обнаружения ошибок, выходы

1202057

20 третьего и допоЛнительных сумматоров по модулю два соединены с вторыми входами дополнительных блоков обнаружения ошибок и одними входами доИзобретение относится к электросвязи и может быть использовано в аппаратуре дискретной информации.

Цель изобретения — обеспечение исправления ошибок любой кратности.

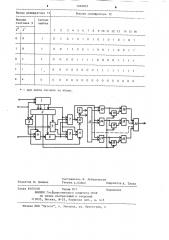

На чертеже представлена структурная электрическая схема устройства для исправления ошибок в кодовой комбинации.

Устройство содержит регистр 1 сдвига, дешифратор 2 служебных слов, первый ключ 3, первый коммутатор 4, второй коммутатор 5, счетчик 6 адресов, первый накопитель 7, второй накопитель 8, счетчик 9 ошибок, пер- 11 вый сумматор 10 по модулю два, третий коммутатор 11, дешифратор 12 номера ошибки, второй сумматор 13 по модулю два, третий сумматор 14 по модулю два, блок 15 обнаружения ошибок, дополнительные блоки 16 обнаружения ошибок, дополнительные сумматоры 17 по модулю два, второй ключ 18, дополнительные ключи 19, элемент ИЛИ 20. 25

Устройство для исправления ошибок в кодовой комбинации работает следующим образом, Принимаемая информация в виде последовательности нулей и единиц проходит через регистр 1, который совместно с дешифратором 2 служит для распознавания служебных слов в потоке кодированной информации и определения их вида.

Восстановление пораженной кодовой комбинации в устройстве проводится в два этапа, На первом этапе производится накопление обоих повторений кодовой комбинации в первом и втором накопи телях 7 и 8 и подготовка к ее исправлению. Работу устройства удобно рассматривать с момента окончания служебного слова, определяющего начало первого повторения. В этот момент 45 открывается первый ключ 3, а второй полнитсльцых ключей, другие входы которых соединены с выходами соответствующих дополнительных блоков обнаружения ошибок.

2 коммутатор 5 устанавливается в таком положении, при котором тактовая час— тота поступает на тактовый вход первого накопителя 7, обеспечивая тем самым запись в него первого повторения кодовой комбинации. Одновременно тактовая частота поступает через первый коммутатор 4 на счетчик 6, обеспечивающий последовательный перебор адресов ячеек первого и второго накопителей 7 и 8.

На время приема служебного слова первый ключ 3 закрывается.

После окончания служебного слова, определяющего начало второго повторения кодовой комбинации, второй коммутатор 5 переключается, обеспечивая запись второго повторения кодовой комбинации во второй накопитель 8 и считывание ранее записанной информации из первого накопителя 7. Одновременно с записью во второй накопитель

8, за счет того, что адресные входы первого и второго накопителей 7 и 8 подключены к одному и тому же счетчику 6, происходит синхронное считывание первого повторения кодовой комбинации из первого накопителя 7 и побитное сравнение ее первым сумматором 10 (выполняющим в этом случае функции схемы сравнения) с вторым повторением кодовой комбинации, поступающим на первый сумматор 10 через третий коммутатор 11. В результате сравнения в местах несовпадения битов первого и второго повторений кодовой комбинации первым сумматором

10 вырабатываются сигналы ошибок.

Поскольку несовпадение одноименных битов в первом и втором повторениях кодовой комбинации не дает однозначного ответа, в каком из повторений возникла ошибка, далее производится следующее. Сигналы ошибки подсчитываются счетчиком 9. Номер ошибки дешифруется дешифратором 12, функцией з 1202 которого является выработка управляющих воздействий на второй, третий и дополнительные сумматоры 13, 14 и 17 (используемые в этом случае как управляемые инверторы) в соответствии с таблицей. Таблица истинности построена для 16-канального дешифратора номера ошибки.

Таким образом, предпринимается попытка направления первого повторения кодовой комбинации (первое повторение выбрано произвольно; с точки зрения возможности восстановления кодовой комбинации оба повторения

1 являются равноправными) путем инвер- 15 тирования битов, не совпадающих с одновременными битами второго повторения, причем охватываются все возможные варианты искажения первого повторения кодовой комбинации, что 20 неизбежно приводит к нахождению верного варианта исправления. Проверка правильности исправления кодовой комбинации производится блоками 15 и 16 обнаружения ошибок, являющими- 25 ся упрощенными вариантами декодера и реагирующим лишь на правильно принятую комбинацию.

Таким образом, на первом этапе производится фиксация канала, в ко- 30 тором инвертирование битов в потенциальных местах возникновения ошибок привело к восстановлению данной конкретной кодовой комбинации. При этом открывается второй ключ 18 или со35 ответствующий дополнительный ключ

19, подготавливая тем самым возможность прохождения восстановленной комбинации на выход.

Вывод восстановленной комбинации 40 по каналу, определенному на первом этапе, производится на втором этапе за время приема служебного слова, определяющего начало первого повторе-. ния очередной кодовой комбинации. С 45 этой целью после приема этого служебного слова первый ключ 3 закрывается, первый коммутатор 4 переключается на частоту выдачи (номинал частоты

057 4 определяется временем приема служебного слова и максимально возможным объемом информации в кодовой комбинации), а третий коммутатор 11 подключает к входу первого сумматора 10 выход второго накопителя 8. Частота выдачи поступает на счетчик 6, управляющий считыванием информации из первого и второго накопителей 7 и 8 (при этом имеется в виду, что информация в накопителе хранится до тех пор, пока в него не будет записана новая, и при многократном считывании не разрушается). Информация второго накопителя 8 используется в этом случае для нахождения мест несовпадений с целью выработки сигналов ошибок в процессе синхронного считывания комбинации первого и второго повторений из первого и второго накопителей 7 и 8. При этом первое повторение кодовой комбинации, проходя через сумматоры 13, 14 и 17, подвергается тем же управляющим воздействиям, что и на первом этапе, т.е. производится повторное восстановление комбинации с тем отличием, что на этом этапе оказывается открытым второй ключ 18 или один иэ дополни-! тельных ключей 19 пропускающий восЭ

I становленную комбинацию через элемент ИЛИ 20 на выход.

После окончания служебного слова

1на блоки 15 и 16 обнаружения ошибки поступает импульс сброса, и процесс восстановления очередной кодовой комбинации повторяется.

Сброс счетчика 6 производится как в начале, так и в конце каждого служебного слова.

Число каналов устройства зависит от суммарного числа ошибок, могущих возникнуть в обоих повторениях кодовой комбинации, и определяется достоверностью передачи информации в системах связи, в которых планируется работа устройства, и максимального объема информации в кодовой комбинации.

1202057

Входы дешифратора 12

Выходы дешифратора 12

Сигнал ошибки

Выходы счетчика 9 о

2 2

* — при любом сигнале на входе.

Редактор M. Цицика

Заказ 8105/60 Тираж 871

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

2 3 4 5 6 7 8 9 10 11 12 13 !4 15 16

0 1 0 1 0 1 0 0 1 0 1 0 1 0

0 0 1 0 0 1 0 0 1 1 0 0 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Составитель Н, Лебедянская

Техред Л.Бойко Корректор А ° Тяско