Устройство для измерения характеристик дискретного канала

Иллюстрации

Показать всеРеферат

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ . ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА, содержащее последовательно соединенные датчик эталонной последовательности и первый сумматор, последовательно соединенные датчик дополнительной последовательности и второй сумматор, выход которого подключен к установочному входу счетчика несовпадений, первый дешифратор, входы которого соединены с другими выходами датчика дополнительной последовательности , последовательно соединенные первый элемент И и первый триггер, первый элемент ИЛИ, второй, третий, четвертый и пятый элементы И, отличающееся тем, что, с целью повьшения достоверности измерения величины фазового рассогласования и определения его знака, в него введены последовательно соединенные второй дешифратор, первый элемент ЗАПРЕТ, второй триггер второй элемент ЗАПРЕТ, третий триггер и второй элемент ИЛИ, выход которого подключен к первому входу второго элемента И, последовательно соединенные счетчик фазового сдвига , вход которого соединен с выходом второго элемента И, и индикатор, четвертый триггер, включенный между выходом пе; вого сумматора и первым входом третьего элемента И, выход которого подключен к сигнальному входу счетчика несовпадений, третий дешифратор, включенный между другими выходами датчика эталонной последовательности и первым входом первого элемента И, при этом выход четвертого элемента И через первый элемент ИЛИ подключен к входу датчика дополнительной последовательности , выход пятого элемента И - к другому входу первого элемента ИЛИ, (Л первый вход четвертого элемента И соединен с вторыми входами первого сумматора и второго сумматора, первый вход которого соединен с первым входом пятого элемента И, второй вход которого соединен с вторым вхоto дом четвертого элемента И, с вторым входом первого элемента И, с выходом о ю счетчика несовпадений и вторыми входами первого и второго элементов ЗАПо о РЕТ, выход второго сумматора подключен к другому входу четвертого триггера , входы третьего дешифратора соединены с входами второго дешифратора, выход которого подключен к другому входу первого триггера, выход первого дешифратора подключен к второму входу второго триггера и к третьему входу второго элемента ЗАПРЕТ, выход второго дешифратора подключен к второму входу третьего триггера, выход которого подключен к третьему входу первого элемента ЗАПРЕТ и к другому входу индикатора, выход второго триг

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1202061

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ. ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

3C; rg r.-,, g " !

Ю

С5 (21) 3759898/24-09 (22) 21. 06. 84 (46) 30. 1 2. 85 Бюл. Р 48 (71) Ленинградский электротехнический институт связи нм.проф.М.А.БончБруевича (72) Л.П.Пуртов, Н,В.Гольцова и С.В,Ефимов (53) 621.396.664(088.8) (56) Авторское свидетельство СССР

У 3706329 кл. Н 04 В:3/46, 1971 °

Авторское свидетельство СССР

9 535743, кл. Н 04 В 3/46, 1974. (54)(57) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ

ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА, содержащее последовательно соединенные датчик эталонной последовательности и первый сумматор, последовательно соединенные датчик дополнительной последовательности и второй сумматор, выход которого подключен к установочному входу счетчика несовпадений, первый дешифратор, входы которого соединены с другими выходами датчика дополнительной последовательности, последовательно соединенные первый элемент И и пер. вый триггер, первый элемент ИЛИ, второй, третий, четвертый и пятый элементы И, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности измерения величины фазового рассогласования и определения

его знака, в него введены последовательно соединенные второй дешифратор, первый элемент ЗАПРЕТ, второй триггер второй элемент ЗАПРЕТ, третий .триггер и второй элемент ИЛИ, выход которого подключен к первому входу второго элемента И, последователь(51) 4 H 04 В 3/46//Н 04 L 11/08 но соединенные счетчик фазового сдвига, вход которого соединен с выходом второго элемента И, и индикатор, четвертый триггер,.включенный между выходом пе.. вого сумматора и первым входом третьего элемента И, выход которого подключен к сигнальному входу счетчика несовпадений, третий дешифратор, включенный между другими выходами датчика эталонной последовательности я первым входом первого элемента И, при этом выход четвертого элемента И через первый элемент ИЛИ подключен к входу датчика дополнительной последовательности, выход пятого элемента И вЂ” к другому входу первого элемента ИЛИ, первый вход четвертого элемента И соединен с вторыми входами первого сумматора и второго сумматора, пер-. вый вход которого соединен с первым входом пятого элемента И, второй вход которого соединен с вторым входом четвертого элемента И, с вторым входом первого элемента И, с выходом счетчика несовпадений и вторыми входами первого и второго. элементов ЗАПРЕТ, выход второго сумматора подключен к другому входу четвертого триггера, входы третьего дешифратора соединены с входами второго дешифратора, выход которого подключен к другому входу первого триггера, выход первого дешифратора подключен к второму входу второго триггера и к третьему входу второго элемента ЗАПРЕТ, выход второго дешифратора подключен к второму входу третьего триггера, выход которого подключен к третьему входу первого элемента ЗАПРЕТ и к другому входу индикатора, выход второго триг1202061

repa подключен к.другому Входу второго элемента ИЛИ, а выход первого триггера — к установочным входам второго. и третьего триггеров.

Изобретение относится к электросвя-"- вого сумматора 7 появляется сигнал

l зи и может быть использовано для полу- который переводит четвертый триггер чения статистических данных о характе- 13 в единичное состояние, вследствие ре распределения ошибок синхронизации чего на выходе третьего элемента в каналах связи. И 14 появляется последовательность

Цель изобретения — повышение досто- импульсов, число которых подсчитыверности измерения величины фазового вается счетчиком 15 несовпадений, рассогласования и определение его Несовпадение разрядов на входах перзнака. вого сумматора 7 возможно по двум

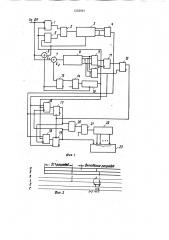

На фиг.1 представлена структурная 10 причинам: иэ-за ошибок трансформаэлектрическая схема устройства для ции и иэ-за ошибок синхронизации. измерения характеристик дискретного Необходимо, чтобы счетчик 15 подсчиканала (ДК); на фиг. 2 — временные тывал несовпадение ошибок синхронидиаграммы работы устройства для слу- эации. Для этого. испытательная посчая отрицательного сбоя фазы, на фиг.315 ледовательность поступает из ДК временные диаграммы работы устройства через четвертый элемент И 1 и первый для случая положительного сбоя фазы; элемент ИЛИ 2 на вход датчика ДПП 3. на фиг.4 — временные диаграммы для . Последовательность, вырабатываемая случая отрицательного сбоя фазы вблизи ДДП 3, и последовательность, прохоконца рекурренты. 2п дящая из канала, сравниваются с помоУстройство содержит четвертый эле- щью второго сумматора 6. При отсутмент И 1, первый элемент ИЛИ 2, дат- ствии ошибок трансформации, но при чик дополнительной последовательности наличии сбоя фазы в канале на выхо(ДДП) 3, первый дешифратор 4, пятый де сумматора 6 имеется последоваэлемент И 5, второй сумматор 6, пер- 25 тельность нулей. При наличии ошибок вый. сумматор 7, датчик эталонной пос- трансформации на выходе второго сумледовательности (ДЭП) 8, третий дешиф- матора 6 появляется сигнал, Таким ратор 9, второй дешифратор 10, первый образом, второй сумматор 6 фиксируэлемент И 11, первый триггер 12, чет- ет ошибки трансформации, а первый вертый триггер 13, третий элемент Зб сумматор 7 — ошибки синхронизации

И 14, счетчик 15 несовпадений, первый и трансформации. Число разрядов неэлемент 3AIIPET 16, второй триггер 17, совпадения, появившихся на выходе второй элемент ЗАПРЕТ 18, третий триг- сумматора 7, проходя через четвертый гер 19, второй элемент ИЛИ 20, второй триггер 13 и третий элемент И 14, элемент И 2 1, счетчик 22 фазового 3 подсчитывается счетчиком 1 5 ° Если сдвига, индикатор 23. имели место ошибки трансформации, сигнал с выхода второго сумматора 6 устройство работает следующим обра сбрасывает четвертый триггер 13 в нулевое состояние и устанавливает

На входы пеРвого сумматоРа 7 посту счетчик 15 также в нулевое состояпают РекУРРентные послеДовательности ние. При наличии ошибок синхронизас выхода ДК и с выхода ДЭП 8. При полном совпадении разрядов рекур- на выходе счетчика 15 оя появляется

Рент на выходе пеРвого сУмматоРа 7 сигнал "Сбой фазы" появляется последовательность нулей, которая не оказывает на схему ника- 4 После определения факта сбоя факого действия. При несовпадении pas- зы необходимо произвести измерение рядов испытательной и эталонной величины и знака сбоя фазы, для чего последовательностей на выходе пер- ДДП 3 переводится в автономный ре1202061 жим, что обеспечивает правильное выделение конца рекуррентной последовательности . Выделение конца испытательной рекуррентной последова« тельностн осуществляется первым дешифратором 4, конца эталонной последовательности — вторым дешифратором

10. Принцип работы устройства основан на сравнении циклов испытательной и эталонной последовательностей, заключающемся в формировании временного интервала между окончаниями рекуррент, и поясняется временной диаграммой, представленной на фиг.2 и 3.

При совпадении циклов испытательной (фиг.2 и 3 а) и эталонной (фиг. 2 и 3 б) последовательностей, что соответствует совпадению сигналов на выходах первого (фиг.2 и .Зв) и второго (фиг.2 и 3r) дешифраторов 4 и 10, третий и второй триггеры 19 и 17 не срабатывают. При опережении испыта" тельной последовательности, что имеет место при отрицательном сбое фазы, срабатывает третий триггер 19 (фиг.2 и Зд), а при отставании — второй триггер 17. Возвращение триггеров в исходное состояние осуществляется сигналом с выходов HpoTHBQIIoJIoxHblx дешифраторов 4 и 10, таким образом, длительность импульса на выходе третьего и второго триггеров 19 и 17 соответствует величине сбоя фазы, Временной интервал, формируемый третьим и вторым триггерами 19 и 17, эквивалентный разности циклов ДЭП 8 и ДДП 3, стробируется тактовыми импульсами (ТИ) с помощью второго элемента И 21 (фиг.2 и Зе), а число импульсов подсчитывается счетчиком 22.

Для того чтобы исключить ложное срабатывание третьего и второго триггеров 19 и 17 в момент окончания измерения, предусмотрены элементы

ЗАПРЕТ 16 и 18. триггеры 19 и 17 разблокированы, 30 схема на 511 разряде ДЭП 8 (фиг.4б) производит измерение сбоя фазы.

В случае отсутствия фиксации сбоя фазы до 500-ro разряда ДЭП 8 при появлении сигнала на выходе третьего дешифратора 9 срабатывает первый элемент И 11 и первый триггер 12 блокирует третий (фиг.4ж) и второй триггеры 19 и 17. На выходе элемента

И 21 (фиг.4и) поступают тактовые. импульсы, которые подсчитываются

40 счетчиком 22 фазового сдвига. Блокировка снимается после 511-ro разряда ДЭП 8, т.е. к началу следующего цикла. Начало блокировки — 500-й разряд †. выбрано условно. При испыта45 киях на реальном канале эту величину корректируют.

В том случае, если имело место опережение испытательной последовательности, но произошло это вблизи конца рекуррентной последовательности, когда ДДП 3 (фиг. 4а) уже не успеет выделить конец рекурренты нли когда сбой произошел непосредственно на дешифрируемых разрядах, в схеме предусмотрена защита, состоящая в блокировке участка рекурренты в интервале 500-511 разрядов. Интервал блокировки формируется первым триггером .

12 (фиг..4е) при отсутствии сбоя фазы, т.е. измерение сбоя фазы отрицательного знака не производится в текущем цикле, если сбой произошел после

500-го разряда. Измерение производится в следующем цикле. Схемно это осуществляется следующим образом.

На выходах первого дешифратора 4 (фиг.4в) и второго дешифратора 10 (фиг.4г) формируются соответствующие импульсы. При наличии сбоя фазы в интервале 1-500 разрядов сигнал на выходе первого элемента И 11 при появлении сигнала на выходе третьего дешифратора 9 (фиг.4д) не появляется, первый триггер 12 не срабатывает, 1202061

Ю

8 г д

1202061

Е д г д е

Ю

Ю б г д

Ю

Ж и

Фис. 4

Составитель А. Сеселкин

Редактор М,Циткина Техред Ж.Кастелевич Корректор С.Бекмар

Заказ 8107/61 Тирах 658 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж- 35, Раушская наб., д. 4/5

Филиал ППП "Патент", r.Óçãîðîä, ул.Проектная, 4