Оперативное запоминающее устройство с коррекцией информации

Иллюстрации

Показать всеРеферат

СО)03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) (5D 4 С 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

Е»

Р.,Г ( »

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3774803/24-24 (22) 23 ° 07.84 (46) 07.01.86. Бюл. №- 1 (72) В.Е. Подтуркин и А.А. Умблия (53) 681.327(088.8) (56) Авторское свидетельство СССР

1(- 744737, кл. С 11 С 29/00, 1978.

Электроника, № 24, 1979, с. 27, рис. 2. (54)(57) ОПЕРАТИВНОЕ ЗАПОМИНАЮШЕЕ

УСТРОЙСТВО С КОРРЕКЦИЕЙ ИНФОРМАЦИИ, содержащее основной и контрольный накопители, блок контроля, выходы которого соединены с информационными входами контрольного накопителя и дешифратора, выходы которого подключены к одним из управляющих входов блока коррекции, одни из входов и выходов которого соединены соответственно с выходами основного накопителя и с информационными входами основного накопителя и одним из входов блока контроля, другие входы которого подключены к выходам контрольного накопителя, другие входы и выходы блока коррекции являются информационными входами и выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, в него введены сумматоры по модулю два, коммутатор, регистр команд, регистр данных, регистр контрольного кода, регистр признака ошибки, элемент ИЛИ-И и элемент И, причем входы первой группы первого сумматора по модулю два соединены с выходами блока контроля, входы первой группы второго сумматора по модулю два и регистра данных подключены к выходам контрольного накопителя, выходы основного накопителя соединены с входами второй группы сумматоров по модулю два и регистра данных, выходы которого подключены к входам третьей группы первого сумматора по модулю два, выходы и входы четвертой группы ко— торого соединены соответственно с входами и выходами регистра контрольного кода и одними из входов коммутатора, выходы которого подключены к входам регистра признака ошибки, выходы которого соединены с входами третьей группы второго сумматора по модулю два, выходы которого подключены к другим входам коммутатора, выходы регистра команд соединены соответственно с прямым входом элемента И и с управляющим входом коммутатора и инверсным входом элемента И, выход которого подключен к управляющему входу коммутатора, прямые входы элемента ИЛИ-И соединены с одними из выходов блока контроля, другой выход которого подключен к инверсному входу элемента

ИЛИ-И, выход которого и другой выход блока контроля являются соответственно выходами сигналов четной и нечетной ошибок устройства, контрольными выходами которого являются выходы регистра признака ошибки и контрольного накопителя, одним из управляющих входов устройства являются входы записи регистра данных, регистра контрольного кода накопителей, блока контроля и другой управляющий вход блока коррекции, другими управляющими входами устройства являются соответственно входы рег стра команд, вход записи регистра

- признака ошибки и вход начальной

1?03364 установки регистра контрольного кода.

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения — повьш ение надежности устройства.

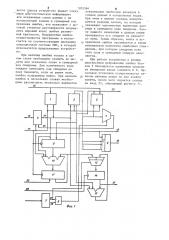

lIa фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 и 3 соответственно функциональные схемы наиболее предпочтительных вариантов выполнения блока контроля и блока коррекции.

Предлагаемое устройство содержит (фиг. 1) основной 1 и контрольный 2 накопители, блок 3 контроля, дешифратор 4, блок 5 коррекции, элемент

ИЛИ-И 6, регистр 7 команд, элемент

И 8, регистр 9 данньгх, первый сумматор 10 по модулю два, регистр 11 контрольного кода, коммутатор 12, второй сумматор 13 по модулю два и регистр 14 признака ошибки.

На фиг. 1 обозначены адресные входы 15, информационные входы и выходы 16, один из управляющих входов 17, контрольные выходы 18-21 и другие управляющие входы 22 и 23 устройства, входы и выходы 24 и входы 25 блока 5 коррекции, выходы

26 и 27 регистра 7 команд. Входы 17, 22 и 23 предназначены для подачи сиг— налов управления записью, чтением и начальной установкой устройства соответственно. Блок 3 контроля содержит (фиг. 2) сумматоры 28 и 29 и элемент И 30. Каждый из разрядов блока 5 коррекции содержит (фиг.3) элемент, НЕРАВНОЗНАЧНОСТЬ 31 и формирователи 32 и 33 сигналов.

Предлагаемое устройство работает следующим образом.

B зависимости от двухразрядного кода, заносимого в регистр 7, устройство работает либо в основном режиме, либо в режиме диагностики, либо в режиме исправления однократных ошибок.

При наличии нулевых уровней на выходах регистра 7 устройство рабо5

1Q

ЗО

„,1 тает в основном режиме. При считывании на входе регистра 7 присутствует нулевой уровень. На входы 15 поступает адрес., в соответствии с которым в накогителях 1 и 2 выбира— ются соответствуюшие ячейки памяти.

Данные из накопителей 1 и 2 поступают на входы блока 3. При этом из накопителя 1 поступает слово данных, а из накопителя 2 контрольный код

Хемминга сформированный для данно го слова данных при записи. Блок 3 формирует код признака ошибки, При этом отсутствию ошиоки соответствуеT нулевой код признака ошибки, В случае, если ошибка имеет нечетную кратность (К (93, .)) -".a выходе 18 формируется осведомительный сигнал,. получаемый как сумма по модул:с два всех разрядов накопителей 1 и 2, В с .лучае ошибки с четной крат IGcть:î (К=2, 4 ...) при наличии на прямых вхацах элемента ИЛИ-!! о ненуле;-ого кода признака ошибки на вьжоде 19 формируется сигнал. Код признака ошибки поступает также на входы дешифратора 4, однако по"KDJIBK5 па управляющий вход дешифратора - поступает с выхода элемента И 8 нулевой уровень, дешифратор 4 не формирует корректирующих сигналов. При этом данные с выходов накопителя 1 передаются на входы 24 без коррекции, поскольку на входы 25 блока 5 не поступают сигналы коррекции, а на входе 17 присутствует нулевой уровень, переключающий блок 5 на выдачу данных на выходы 16. При заииги на входы 15 поступает адрес, выбирающий требуемую ячейку памяти. На „û 16 поступает слово данных. На время установления адреса на входе 17 присутствует нулевой уровень. Слово данных с контрольным кодом из накопителей 1 и 2 поступает на входы регистра 19. По переднему фронту импульса записи па входе 17 в регистре 19 фиксируется сло1203364

15

25

35

45

55 во данных, хранившееся в выбранной ячейке памяти, со своим контрольным кодом. Блок 5 по сигналу на входе

17 переключается на передачу слова данных с входов 16. Сигнал записи на входе 17 переключает накопители

1 и 2 в режим записи. Слово данных заносится в выбранную ячейку накопителя 1, а также поступает на одни из входов блока 3, на другие входы которого поступает нулевой код с выходов накопителя 2. При этом блок

3 формирует контрольный код Хемминга, записывающийся в накопитель 2. Сформированный таким образом контрольный код, совместно со словом данных поступают на первую и вторую группы входов сумматора 10, на третью группу входов которого с выходов регистра 9 поступает слово данных с контрольным кодом, хранившиеся в выбранных ячейках накопителя 1 до поступления сигнала записи, а на четвертую группу входов сумматора

10 поступает общий контрольный код с выходов регистра 11. Во время действия сигнала записи на входе 17 сумматор 10 осуществляет формирование ! нового значения общего контрольно го кода, который по заднему фронту ,сигнала записи на входе 17 фиксируется в регистре 11. На этом цикл записи заканчивается.

Для переключения устройства в режим исправления одиночных ошибок в регистр 7 заносится код с единичным значением на выходе 26. При этом с выхода элемента И 8 на вход дешифатора 4 поступает единичный уровень. При записи в этом режиме устойство функционирует аналогично основному режиму. При считывании формируемый блоком 3 код признака ошибки поступает на входы дешифратора 4. Если код признака ошибки не нулевой, то дешифратор 4 на одном из своих выходов формирует сигнал коррекции, поступающий на соответствующий разряд входа 25 блока 5, который при передаче данных на выходы 16 инвертирует информацию в указанном разряде, чем и достигается исправление однократной ошибки.

В остальном устройство функционирует также, как в основном режиме, при этом на выходах 18 и 19 формируются осведомительные сигналы о наличии ошибок, причем сигналы о нечетных ошибках могут игнорироваться, поскольку осуществляется исправление одиночных, следовательно, нечетных ошибок. В режим диагностики устройство переключается при занесении в регистр 7 кода с единичным уровнем на выходе 27, поступающим на вход коммутатора 12. До переключения в режим диагностики коммутатор 12 передает на информационные входы регистра 14 общий контрольный код с выходов регистра 12.

Необходимо, чтобы перед началом диагностики общий контрольный код был переписан в регистр 14, что осуществляется по заднему фронту сигнала на входе 22. Поэтому последней операцией перед переключением в режим диагностики должна быть операция считывания. Таким образом, после переключения в режим диагностики в регистре 14 находится контрольный код, а коммутатор 12 по сигналу на входе 27 подключает к входам регистра 14 выходы сумматора 3. После этого для проведения диагностики необходимо опросить в режиме считывания все ячейки памяти устройства в произвольной последовательности.

Для опроса каждой ячейки памяти на входы 15 подается ее адрес, а на вход 22 единичный сигнал чтения. По заданному адресу из накопителя 1 извлекается слово данных, из накопителя 2 — контрольный код, которые поступают на входы сумматора 13, на другие входы которого поступает текущее значение кода с выходов регистра 14. С выхода сумматора 13 сумма по модулю два этих кодов поступает через коммутатор 12 на входы регистра 14 и записывается в нем по заднему фронту сигнала на входе 22.

Если очередное считываемое слово данных или его контрольный код содержит обнаружимую ошибку, то блок 3 формирует ненулевой код признака ошибки, и на одном из выходов 18 и

19 появляются осведомительный сигнал о наличии ошибки. При этом из устройства считывается как слово данных по выходам 16, так и контрольный код с выходов 20. По окончании опроса всех ячеек памяти в регистре 14 будет сформирован общий код суммарного признака ошибки, который может быть считан с выходов

21, нулевое значение которого говорит о наличии в данных одной или группы ошибок. Таким образом, в проS 1 цессе опроса устройство выдает следус ь ющую диагностическую информацию: все искаженные слова данных с их контрольными кодами и суммарный код признака ошибки, что позволяет с высокой степенью достоверности исправлять широкий класс ошибок различной кратности. Исправление ошибок осуществляется программно и возлагается на соответствующую программу операционной системы 3ВМ, в которой используется предлагаемое устройство.

При наличии ошибки только в одном слове необходимо сложить по модулю два указанное слово и суммарный

1 код синдрома. Для полученного кода следует вычислить код синдрома по коду Хемминга, если он равен нулю, ошибка исправлена верно. При наличии ошибок в нескольких словах необходимо рассмотреть несколько вариантов

203364 б локализации ошибочных разрядов в словах данных и контрольных кодах.

При этом в первую очередь инвертируются разряды данных, на которые указывают одноименные единичные раз5 .ряды в суммарном коде синдрома. После каждого изменения в данном слове проверяется его синдром на равенство нулю. Таким образом, гоиск и исправление ошибок заключается в таком минимальном изменении ошибочных слов о данных, при котором синдромы всех этих слов и суммарный синдром зануляются, При работе устройства в режиме диагностики исправление ошибок блоком 5 блокируется единичным уровнем на инверсном входе элемента И 8, Начальная установка осуществляется записью нулевых кодов во все ячейки памяти, после чего подается сигнал на вход 23, обнуляющий регистр 11.

1203364

Составитель Т. Зайцева

Редактор Л. Зайцева Техред О.Ващишина Корректор И. Муска

Заказ 8407/44 Тираж 583 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4