Устройство для умножения

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11)

y1) 4 G 06 F 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3748511/24-24 (22) 06.06.84 (46) 07.0 1.86. Бюл. Р 1 (71) Ордена Ленина институт кибернетики им. В.М.Глушкова (72) В.А.Вышинский, Б.М.Тихонов и

Н.Б.Фесенко (53) 68 1.325(088.8) (56) Авторское свидетельство СССР

Р 817702, кл. G 06 F 7/52, 1978.

Самофалов К.Г., Корнейчук B.È. и

Тарасенко В.П. Цифровые 3ВМ.-Киев:

Вища школа, 1983, с.313-314,рис.5,24. (54) (57) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее 1 -разрядные сдвиговые регистры первого и второго сомножителей, две группы из 1 и (h-1) элементов И соответственно (H — - разрядность сомножителей), два полусумматора, (2 H -4) сумматоров и 2И-разрядный регистр результата, входы

2h-ro и (2И-1)-ro разрядов которого соединены соответственно с выходами переноса и суммы первого полусумматора, выход суммы второго полусумматора соединен с входом второго разряда 2и-разрядного регистра результата, вход первого разряда которого соединен с выходом первого элемента

И первой группы, первые входы элементов И которой соединены с выходами соответствующих разрядов П -разрядного регистра первого сомножителя, а вторые входы — с выходом )1-го разряда И -разрядного сдвигового регистра второго сомножителя, выходы (и -1) разрядов которого соединены с первыми входами соответствующих элементов И второй группы, выход второго элемента И первой группы соединен с первым входом второго полусумматора, выход переноса которого соединен с первым входом первого сумматора, выход переноса i --го сумматора соединен с первым входом (i +1) — го сумматора (.i =1,2,...,Н вЂ” 1), вторые входы первых (h -2) сумматоров соединены с выходами соответствующих элементов И первой группы, кроме первого и второго элементов И, а вход старшего разряда И -разрядного сдвигового регистра второго сомножителя соединен с входом второго сомножителя устройства, о т л и И ч а ю щ е е с я тем, что, с целью повышения быстродействия, вход первого сомножителя устройства соединен с входом младшего разряда И -раз- ( рядного сдвигового регистра первого сомножителя, выход младшего разряда которого соединен с вторыми входами ,элементов И второй группы, выход (h-1)-го элемента И которой соединен с первым входом первого полусумматора, второй вход которого соединен с выходом переноса (2h-4)-ro сумматора, выход переноса ) --го сумматора соединен с первым входом () +1)-го сумматора (j =h-1,...,2h-4),выходы элементов И второй группы, кроме последнего, соединены соответственно с вторыми входами J -х сумматоров, второй вход второго полусумматора соединен с выходом второго разряда

2h-разрядного регистра результата, выход К-го разряда которого (К =

=3,..., 2)1-2) соединены с третьим входом w-ro сумматора ()п=1,2,..., Ъ

2 -4) соответственно.

1203512

Изобретение .относится к вычислительной технике,в частности к устройствам умножения, и может быть использовано при построении арифметических устройств электронных вычислительных машин.

Цель изобретения — повьппение быстродействия.

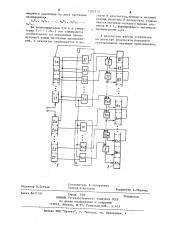

На чертеже изображена структур— ная схема устройства для умножения.

Устройство содержит и -разрядньпю сдвиговый регистр 1 первого сомножителя, И -разрядный сдвиговый ре гистр 2 второго сомножителя, группу из и элементов И 3, группу из (й-1) элементов И 4, два полусумматора 5 и 6, (2и-4) сумматоров 7, 2b-разрядный регистр 8 результата.

В данном устройстве реализуется умножение двух сомножителей путем последовательной их подачи на регистры 1 и 2 оцновременно (на регистры 1 — первый сомножитель со старших разрядов, на регистр 2 второй сомножитель с младших разрядов). При этом (темпе сдвига) на входах сумматоров формируются строки следующей таблицы (для четырех разрядов):

Ь„а а а а„ Ь Ь Ь, Ь а„а а . Ьэ Ь|, а

by а„а Ь, аg

Ь„ а1 а

Суммирование строк этой таблицы эквивалентно суммированию строк сле дующей таблицы: а а а а Ь„ а аэа < Ь а„а а а b3 а, а аэа b, Устройство работает следующим образом.

В исходном состоянии регистры

1 и 2 обнулены. На первый вход последовательно подается первый сомно житель А= а„,a,...,a>f начиная со старших разрядов, на второй вход одновременно подается второй сомножитель В = gbq,b,...,b j, начиная с младших разрядов.

В каждом такте одновременно с записью разряда сомножителей в регистре 1 происходит сдвиг информации на один разряд в сторону старших разрядов, а в регистре 2 — в сторону младших разрядов. Управляющий

ЗО

55 сигнал с выхода младшего разряда регистра 1 поступает на входы элементов И 4, управляющий сигнал с выхода старшего разряца регистра 2 — на входы элементов И 3 группы.

В результате на выходах элементов И 3 и 4 групп формируются в каждом такте различные по весу частичные произведения.

В .первом такте в младший разряд регистра 1 записывается значение старшего разряда а„ сомножителя А, в старший разряд регистра 2 — зна е". ние младшего разряда 6 сомножителя В.

На выходе элемента И 3. формируется первое частичное произведение а< Ъ„, На сумматоре 7,И -2 оно суммируется с промежуточным значением суммы частичных произведений и результат записывается в регистр 8 результата. Промежуточные значения суммы частичных произведений хранится на двойном регистре 8 резуль.тата.

Бо втором тахте в младший разряд регистра 1 записывается значение разряда а > сомножителя А, в старший разряд регистра 2 — значение разряда b „- „ сомножителя B. На выходе элем нтов И. 3. -1,3.п, 4м +1 формируются различные по весу частичн;. е произведения а Ь, 1, a>b, а Ь„. На сумматорах 7. и -3, 7. и -2, 7. и -1 они суммируются со значением промежуточной суммы частичных произведений, и результат записывается в регистр 8 результата.

В -м такте в младший разряд регистра 1 записывается значение разряда а; сомножителя А, в старший разряд регистра 2 — значение разряда Ь -сомножителя В. На выходе элементов И З.h -(i — 1), 4.п+(-1): формируются различные по весу частич ные произведения а1Ъ -(1), а Ь „ (ð а;Ь, (, 1, а Ь„(; >1...., а;Ь, На сумматорах 7.п — (i +1)-7. +

+(i +3) они суммируются соответственно со значениями промежуточной суммы частичных произведений, и резуль-, тат записывается в регистр 8 резуль- . тата.

В и-м такте в младший разряд регистра

1 записывается значение младшего разряда ар,. сомножителя А, в старший разряд регистра 2 — значение старшего разряда Ь сомножителя В. На выходе элементов И 3 и 4 групп фор1203512

Составитель Е.Захарченко

Техред И.Асталош

Корректор А.Обручар

Редактор В.Петраш

Подписное

Заказ 8417/51

Тираж 709

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП "Патент", r Ужгород, ул. Проектная, 4 мируются различные по весу частичные произведения а„Ь„, à b,, ..., а„Ь, а„Ь,..., а Ъ„.

На полусумматорах 5 и 6 и сумматорах 7.1 — 7.2н-3 они суммируются соответсвенно со значениями промежуточной суммы частичных произведений, и результат записывается в регистр 8 результата, причем в младший разряд регистра 8. результата записывается значение сигнала с выхода элемента И 3.1, формирующего частичное произведение а Ь .

В результате работы устройства на регистре результата находится окончательное значение произведения.