Цифро-частотный умножитель

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (Я) 4 С 06 F 7/68

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3762959/24-24 (22) 11.07.84 (46) 07.01.86. Бюп. М 1 (71) Львовский ордена Ленина политехнический институт им, Ленинского комсомола (72) В,Б.Дудыкевич, В.И.Отенко и З.М.Стрилецкий (53) 681.3(088.8) (56) Патент США Р 2910237, кл, Н 03 К 13/02, 1969.

Гутников В.С, Интегральная электроника в измерительных устройствах.

Л.: Энергия, 1980, с. 238-240. (54)(57) ЦИФРОЧАСТОТНЬЙ УМНОЖИТЕЛЬ, содержащий счетчик, группу элемен.тов И, первый элемент ИЛИ-НЕ и элемент НЕ, вход которого соединен с частотным входом цифрочастотного умножителя, а выход соединен с входом счетчика и с первыми входами элементов И группы, вторые входы элементов И группы подключены к соответствующим разрядам цифрового входа цифрочастотного умножителя, начиная с второго, третьи входы элементов И группы подключены к соответствующим инверсным выходам разрядов счетчика, прямой выход I --го разряда счетчика (i = 1,...,1ъ -1) подключен к (i+3)-м входам элементов И группы, начиная с (,+1)-ro, выходы элементов И группы подключены к входам первого элемента ИЛИ-НЕ, отличающийся тем, что, с целью повышения точности умножения, в него включены триггер, Р-триггер, первый и второй элементы И, второй, третий и четвертый элементы ИЛИ-НЕ, первый вход первого элемента И подключен к выходу второго элемента И и к первому входу второго элемента ИЛИ-НЕ, второй вход которого подключен к второму входу первого элемента И и к выходу третьего элемента ИЛИ-НЕ, третий вход второго элемента ИЛИ-НЕ подключен к выходу четвертого элемента ИЛИ-НЕ, а1 выход — к выходу цифрочастотного умножителя, первый вход третьего элемента ИЛИ-HE — к выходу первого элемента ИЛИ-НЕ и к счетному входу счетного триггера, прямой выход которого подключен к второму входу третьего элемента ИЛИ-НЕ, первый вход четвертого элемента ИЛИ-НЕ подключен к инверсному выходу j) -триггера, а второй вход — к частотному входу цифрочастотного умножителя и к тактовому входу Р -триггера, )) --вход которого подключен к выходу первого элемента И, первый вход второго элемента И подключен к инверсному выходу первого разряда счетчика, второй вход — к первому разряду цифро.вого входа цифрочастотного умножителя, а третий вход — к входу счетчика.

03522

1 12

Изобретение относится к. автоматике и вычислительной технике и может быть применено для умножения частоты импульсов в устройствах преобразования информации, в частности в цифровых функциональных преобразователях.

Цель изобретения — повышение точности умножения.

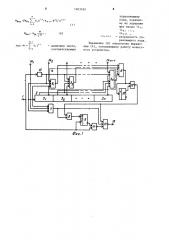

На фиг. 1 представлена структурная схема предлагаемого цифрочастотного умножителя; на фиг. 2 — временные диаграммы, поясняющие его работу.

Цифрочастотный умножитель (фиг. 1) содержит частотный вход 1, и-разрядный счетчик 2, реализованный на триггерах 3„, 3, ..., 3„, группу 4 элементов И 5„, 5@. ..., 5qi, элемент ИЛИ- НЕ 6, элемент И 7, элемент И 8, D -триггер 9, счетный триггер 10, элементы ИЛИ-НЕ 11н 12, элемент ИЛИ-НЕ 13, цифровой вход 14 (входы 14„, 14, ..., 14;,+„разрядов), элемент НЕ 15, выход 16. На фиг. 2 временные диаграммы обозначены порядковыми номерами элементов, »а выходах которых они сняты. Номера триггеров, диаграммы которых сняты на инверсных выходах, снабжены знаком инверсии, Временные диаграммы показаны для управляющего цифрово-. го кода,.поданного на входы 14, 14, ..., 14„, „,равного (29)„ (11101) .

Вход элемента НЕ 15 соединен с входом 1 умножителя, а выход— с входом счетчика 2 и с первыми входами элементов И 5< 5,..., 5>. Вторые входы элементов И 5<

5z, ..., 5q подключены соответст венно к входам 14, 14 . .. 14„+„, третьи входы элементов И 5„, 5, 5„ — соответственно к инверсным выходам триггеров 3, 3, Зь счетчика 2; прямой выход триггера 3„ подключен к четвертым входам элементов И 5, 5, ..., 5 „ прямой выход триггера 3z — к пятым входам элементов И 5з, 5, 5 и т.д., прямой выход триггера Зь„1 подключен к (+2)-му входу элемента И 5, а выходы элементов И 5,, 5, ..., 5 подключены к входам элемента ИЛИ-НЕ 6. Первый вход элемента И 8 подключен R выходу элемента И 7 и к первому входу элемента ИЛИ-HE 13, второй вход которого подключен к второму входу элемента И 8 и к выходу элемента ИЛИHE 12, третий вход элемента ИЛИНЕ 13 подключен к выходу элемента ИЛИ-НЕ 11, а выход — к -выходу 16 умножителя. Первый вход элемента ИЛИ-НЕ 12 подключен к выходу элемента ИЛИ-НЕ 6 и счетному входу счетного триггера 10, прямой выход которого подключен к второму входу элемента ИЛИ-НЕ llZ. Первый вход эле1О мента,ИЛИ-HE 11 подключен к инверсному выходу J) †.триггера 9, а второй вход — к входу 1 умножителя и к тактовому входу -триггера 9, вход которого подключен к выходу элемента И 8. Первый вход элемента И 7 подключен к инверсному выходу триггера 3„, второй вход— к входу 14, а третий вход — к входу счетчика 2.

Цифрочастотный умножитель работает следующим образом.

Перед началом работы триггеры 3, 3, ..., 3> счетчика 2 и триггер 9 установлены в нулевое состояние, 2д а триггер 10 — в единичное. Счетчик 2, реализованный на триггерах 3,, 3, ..., 3„ элементы И 5А, 5, ..., 5„, элемент ИЛИ-НЕ 6, входы 14>, 14з, ..., 14, и элемент HE 15 представляют собой двоичный умножи-, тель частоты, на вход 1 которого подаются отрицательные импульсы.

Сигнал на выходе i — ro элемента И 5 может быть равен единице только тогда, когда выполняются следующие условия: равен единице сигнал на входе 14< <, на инверсном выходе триггера 3 присутствует сигнал логической единицы, на прямых выходах триггеров 3;„, 3;, ...,, 3 при40 сутствует сигнал логическои единицы.

Выходные сигналы элементов И 5„, 5<, ..., 5 стробируются импульсами, подаваемыми с выхода элемента HE 15, Таким образом, при подаче на вход 1 умножителя отрицательного импульса, а на входы 14, 14»

14 „ потенциала логической единицы импульс появится на выходе того из элементов И 5„, 5, ..., 5», к одному из входов которого подключен инверсный выход триггера, переходящего по заднему фронту входного импульса умножителя иэ нулевого состояния в единичное. Если же подать на вход 1 умножителя серию из Мь . импульсов, то число импульсов М на зыходе (i -го элемента И 5

1203522 и (g) 1 Ьх

I zi

NSx быхов (Ь) 10

111х К; 1 или

NSX.Ê

М

Ььи1 (4) 45

МЬх К и+1

Вих (5) 5р И 7 ПОэтОму числО импульсОв Й „

Выходные импульсы элементов И 5<, 5, ..., 5> не сонпадают между собой во времени и суммируются эле ментом ИЛИ-НЕ 6. Поэтому при подаче на входы 14, 14, ..., 14„1 соответственно сигналов К„, к„» ..., К„ соответствующих различным разрядам двоичного числа К, так что ,К =Кн 2 +К„, 2ï-+ + ... +

+К 2 или зависимость между числом" импульСОВ N На ВХОДЕ И МЬМ,1 На ВЫХОДЕ

6х умножителя (элемента ИЛИ-HE 6) будет с учетом (1) следующей:.

NS„NS„Nьх

"ьих1="и 1 Кп-1 . -.+ s n

Учитывая (2), получаем выражение описывающее работу двоичного умножителя

Счетный триггер 10 и элемент ИЛИНЕ 12 предстанляют собой делитель частоты импульсов на дна со стробированием входными импульсами (им ПЛ-НЕ 6) . пульсами с выхода элемента У Я-Н ) .

ПОэтОму числО импульсОв М,1 на выходе элемента ИЛИ-НЕ 12 связано с числом импульсов йк„ на входе умножителя следующим соотношением:, Наличие уровня логического нуля на входе 14 вызывает появление

1 нулевого логического уровня на выходе элементов И 8 и 7, единичного логического уровня на инверсном выходе D --триггера 9 и, следовательно, уровня логического нуля на выходе элемента ИЛИ-kiE 11.

Таким образом, число импульсов на выходе 16 предлагаемого умножите15

40 ля при нулевом потенциале на входе 14„ определяется выражением (7).

При подаче на вход 141 сигнала К„,= 1, количество импульсов Nsb q на выходе элемента И 7 (аналогично сказанному об элементе И 5,) связано с количеством импульсов Мь„ на входе 1 умножителя выражением

Выходная импульсная последовательность элемента И 7 суммируется с выходной импульсной последователь-, ностью элемента ИЛИ-НЕ 12 с помощью элемента ИЛИ-НЕ 13. При совпадении импульсов этих последовательностей на выход элемента ИЛИ-HE 13 проходит импульс, а на выходе элемента И 8 появляется уровень логической единицы, который по заднему фронту отрицательного входного импульса умножителя записывается в

D-триггера. При этом элемент ИЛИНЕ ii открывается и пропускает на свой выход следующий импульс с входа 1 умножителя, который своим задним фронтом записывает в D --триггер 9 ноль, появившийся к этому времени на выходе элемента И 8. Следует отметить, что импульсы на выходе элемента ИЛИ-НЕ 11 не совпадают с импульсами выходных импульсных последовательностей элементов ИЛИ-НЕ 12 и И 7, так как они занимают свободные позиции, возникшие в результате деления выходной импульсной последовательности элемента ИЛИ-НЕ 6 и входной импульсной последовательности умножителя на два. Из этого видно, что два совпадающих во времени импульса выходных импульсных последовательностей элементов ИЛИ-НЕ 12 и И 7 вызынают появление на выходе элемента ИЛИ-НЕ 13 двух несовпадающих во времени импульсов.

Таким образом, происходит суммирование выходных импульсных последовательностей элементов ИЛИ-НЕ 12 и предлагаемого цифрочастотного умно;кителя при числе входных импульсов и х определяется с учетом (2), (5(и (6) выражением и

fag„„=(Ng„+K;2 f2 к„., i=1

t 203522 н

N»„-(ЧЬ| К; 2 ° К „„2 )/ 5 (8} где Pt = К2

I — двоичное число, соответствующе управляющему коду-, поданному на управляю щие входы 14, 14, 14 „,. = + — разрядность управляющего кода.

Выражение (8) аналогично выражению (4), описывающему работу известного устройства.

1203522

Редактор В.Петраш

Заказ 84 18/52 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Аи фМЮ

Юил г

Составитель В.Данчеев

Техред М.Надь Корректор С.Черни

Филиал ППП "Патент", г.ужгород, ул.Проектная, 4