Устройство для управления остановом электронной вычислительной машины

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„12О352 (5И 4 С 06 F 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬП М1 (21) 3705006/24-24 (22) 24.02.84 (46) 07.01.86. Бюл. Ф 1 (72) В.Н. Бучнев, Н,П. Васильев, В.P. Горовой и Е.И. Карпунин (53) 681.325(088.8) (56) Патент Японии Ф 53-41497, кл. С 06 F 11/00, опублик. 1978.

Авторское свидетельство СССР

В 868758, кл. G 06 F 9/00, 1979. (54) (57) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ

ОСТАНОВОМ ЗЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ, содержащее пять схем сравнения, регистр, первый счетчик и первый триггер, причем информационный вход и синхровход регистра подключены соответственно к входу признаков и входу синхронизации устройства, входы фиксированной адресной информации устройства с первого по третий подключены к первым входам схем сравнения соответственно с первой по третью, вторые входы которых соединены с входом текущего адреса устройства, информационный вход и вход количества сравнений которого подключены к первым входам соответственно четвертой и пятой схем сравнения, вторые входы которых подключены соответственно к выходу регистра и выходу счетчика, вход установки в "0" которого подключен к выходу первого триггера, выход пятой схемы сравнения подключен к выходу сигнала остайова устройства, о т— л и ч а ю щ е е с я тем, что, с целью повышения достоверности управления остановом электронной вычислительной машины, в него введены второй и третий триггер, элемент задержки, второй счетчик, ком-. мутатор и элемент И-НЕ, причем выходы первого и второго разрядов информационного выхода коммутатора подключены соответственно к входам установки в "1" и установки в "0" первого триггера, входы с первого по пятый элемента И-НЕ подключены соответственно к выходу. третьей схемы сравнения, выходу второго триггера, выходу третьего триггера, выходу четвертой схемы сравнения и выходу третьего разряда информационного выхода коммутатора, входы разрядов с первого по третий первого информационного входа которого под-. ключены к выходам схем сравнения соот ветственно с первой по третью, второй информационный вход коммутатора подключен к входу логической единицы, устройства, выходы первой и второй схем сравнения подключены соответственно к входу установки в " 1" треть го триггера и к входу установки в

"0 второго триггера, информационный вход и синхровход которого подключены соответственно к выходу третьего триггера и к выходу элемента задержки, вход которого соединен с входом установки в "0" третьего триггера и подключен к выходу второго счетчика, счетный и разрешающий входы которого подключены соответственно к входу синхронизации устройства и к выходу третьего триггера, выход элемента И-НЕ подключен к счетному входу первого счетчика, управляющий вход коммутатора подключен к входу режима работы устройства.

1 2035 .""

1Î

Изобретение относится к вычислительной технике и может быть применено для управления исполнением программ в цифровой вычиспительной машине (ЦВМ).

Цель изобретения — повышение достоверности управления остановом электронной вычислительной машины.

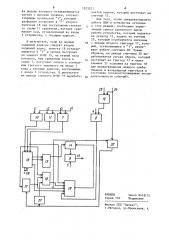

На чертеже изображена принципиальная схема устройства.

Устройство содержит первый 1, второй 2 и третий 3 входы фиксированной адресной информации, информационный вход 4, вход 5 количества сравнений, вход 6 текущей адресной информации, схемы 7-11 сравнения, регистр 12, триггер 13, счетчик 14, выход 15 сигнала останова, коммутатор 16, триггеры 17 и 18, элемент

И-HE 19, второй счетчик 20, элемент

21 задержки, вход 22 режима работы устройства, вход 23 признаков устройства, вход 24 синхроимпульсов устройства.

Устройство работает следующим образом.

При наличии на входе 22 устройства высокого уровня напряжения (+5 В) устройство работает следующим образом: на входе 1 устройства установлен начальный адрес, на входе

2 устройства — конечный адрес участка программы, на котором необходимо остановить работу ЦВМ. На вход 6 устройства поступает значение текущего адреса: программ. При сравнении начального адреса с текущим на выходе схемы 10 сравнения появляется сигнал сравнения, который через коммутатор 16 (который открыт в этом режиме) воздействует на первый единичный вход триггера 13, и триггер переходит в состояние "1", что обеспечивает снятие со счетчика 14 сигнала обнуления.

При сравнении конечного адреса с текущим появляется сигнал на выходе пятой схемы 11 сравнения, который воздействует на второй вход триггера 13 и триггер переходит в состояние "0", при этом нулевой выход триггера 13 обнуляет счетчик

14. Таким образом, работа счетчика

i4 разрешена только в диапазоне текущих адресов программ от заданного начального до заданного конечного адресов.

Если внутри указанного диапазона происходит сравнение текущего адреса с адресом останова, который установлен на входе 3 устройства, на выходе первой схемы 7 сравнения появляется сигнал, который через коммутатор 16 поступает на вход элемента И-НЕ 19, с выхода которого сигнал поступает на счетный вход счетчика 14, состояние которого увеличивается на " 1", если произойдет сравнение в то же самое время комбинации входных сигналов с регистра 12 с кодом, установленным на выходе 4 устройства, причем на выходе второй схемы 8 сравнения появляется сиги ал, который также воздействует на элемент И-НЕ 19.

На регистр 12 могут подаваться про— извольные сигналы, которые имеют различную временную привязку, внутри такта работы ЦВМ эти сигналы запоминаются в регистре, в конце такта информация с регистра 12 сравнивается с информацией, поступающей с вхоца 4 устройства, после чего регистр обнуляется.

На входе 5 устройства установлен в течение интервала. от начального до конечного адресов код, который соответствует текущему числу сравс пений всех входных сигналов.

Б то время, как содержимое счетчика 14 станет равным коду, установленному на входе 5 устройства, на выходе третьей схемы 9 сравнения появляется сигнал 15 останова. Если счетчик 14 не достигает числа, равного коду, установленному на входе

5 устройства, и если происходит сравнение текущего адреса с конечным адресом в пятой схеме 11 сравнения, то триггер 13 переходит в нулевое состояние и тем самым обнуляет счетчик 14.

При наличии на управляющем входе коммутатора 16 низкого уровня на выходах устанавливаются высокие уровни, два из которых переводят первый триггер 13 в двухстабильное состояние с высоким уровнем на выходе, который разрешает работу счетчика

14, третий подается на элемент

И-НЕ 19, разрешая прохождение сигналов по другим входам. На входы

1-3 в этом режиме останова подают последовательности трех а„,ресов. Значение первого адреса после сравнения в схеме 10 сравнения с текущим адресом, поступающим с входа 6 устройства, запоминается в триггере 17, Заказ 8418/52

9 Подписное на выходе которого устанавливается сигнал с высоким уровнем, соответствующим логической "1", который разрешает установку в " 1" второго триггера 18 при поступлении сигнала со схемы 11 сравнения, которая сравнивает код, установленный на входе

2 устройства, с текущим адресом.

В результате, если за первым заданным адресом следует второй заданный адрес, триггер 18 устанавливается в " 1" и сигнал поступает на элемент И-НЕ 19, на первый вход которого, при сравнении кодов в схеме 7, поступает сигнал о совпадении третьего заданного на входе 3 кода с текущим адресом, поступающим с входа б устройства„ В результате на выходе элемента И-НЕ 19 вырабаты203523 4 вается сигнал, который поступает на счетчик 13.

Для того, чтобы синхронизировать работу ЦВМ и устройства останова в этом режиме, необходимо управляющий сигнал временного цикла работы устройства, который подается на регистр 12, подать на счетчик

20, который стробируется сигналом

10 с выхода второго триггера 17, который, установившись в "1", paspeшает работу счетчика 20. Таким образом, на выходе счетчика 20 вырабатывается сигнал сброса, который

15 поступает на триггер 17 и через элемент 21 задержки на триггер 18 для предотвращения ложного срабатывания и возвращения триггеров в состояние готовности(ожидания последовательности событий).

IIIIII Патент", r.Ужгород, ул.Проектная, 4