Устройство для контроля микропрограммного блока управления

Иллюстрации

Показать всеРеферат

союз советских социмистичксиих

Республин

С 06 Р 9/22, 1!/16 (21) 3754968/24-24 (22) 14.06.84 (46) 07.01.86. Бюл. № 1 (72) А.А. Баранник, В.Д. Злодеев и В.И. Писаренко (53) 681.3(088.8) (56) Авторское свидетельство СССР № 391563, кл. С 06 F 11/16, 1969.

Авторское свидетельство СССР № 940159, кл. С 06 F 9/22, 1980. (54)(57) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

МИКРОПРОГРАММНОГО БЛОКА УПРАВЛЕНИЯ, содержащее два элемента И, два элемента ИЛИ, первый регистр, первую группу элементов И, первую схему сравнения, причем вход синхронизации устройства соединен с первым входом первого элемента И, входом первого элемента задержки и первыми входами элементов И первой группы, вторые входы которых соединены с соответствующими адресными выходами контролируемого микропрограммного блока управления и с первой группой информационных входов первои схемы сравнения, выходы элементов И первой группы соединены с входами первого регистра, выходы которого соединены с второй группой информационных входов первой схемы сравнения, вход разрешения которой соединен с выходом первого элемента задержки с первым входом второго элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход обнуления которого соединен с выходом первого элемента И и входом пуска контролируемого микропрограммного блока управле„„ЯУ„„1203526 ния, группа. выходов микроопераций которого соединена с входами первого элемента ИЛИ, выход которого соединен с входом установки первого триггера, выход второго элемента И соединен с первым входам второго элемента ИЛИ, второй вход которого соединен с выходом созпадения первой схемы сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно дополнительно содержит третий элемент И, второй элемент задержки, вторую группу элеJ ментов И, второй и третий регистры, вторую схему сравнения, второй и 3 третий триггеры, причем первые входы элементов И второй группы соеди1нены с входом синхронизации устрой.ства, вторые входы элементов И второй группы соединены с соответствующими выходами микроопераций группы контролируемого микропрограммного, блока управления и первой группой информационных входов второй схемы сравнения, вторая группа информационных входов которой соединена с группой выходов элементов И второй группы, вход второго элемента задержки соединен с выходом первого элемента задержки, выход второго элемента задержки соединен с входом разрешения второй схемы сравнения и вторым входом второго элемента И, выход которого является выходом отказа устройства, выход второй схемы сравнения соединен с входом .установки второго триггера и третьим входом второго элемента ИЛИ, выход которого соединен с входом разрешения

1 203 i 2-,<. третье го регистра, инфо рмацион ные входы которого соединены с соответствующими адресными выходами контролируемого микропрограммного блока управления, информационные выходы третьего регистра подключены к шике индикации адреса, входы обнуления второго и третьего триггеров соединены с входом синхронизации устройства, прямой выход второго триггера соединен с выходом нормальной работы устройства, инверсный

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации средств контроля управляющих автома.тов, примек емых в цифровых вы—

Счислительных машинах и различных устройствах цифровой автоматики.

Пель изобретения — повышение достоверности контроля.

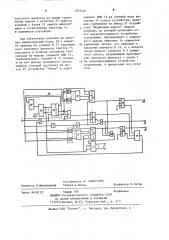

На чертеже приведена фучкциокяль — 1О ная схема предлагаемого устройства.

В состав устройства входят сикхрокизирующий вход 1, вход 2 качалькой установки, элемент И 3, элемент

ИЛИ 4, элементы 5 и 6 задержки, гр п-15 пы элементов И 7 и 8, реглстры 9 и 10, регистр 11 адреса устройства., схемы 12 и 13 сравнения, триггеры

14 — 16, элемент И 17. элемент

ИЛИ 18, элемент И 19> дешифратор 20, 2С вход 21 установки начального адреса, регистр 22 адреса микропрограммного автомата, блок 23 памяти мккрокоманд, выходы 24-26 правильной работы, отказа и зацикливания соответ- 15 ственно и выход 27 индикации адреса (цепи синхронизации работы буферных регистров 9 и 10 и регистра 11 адреса не показаны), блок микропрограмм. 3l;"

Устройство 28 управления позволяет контролировать ошибки программирования и перфорации типа "тупик", приводящие к зацикливацию программы на каком-либо адресе, и ошибочного занесения в блок памяти микропрограмм в соседние ячейки одинаковых команд. Такие ошибки обнаруживаются выход второго триггера соединен с первым входом третьего элемента И, второй вход которого соединен с прямым выходом первого триггера, вход установки третьего триггера соединен, с выходом первой схемы сравнения, прямой выход третьего триггера соединен с выходом зацикливания устройства,инверскый выход третьего триггера соединен с третьим входом третьего элемента И, выход которого соединен с вторым входом первого элементаИ.. при сравнении адресных частей предыдущей и последующей микрокоманд и сравнении кодов комякд. В устройстве предусмотрены также индикация адреса, на котором произошло заклик квак не, -равнение кодов соседних команд и контроль физического отказа элементов ка выходе микроопераций блока памяти.

Устройство работает следующим образом. !

1еред началом работы схема приводится в исходное состояние путем подачи кя входы 2 начальной установ«и единичного импульса, и триггеры

15 и 16 устанавливаются в нулевое состояние, а триггер 14 — в единичное. В результате этого с выходя

".ëåìåíra И 19 единичный сигнал подается на вход элемента И 3 и разрешает прохождение тактового импульса с входа 1 на выход элемента И 3.

Подача импульса на вход 2 производится также после останова микропрограммного устройства по сигналам ошибки для возобновления работы устройства контроля. Ход программы в устройстве контролируется следующим образом. Очередной тактовьпл импульс поступает через синхрокизирующий вход 1 устройства на входы элементов И 7 и 8 первой и второй групп и разрешает запись адреса микрокоманды выхода регистра 22 адреса блока микропрограммного управления на регистр 9 и запись кода команды с выхода микроопераций блока 23 памяти микроко2035

30

55

3 1 манд на регистр 10. Этот же импульс, поступивший через элемент И 3 на блок 23 памяти микрокоманд, вызывает считывание очередной микрокоманды. Затем на регистре 22 с помощью дешифратора 20 устанавливается адрес очередной микрокоманды, и тактовый импульс, вызвавший считывание микрокоманды через элемент 5 задержг ки, поступает на схему 12 сравнения и через элемент 6 задержки на схему 13 сравнения (для разрешения сравнения) . Происходит сравнение адреса предыдущей микрокоманды, записанного на регистре 9, и адреса очередной микрокоманды, поступающего на схему 12 сравнения с выхода регистра 22 адреса (в период между тактовыми импульсамк, когда отсутствуют разрешение записи на регистры 9 и 10 через элементы 7 и 8).

Одновременно адрес очередной мккро— команды заносится в регистр 11 адреса устройства..При равенстве указанных адресов схема 12 сравнения формирует сигнал ошибки, который поступает на единичный вход триггера 16 и на вход элемента ИЛИ 18.

С единичного вьгхода триггера 16 формируется скгнал Зацикливание на выход 26 устройства, с нулевого выхода триггера снимается единичный сигнал, в результате чего закрывается элемент И 19, и с второго входа элемента И 3 снимается сигнал, разрешающий прохождение тактового импульса с входа 1 на считывание микрокоманд — происходит останов микропрограммного устройства управления. Одновременно сигнал со схемы

12 сравнения через элемент ИЛИ 18 поступает на управляющий вход регистр

11 адреса устройства, вызывая считывание адреса, по которому произошло зацикливание, на выход 27 устройства "Индикация адреса". Аналогично происходит сравнение кода предыдущей и очередной команд на схеме 13 сравнения: по окончании считывания очередной микрокоманды с блока 23 памяти микрокоманд на его выходе устанавливается код очередной команды и происходит сравнение кода предыдущей команды, записанной на регистре 10, и кода очередной команды, поступающей на схему 13 сравнения с выхода микроопераций . блока 23 памяти микрокоманд. При равенстве указанных кодов команд 6 4 схема 13 сравнечия формирует сигнал ошибки, который поступает на единичный вход триггера 15 и на вход второго элемента ИЛИ 18. С единичного выхода триггера 15 формируется сигнал

"Коман а" на выход 24 устройства, с нулевого выхода триггера снимается единичный сигнал, в результате чего закрывается элемент И 19 и с второго входа первого элемента И 3 сн кмается сигнал, разрешающий прохождение тактового импульса с входа 1 на микропрограммное устройство управления. Происходит его останов, как и в первом случае при зацикли— вании программы. Одновременно сигнал со схемы 13 сравнения через вход второго элемента ИЛИ 18 посту-. пает на вход считывания регистра 11 адреса устройства, вызывая считывание адреса, на котором произошло сравнение кодов команд, на выход

27 устройства "Индикация адреса".

Элемент 5 задержки должен обеспе-.ить задержку тактового импульса на время считывания адреса с регистра 22 адреса микропрограммного автомата, а элемент 6 задержки обеспечивает задержку импульса с элемента 5 на время считывания кода команды блока микроопераций блока 23 памяти микрокоманд и установление триггера 14 в единичное состоян ие, Контроль ошибок, вызванных физическими отказамк элементов устройства, заключается в проверке наличия сигналов микроопераций в операционной часги микрокоманды контролируемого устройства. При отсутствии сигналов на выходах микрооперацик устройство формирует скг нал Ошибки.

В устройстве микропрограммного управления обнаруживается отсутствие сигналоь мккроопераций на выходе блока 23 памяти следующим образом. Каждый тактовый импульс через элемент И 3 устанавливает первый триггер 1<4 в нулевое состояние.

Сигналы команд операционной части мккрокоманды через элемент ИЛИ 4 устанавливают триггер 14 в единичное состояние и запрещают прохождение тактового импульса, задержанного элементами 5 и 6 задержки, через элемент И 17 для формирования сигнала ошибкк. Элементы 5 к 6 задержки должны обеспечить задержку

1203 26

Составитель А. Сиротская

Редактор О.Юрковецкая Техред А.Бойко

Корректор Л, Патай

Заказ 8418/52

Тираж 709

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035,,Москва, Ж-35, Раушская наб,, д. 4/5

Подписное

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 тактового импульса на время считы вания адреса с регистра 22 адреса, команды с блока 23 памяти микрокоманд и установление триггера 14 в единичное состояние.

При отсутствии сигналов на выходах микроопераций блока 23 к моменту прихода на элемент И 17 эадер>канного тактового импульса триггер 14 находится в нулевом состоянии (нет сигнала на выходе элемента ИЛИ 4), следовательно, элемент И 17 открыт„ и на его выходе появляется сигнал ошибки, который поступает на выход 25 устройства "Отказ" и через элемент ИЛИ 18 на счетный вход регистра 11 адреса устройства, вызывая считывание на выход 27 устрой-,. ства Индикация адреса" адреса команды, на которой произошел отказ микропрограммного устройства управления. Одновременно с единичного выхода триггера 14 снимается

10 единичный сигнал„ что приводит к закрытию элемента И 19, и с второго входа первого элемента И 3 снимается сигнал, разрешающий прохождение тактового импульса с входа 1

15 на микропрограммное устройство управления, и происходит его останов.