Устройство для распознавания образов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) (11) ш G 06 К 9/36

1 !

/

/ (ЪСУДАРСТВЕККЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ.

К ASTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3760196/24-24 (22) 05.07.84 (46) 07 ° 01.86. Бюл. № 1 (71) Московский институт электронной техники (72) В.А. Абрамов, В.С. Дубровин, В.С. Звездин, Э.З. Немировский и В.Ф. Шаньгин (53) 681.327.12(088.8) (56) Патент Японии N 56-15546, кл. G 06 К 9/62, опублик. 1981.

Заявка Великобритании ¹ 1310265, кл. G 4 R, опублик. 1973. (54)(57) 1. УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ОБРАЗОВ, содержащее вычислительные блоки, одни входы которых являются первым входом устройства, другие подключены к выходам соответствующих регистров первой и второй групп и первого регистра, а выходы соединены с одними входами соответствующих регистров второй группы, другиЕ входы котовых являются вторым входом устройства, при этом входы регистров первой группы являются третьим входом устройства, вход первого регистра первой группы регистров является четвертым входом устройства, а входы первого регистра являются пятым и шестым входами устройства, о т л и ч а ю щ е е с я тем, что, с целью повьппения надеж- ности распознавания, оно содержит второй регистр, вход которого является седьмым входом устройства,, а выход подключен к первому регистру второй группы регистров, и первый коммутатор, входы которого соединены с выходами регистров второй группы, а выход является выходом устройства, при этом регистры первой и второй групп соответственно последовательно соединены между собой, выход каждого регистра соединен с входом предыдущего, а выход последнего регистра в каждой группе подключен к входу первого.

1203554

2. Устройство по п.1, о т л и— ч а ю щ е е с я тем, что вычисли„тельные блоки содержат группу коммутаторов, одни входы которых явпяются первым, вторым и третьим входами блоков, а выходы подключены к одним входам второго коммутатора, сумматор, один вход которого соединен с выходом одного коммутатора группы, а выход подключен к другому входу второго коммутатора, выход которого соединен с входами коммутаторов группы, первый инвертор, вход которого соединен с выходом другого

I коммутатора группы, а выход поцключен к одному входу третьего коммута— тора, другой вход которого соединен с выходом соответствующего коммутатора группы, а выход подключен к другому входу сумматора, выход котоИзобретение относится к автоматике и вычислительной технике и может быть использовано в быстродействующих системах распознавания изображений и речи.

Цель изобретения — повышение надежности распознавания.

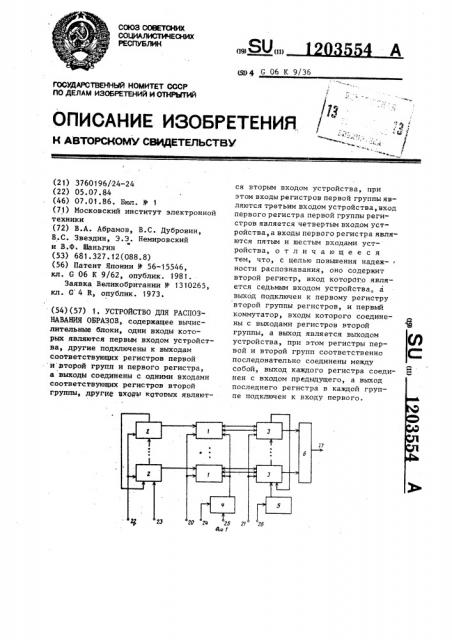

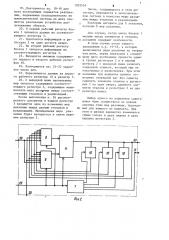

На фиг. 1 представлена блоксхема предлагаемого устройства; на фиг. 2 и 3 — примеры конкретного конструктивного выполнения вычислительного блока.

Устройство содержит вычислительные блоки 1 первую 2 и вторую 3 группы регистров, первый 4 и второй

5 регистры и первый коммутатор 6, выполненный в виде мультиплексора (фиг. 1).

При этом вычислительные блоки содержат (фиг. 2) первый дешифратор

7, группу коммутаторов 8 и 9, выполненных в виде мультиплексоров, третью группу 10 регистров и арифметический блок 11, включающий (фиг. 3) сумматор 12, второй коммутатор 13 и третий коммутатор 14, выполненные в виде мультиплексоров, второй 15 и третий 16 дешифраторы, первый 17 и второй 18 инверторы и элементы 19 задержки, рого соединен с входом второго инвертора, подключенного к четвертому входу второго коммутатора, первый дешифратор, входы которого являются вторым входом блока, а выходы соединены с одними входами регистров третьей группы, другие входы которых подключены к выходу второго коммутатора, а выходы соединены с входами соответствующих коммутаторов группы, второй дешифратор, входы которого являются вторым входом блока, а выходы подключены к другим входам третьего коммутатора, и элементы задержки, входы которых являются вторым входом блока, а выходы подключены к третьему дешифратору, один вход которого соединен с выходом сумматора, а выходы подключены к другим входам второго коммутатора, Устройство содержит первый 20, второй 21, третий 22, четвертый 23, пятый 24, шестой 25 и седьмой 26 входы устройства, и выход 27

5 (фиг. 1), первый 28, второй 29 и третий входы вычислительного блока и выходы 30 и 31 (фиг. 2).

Устройство для распознавания образцов предназначено для работы в составе вычислительной системы в качестве периферийного вычислителя и подключается к вычислительной системе через свои шины данных и управления. Устройство работает с внешней синхронизацией под управлением центрального процессора вычислительной системы. На входные шины устройства подаются соответствующим образом синхронизованные потоки данных с элементами эталона и реализации и определяемые алгоритмом обработки комбинации управляющих сигналов.

Устройство распознавания образов в соответствии с комбинациями управляющих сигналов осуществляет коммутацию входов-выходов всех своих внутренних блоков и в результате выполнения алгоритма передает в вычис30 лительную систему через выходную з 1203554 шину меру различия между очередным эталоном и реализацией.

В устройстве, содержащем M вычислительных блоков 1, одновременно могут обрабатываться только М элементов эталона.

Если в эталоне число элементов больше количества блоков 1, то в алгоритме появятся дополнительные шаги.

Рассмотрим вначале работу устройства, когда число блоков 1 больше или равно числу элементов в эталоне. Число элементов в реализации не ограничено и может быть любым.

Тогда для вычисления меры различия между неизвестной реализацией и эталонным образом устройство распознавания выполняет следующую последовательность команд, определяемых последовательностью комбинаций управляющих сигналов, подаваемых на шину управления устройства распознавания образов из вычислительной системы.

Данная последовательность управляющих сигналов может поступать из внешней вычислительной системы, где может, храниться в постоянном запоминающем устройстве. Из постоянного запоминающего устройства на каждый синхроимпульс выбирается очередная комбинация управляющих сигналов.

Ниже приведены пункты алгоритма работы устройства распознавания образов.

1. С шины элементов эталонов в первый регистр 2 записывается соответствующий элемент эталона. . 2. В регистрах 2 через сдвиговые входы-выходы данные сдвигаются на один регистр вверх. Для этого подается комбинация управляющих сигналов, по которой в мультиплексорах регистров 2 выход коммутируется со сдвиговым входом, и подаются сигналы разрешения записи в первый регистр 2 и разрешение записи во второй регистр 2.

3. Пункты 1 и 2 повторяются заданное число раз для последующих элементов эталонов так, что в результате в первом регистре 2 хранится первый элемент эталона, а в последнем регистре 2 хранится последний элемент эталона.

4. В регистре 5 устанавливается максимально возможное большое число

30

5. Аналогично и. l в регистр 4 с шины 25 "-агисывается первьп элемент реализации.

6. В каждом блоке 1 в первые рабочие регистры 10 пересылаются элементы эталона из соответствующего регистра 2. Для этого на мультиплексоры

8 в блоках 1 подается управляющий код, по которому выход мультиплексора 8 коммутируется с первым входом данных. В арифметические блоки

11 всех блоков 1 подается код, соответствующий заданной функции, а затем в дешифратор 7 подается управляющий код, по которому на выходе детифратора 7 возбуждается линия разрешения записи в первый рабочий регистр 10.

7. Аналогичными управляющими сигналами во вторые рабочие регистры

10 всех блоков 1 пересылается элемент реализации из регистра 4.

8. В арифметический блок 11 каждого блока 1 подается команда вычисления модуля разности содержимого первого и второго рабочих регистров с пересылкой результата в первый рабочий регистр.

9. Данные из первых рабочих регистров пересылаются в соответствую щие регистры 3 накопленных мер.

10. В регистр 4 записывается с шины элементов реализации следующий элемент реализации.

11. Повторяются пп. 6-8.

12. Во вторые рабочие регистры

II0 во всех блоках 1 пересылаются данные из соответствующих регистров 3.

13. В регистрах 3 накопленных мер данные сдвигаются на один регистр вверх. В первый регистр 3 накопленных мер записываются данные из регистра 5 константы.

14. В третьи рабочие регистры

10 всех блоков 1 пересылаются данные из соответствующих регистров

3 накопленных мер.

15. Находится минимум содержимо- го второго и третьего рабочих регистров 10 блоков 1. Результат помещается во второй рабочий регистр.

16. Повторяются пп. 13-15.

) 17. Находится сумма первого и второго рабочих регистров 10, 18. Результат, находящийся во втором рабочем регистре 10, пересылается в соответствующий регистр 3

1203554

19.,Повторяются пп. 10-18 для

Ъ всех последующих элементов реализа-. ции, подаваемых последовательно из

:вычислительной системы на шину элементов реализации устройства распознавания образов.

20 ° В первый рабочий регистр блоков 1 читаются данные из соответствующего регистра 3.

21. Сдвигается информация в регистрах 3 на один регистр вверх.

22. Во второй рабочий регистр блоков 1 читается информация из соответствующего регистра 3.

23. Находится минимум содержимо(х о первого и второго рабочих регистров 10.

24. Повторяются пп. 21-23 заданное число раз.

25. Пересылаются данные из первого рабочего регистра 10 в регистр 3. .26. С выходной шины накопленных мер читается содержимое соответствующего регистра 3, содержащее минимальную меру различия между соответствующим эталоном и реализацией.

После выполнения п. 26 рассмотренного алгоритма в каждом регистре

3 находится одна из возможных мер различия между данным эталоном и реализацией. Минимальная мера раз.личия будет находиться в самом верхнем регистре 3.

Число, содержащееся в этом регистре, передается в вычислительную систему в качестве меры различия между эталоном и реализацией.

Повторив алгоритм для К эталонов, получим К мер различия.

Для случая, когда число блоков 1 меньше числа элементов в эталоне, 10 алгоритм содержит особенности.

В этом случае после каждого выполнения п.п. 10-18, в которых вычисляются меры различия на очередном шаге, перед переходом к следующему шагу необходимо провести сдвиг в группе регистров 2 и в первый регистр 2 с выходной шины записать очередной элемент, который еще не участвовал в вычислениях. При этом

20 возможны три варианта сдвига: повторить очередной шаг без сдвига; сдвинуть элементы эталона в регистрах 2 на один вверх; сдвинуть элементы эталона в регистрах 2 на два регистра вверх.

Выбор одного из вариантов сдвига может быть осуществлен на основе анализа сумм мер различия, получаеЗО мых для каждого из варианта. При этом в разных вариантах изменяются суммы только в двух нижних и двух верхних регистрах 2.

1203554

Составитель А. Романов

Редактор Г. Волкова Техред О.Ващишина Корректор И. Эрдейи

Заказ 8419/53 Тираж 709 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4